实例介绍

【实例简介】FPGA实现的TOE码逻辑,完整的逻辑设计

这是 FPGA 厂商提供的标准 IP,支持 1G/10G 自适应模式, 可选 32 位低时

延 10 G 以太网 MAC 或 64 位以太网 MAC,支持 10G 数据速率

• 选择 PHY 层的外部 XGMII 或内部 FPGA 接口

• 在客户端发送及接收接口上支持 AXI4-Stream 协议

• 支持缺损空闲计数以实现最大数据吞吐量;在各种条件下保持最小 IFG

并提供线路速率性能

• 针对所有设备支持包含带内 FCS 和不含带内 FCS 的缺损空闲计数

• 全面的统计收集

• 支持双向 802.3 和 802.1Qbb(基于优先级)流量控制

• 提供 MDIO STA 主接口以管理 PHY 层

• 支持 VLAN、巨型帧和 WAN 模式

• 定制前导模式

• 独立 TX 及 RX 最大传输单元 (MTU) 帧长度

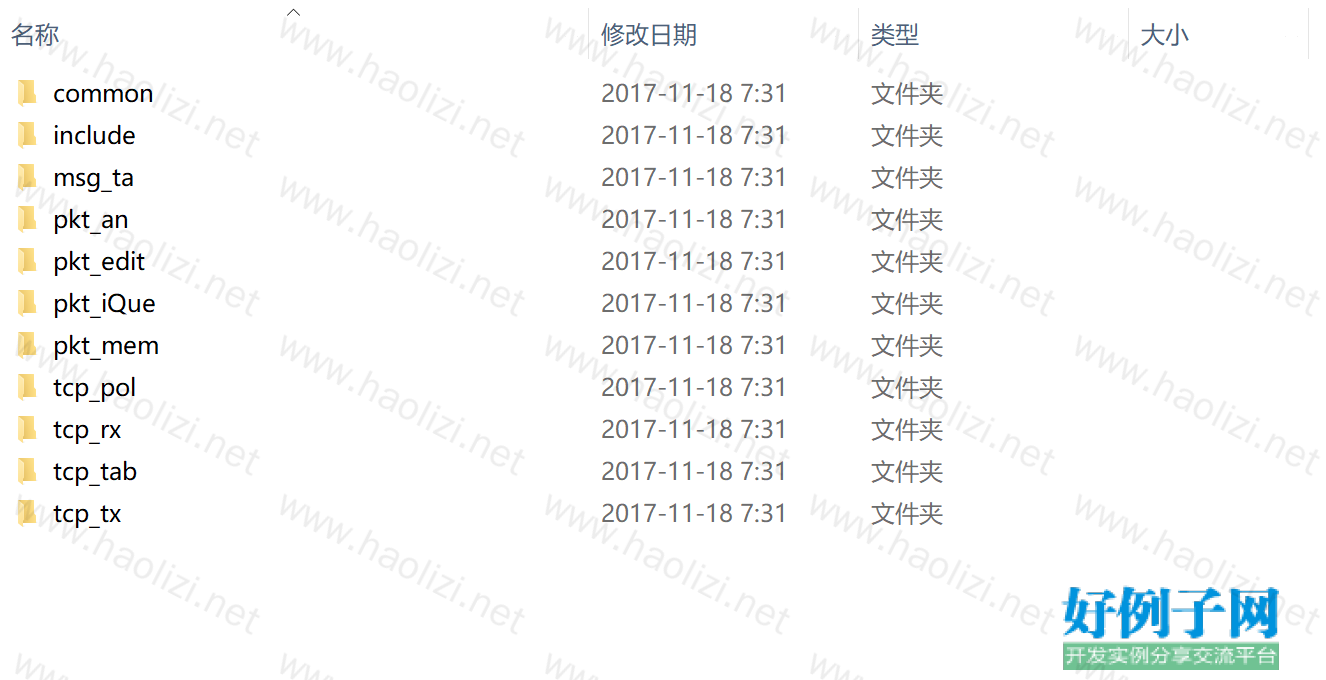

【实例截图】

【核心代码】

.

├── FPGA实现的TOE码逻辑,完整的逻辑设计_TOE-verilog.rar

└── TOE-verilog

├── common

│ ├── async_bfifo.v

│ ├── async_bfifo_reg.v

│ ├── ctrl_dly.v

│ ├── data_dly.v

│ ├── fifo_sig_pro.v

│ ├── nic_intf.sv

│ ├── nic_top_define.sv

│ ├── rr_arb.v

│ ├── toe_top_define.sv

│ └── xilinx_ram_lib.v

├── include

│ ├── common_define_value.v

│ └── pkt_des_unpack.v

├── msg_ta

│ ├── cell_sch.v

│ ├── data_demux.v

│ ├── fc_sch.v

│ ├── fc_wr.v

│ ├── msg_ta.v

│ └── pa_tx.v

├── pkt_an

│ ├── cpkt_unf.v

│ ├── pkt_an.sv

│ ├── pkt_des_unpack.v

│ └── pkt_proc.sv

├── pkt_edit

│ ├── ec_gen.sv

│ ├── mfifo_sync_wpkt.v

│ ├── pkt_edit.v

│ ├── pre_edit.v

│ └── rx_edit.v

├── pkt_iQue

│ ├── cell_que.v

│ ├── data_demux.v

│ ├── pkt_iQue.v

│ └── reg_que_fifo.v

├── pkt_mem

│ ├── crc_gen.v

│ ├── crc_pre_gen.v

│ ├── fptr_fifo_init.v

│ ├── pkt_mem.v

│ ├── pkt_mem_rd.v

│ └── pkt_mem_wr.v

├── tcp_pol

│ ├── pkt_tbl_pol.dat

│ └── toe_pol.v

├── tcp_rx

│ ├── common_define_value.v

│ ├── cpkt_fifo_mux.v

│ ├── cpkt_mix.v

│ ├── cpkt_mux.v

│ ├── fix_cpkt_unf.v

│ ├── pkt_des_unpack.v

│ ├── sync_table_fifo.v

│ ├── tcp_rx.sv

│ ├── tcp_rx_tab_pre_req.sv

│ ├── tcp_rx_tab_req.v

│ ├── tcp_rx_table_act.sv

│ ├── tcp_rx_tcpkt_mix.sv

│ └── work_cpkt_ctrl.sv

├── tcp_tab

│ └── toe_tab.v

└── tcp_tx

├── tcp_tx.v

├── tcp_tx_tab_act.v

└── tcp_tx_tab_req.v

12 directories, 57 files

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论