实例介绍

【实例截图】

【核心代码】

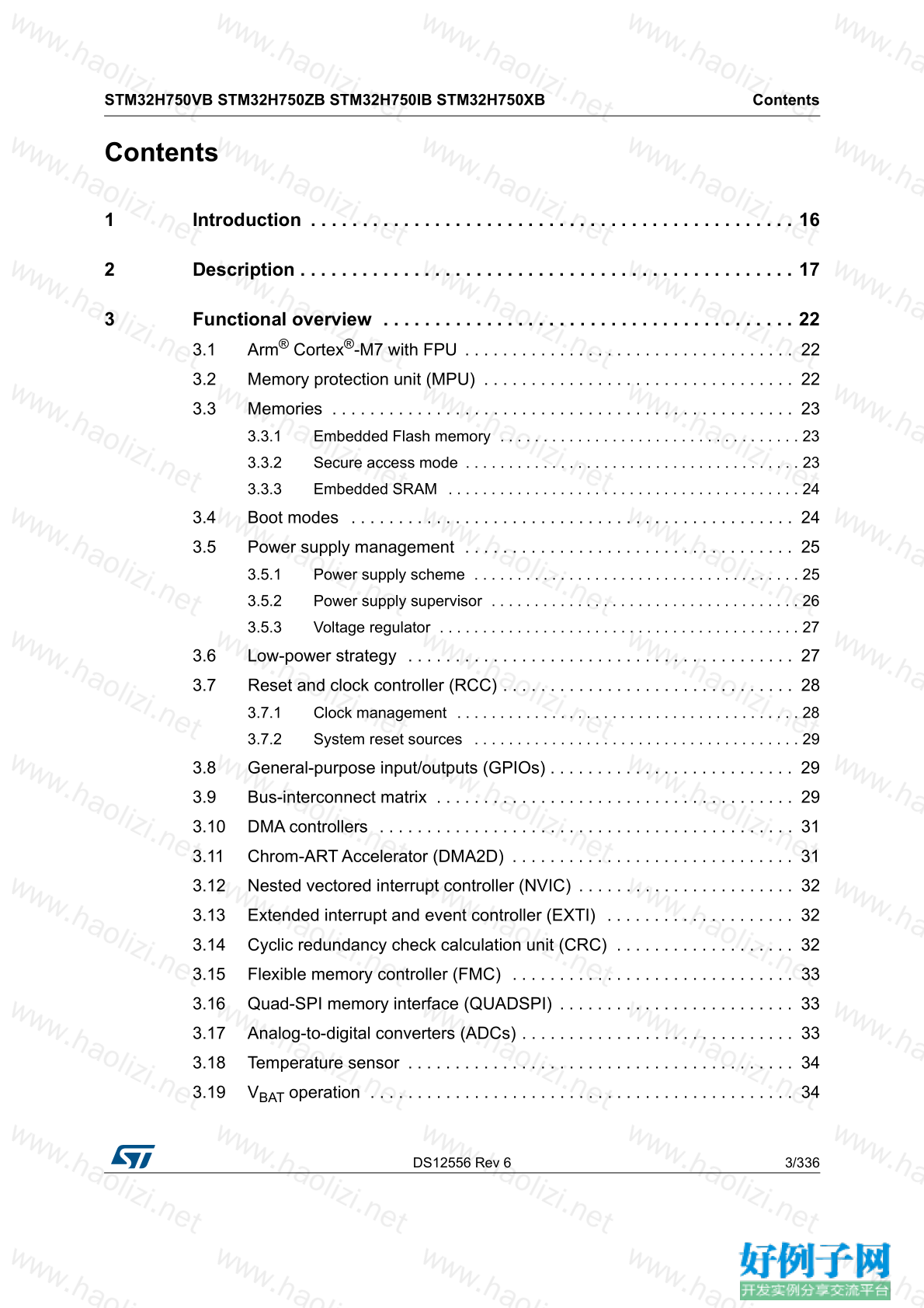

Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3 Functional overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.1 Arm ® Cortex ® -M7 with FPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.2 Memory protection unit (MPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.3 Memories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3.1 Embedded Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3.2 Secure access mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.3.3 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.4 Boot modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.5 Power supply management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.5.1 Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.5.2 Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.5.3 Voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.6 Low-power strategy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.7 Reset and clock controller (RCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.7.1 Clock management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3.7.2 System reset sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.8 General-purpose input/outputs (GPIOs) . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.9 Bus-interconnect matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.10 DMA controllers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.11 Chrom-ART Accelerator (DMA2D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3.12 Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . . . . 32

3.13 Extended interrupt and event controller (EXTI) . . . . . . . . . . . . . . . . . . . . 32

3.14 Cyclic redundancy check calculation unit (CRC) . . . . . . . . . . . . . . . . . . . 32

3.15 Flexible memory controller (FMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.16 Quad-SPI memory interface (QUADSPI) . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.17 Analog-to-digital converters (ADCs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.18 Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.19 V BAT operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Contents STM32H750VB STM32H750ZB STM32H750IB STM32H750XB

4/336 DS12556 Rev 6

3.20 Digital-to-analog converters (DAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.21 Ultra-low-power comparators (COMP) . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.22 Operational amplifiers (OPAMP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.23 Digital filter for sigma-delta modulators (DFSDM) . . . . . . . . . . . . . . . . . . 36

3.24 Digital camera interface (DCMI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.25 LCD-TFT controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.26 JPEG Codec (JPEG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.27 True random number generator (RNG) . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.28 Cryptographic acceleration (CRYP and HASH) . . . . . . . . . . . . . . . . . . . . 39

3.29 Timers and watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.29.1 High-resolution timer (HRTIM1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.29.2 Advanced-control timers (TIM1, TIM8) . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.29.3 General-purpose timers (TIMx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.29.4 Basic timers TIM6 and TIM7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.29.5 Low-power timers (LPTIM1, LPTIM2, LPTIM3, LPTIM4, LPTIM5) . . . . 43

3.29.6 Independent watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.29.7 Window watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.29.8 SysTick timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.30 Real-time clock (RTC), backup SRAM and backup registers . . . . . . . . . . 44

3.31 Inter-integrated circuit interface (I 2 C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.32 Universal synchronous/asynchronous receiver transmitter (USART) . . . 45

3.33 Low-power universal asynchronous receiver transmitter (LPUART) . . . . 46

3.34 Serial peripheral interfaces (SPI)/integrated interchip

sound interfaces (I2S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.35 Serial audio interfaces (SAI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.36 SPDIFRX Receiver Interface (SPDIFRX) . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.37 Single wire protocol master interface (SWPMI) . . . . . . . . . . . . . . . . . . . . 48

3.38 Management Data Input/Output (MDIO) slaves . . . . . . . . . . . . . . . . . . . . 49

3.39 SD/SDIO/MMC card host interfaces (SDMMC) . . . . . . . . . . . . . . . . . . . . 49

3.40 Controller area network (FDCAN1, FDCAN2) . . . . . . . . . . . . . . . . . . . . . 49

3.41 Universal serial bus on-the-go high-speed (OTG_HS) . . . . . . . . . . . . . . . 50

3.42 Ethernet MAC interface with dedicated DMA controller (ETH) . . . . . . . . . 50

3.43 High-definition multimedia interface (HDMI)

- consumer electronics control (CEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.44 Debug infrastructure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

DS12556 Rev 6 5/336

STM32H750VB STM32H750ZB STM32H750IB STM32H750XB Contents

7

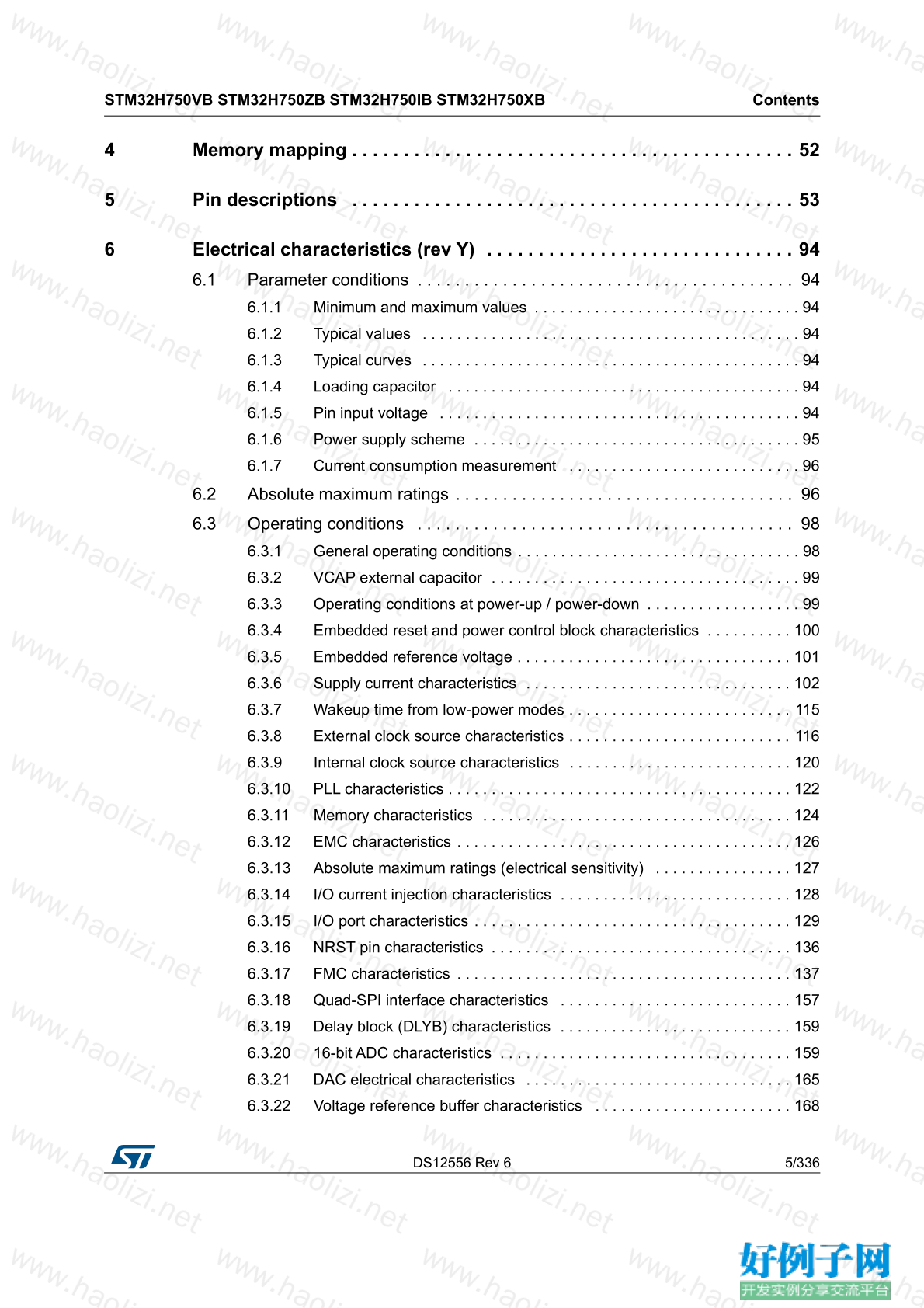

4 Memory mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

5 Pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

6 Electrical characteristics (rev Y) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

6.1 Parameter conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

6.1.1 Minimum and maximum values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

6.1.2 Typical values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

6.1.3 Typical curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

6.1.4 Loading capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

6.1.5 Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

6.1.6 Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

6.1.7 Current consumption measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.2 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

6.3 Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.3.1 General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.3.2 VCAP external capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

6.3.3 Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . . 99

6.3.4 Embedded reset and power control block characteristics . . . . . . . . . . 100

6.3.5 Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

6.3.6 Supply current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

6.3.7 Wakeup time from low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . 115

6.3.8 External clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 116

6.3.9 Internal clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 120

6.3.10 PLL characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

6.3.11 Memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

6.3.12 EMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

6.3.13 Absolute maximum ratings (electrical sensitivity) . . . . . . . . . . . . . . . . 127

6.3.14 I/O current injection characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

6.3.15 I/O port characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

6.3.16 NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

6.3.17 FMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

6.3.18 Quad-SPI interface characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

6.3.19 Delay block (DLYB) characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

6.3.20 16-bit ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

6.3.21 DAC electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

6.3.22 Voltage reference buffer characteristics . . . . . . . . . . . . . . . . . . . . . . . 168

Contents STM32H750VB STM32H750ZB STM32H750IB STM32H750XB

6/336 DS12556 Rev 6

6.3.23 Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

6.3.24 Temperature and V BAT monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

6.3.25 Voltage booster for analog switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

6.3.26 Comparator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

6.3.27 Operational amplifier characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 173

6.3.28 Digital filter for Sigma-Delta Modulators (DFSDM) characteristics . . . 176

6.3.29 Camera interface (DCMI) timing specifications . . . . . . . . . . . . . . . . . . 178

6.3.30 LCD-TFT controller (LTDC) characteristics . . . . . . . . . . . . . . . . . . . . . 179

6.3.31 Timer characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

6.3.32 Communications interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

6.3.33 JTAG/SWD interface characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 196

7 Electrical characteristics (rev V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.1 Parameter conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.1.1 Minimum and maximum values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.1.2 Typical values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.1.3 Typical curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.1.4 Loading capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.1.5 Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

7.1.6 Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

7.1.7 Current consumption measurement . . . . . . . . . . . . . . . . . . . . . . . . . . 201

7.2 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

7.3 Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.3.1 General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

7.3.2 VCAP external capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

7.3.3 Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . 205

7.3.4 Embedded reset and power control block characteristics . . . . . . . . . . 206

7.3.5 Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

7.3.6 Supply current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

7.3.7 Wakeup time from low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . 220

7.3.8 External clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 221

7.3.9 Internal clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 225

7.3.10 PLL characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

7.3.11 Memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

7.3.12 EMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

7.3.13 Absolute maximum ratings (electrical sensitivity) . . . . . . . . . . . . . . . . 233

7.3.14 I/O current injection characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

DS12556 Rev 6 7/336

STM32H750VB STM32H750ZB STM32H750IB STM32H750XB Contents

7

7.3.15 I/O port characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

7.3.16 NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

7.3.17 FMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

7.3.18 Quad-SPI interface characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

7.3.19 Delay block (DLYB) characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

7.3.20 16-bit ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

7.3.21 DAC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

7.3.22 Voltage reference buffer characteristics . . . . . . . . . . . . . . . . . . . . . . . 280

7.3.23 Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

7.3.24 Temperature and V BAT monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

7.3.25 Voltage booster for analog switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

7.3.26 Comparator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

7.3.27 Operational amplifier characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 284

7.3.28 Digital filter for Sigma-Delta Modulators (DFSDM) characteristics . . . 286

7.3.29 Camera interface (DCMI) timing specifications . . . . . . . . . . . . . . . . . . 289

7.3.30 LCD-TFT controller (LTDC) characteristics . . . . . . . . . . . . . . . . . . . . . 290

7.3.31 Timer characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

7.3.32 Communication interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

8 Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 311

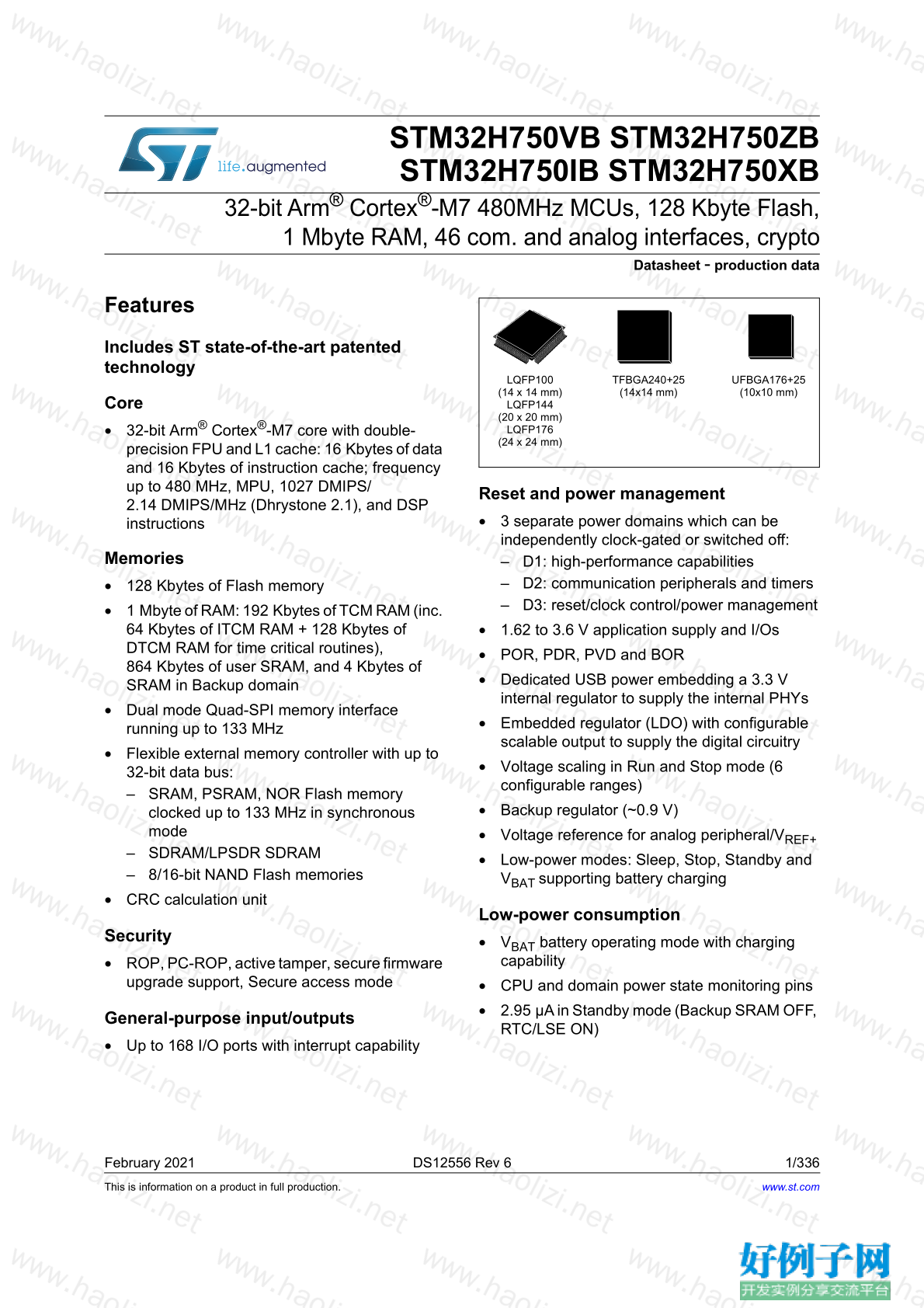

8.1 LQFP100 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .311

8.2 LQFP144 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 315

8.3 LQFP176 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

8.4 UFBGA176 25 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

8.5 TFBGA240 25 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

8.6 Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 329

8.6.1 Reference documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 330

9 Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 331

10 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332

List of tables STM32H750VB STM32H750ZB STM32H750IB STM32H750XB

8/336 DS12556 Rev 6

List of tables

Table 1. STM32H750xB features and peripheral counts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 2. System vs domain low-power mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 3. DFSDM implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 4. Timer feature comparison. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 5. USART features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 6. Legend/abbreviations used in the pinout table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 7. STM32H750xB pin/ball definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 8. Port A alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 9. Port B alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 10. Port C alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 11. Port D alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 12. Port E alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 13. Port F alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Table 14. Port G alternate functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 15. Port H alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 16. Port I alternate functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Table 17. Port J alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 18. Port K alternate functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 19. Voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 20. Current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 21. Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 22. General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 23. VCAP operating conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 24. Operating conditions at power-up / power-down (regulator ON) . . . . . . . . . . . . . . . . . . . . 99

Table 25. Reset and power control block characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 26. Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 27. Internal reference voltage calibration values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 28. Typical and maximum current consumption in Run mode, code with data processing

running from ITCM, regulator ON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 29. Typical and maximum current consumption in Run mode, code with data processing

running from Flash memory, cache ON, regulator ON . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 30. Typical and maximum current consumption in Run mode, code with data processing

running from Flash memory, cache OFF, regulator ON . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Table 31. Typical consumption in Run mode and corresponding performance

versus code position. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Table 32. Typical current consumption batch acquisition mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Table 33. Typical and maximum current consumption in Sleep mode, regulator ON. . . . . . . . . . . . 105

Table 34. Typical and maximum current consumption in Stop mode, regulator ON. . . . . . . . . . . . . 106

Table 35. Typical and maximum current consumption in Standby mode . . . . . . . . . . . . . . . . . . . . . 106

Table 36. Typical and maximum current consumption in VBAT mode. . . . . . . . . . . . . . . . . . . . . . . 107

Table 37. Peripheral current consumption in Run mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 38. Peripheral current consumption in Stop, Standby and VBAT mode. . . . . . . . . . . . . . . . . 114

Table 39. Low-power mode wakeup timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 40. High-speed external user clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 41. Low-speed external user clock characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Table 42. 4-48 MHz HSE oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 43. Low-speed external user clock characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 44. HSI48 oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

DS12556 Rev 6 9/336

STM32H750VB STM32H750ZB STM32H750IB STM32H750XB List of tables

12

Table 45. HSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 46. CSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 47. LSI oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 48. PLL characteristics (wide VCO frequency range). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 49. PLL characteristics (medium VCO frequency range) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 50. Flash memory characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 51. Flash memory programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Table 52. Flash memory endurance and data retention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Table 53. EMS characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Table 54. EMI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Table 55. ESD absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Table 56. Electrical sensitivities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 57. I/O current injection susceptibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 58. I/O static characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Table 59. Output voltage characteristics for all I/Os except PC13, PC14, PC15 and PI8 . . . . . . . . 131

Table 60. Output voltage characteristics for PC13, PC14, PC15 and PI8 . . . . . . . . . . . . . . . . . . . . 132

Table 61. Output timing characteristics (HSLV OFF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Table 62. Output timing characteristics (HSLV ON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 63. NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Table 64. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings . . . . . . . . . . . . . . . . . 139

Table 65. Asynchronous non-multiplexed SRAM/PSRAM/NOR read - NWAIT timings. . . . . . . . . . 139

Table 66. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings . . . . . . . . . . . . . . . . . 140

Table 67. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings. . . . . . . . . . 141

Table 68. Asynchronous multiplexed PSRAM/NOR read timings. . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Table 69. Asynchronous multiplexed PSRAM/NOR read-NWAIT timings . . . . . . . . . . . . . . . . . . . . 142

Table 70. Asynchronous multiplexed PSRAM/NOR write timings . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Table 71. Asynchronous multiplexed PSRAM/NOR write-NWAIT timings . . . . . . . . . . . . . . . . . . . . 144

Table 72. Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 73. Synchronous multiplexed PSRAM write timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 74. Synchronous non-multiplexed NOR/PSRAM read timings. . . . . . . . . . . . . . . . . . . . . . . . 149

Table 75. Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Table 76. Switching characteristics for NAND Flash read cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 77. Switching characteristics for NAND Flash write cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 78. SDRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Table 79. LPSDR SDRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Table 80. SDRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Table 81. LPSDR SDRAM write timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Table 82. QUADSPI characteristics in SDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Table 83. QUADSPI characteristics in DDR mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Table 84. Dynamics characteristics: Delay Block characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Table 85. ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Table 86. ADC accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table 87. DAC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Table 88. DAC accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Table 89. VREFBUF characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Table 90. Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Table 91. Temperature sensor calibration values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Table 92. V BAT monitoring characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Table 93. V BAT charging characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Table 94. Temperature monitoring characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Table 95. Voltage booster for analog switch characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Table 96. COMP characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

List of tables STM32H750VB STM32H750ZB STM32H750IB STM32H750XB

10/336 DS12556 Rev 6

Table 97. OPAMP characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 98. DFSDM measured timing - 1.62-3.6 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Table 99. DCMI characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Table 100. LTDC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Table 101. TIMx characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

Table 102. Minimum i2c_ker_ck frequency in all I2C modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Table 103. I2C analog filter characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Table 104. SPI dynamic characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Table 105. I 2 S dynamic characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Table 106. SAI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Table 107. MDIO Slave timing parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Table 108. Dynamic characteristics: SD / MMC characteristics, VDD = 2.7 to 3.6 V . . . . . . . . . . . . . 190

Table 109. Dynamic characteristics: eMMC characteristics, VDD = 1.71 to 1.9 V . . . . . . . . . . . . . . . 191

Table 110. USB OTG_FS electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Table 111. Dynamic characteristics: USB ULPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Table 112. Dynamics characteristics: Ethernet MAC signals for SMI. . . . . . . . . . . . . . . . . . . . . . . . . 194

Table 113. Dynamics characteristics: Ethernet MAC signals for RMII . . . . . . . . . . . . . . . . . . . . . . . . 195

Table 114. Dynamics characteristics: Ethernet MAC signals for MII . . . . . . . . . . . . . . . . . . . . . . . . . 196

Table 115. Dynamics JTAG characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 116. Dynamics SWD characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 117. Voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Table 118. Current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Table 119. Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Table 120. General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Table 121. Supply voltage and maximum frequency configuration . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Table 122. VCAP operating conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Table 123. Operating conditions at power-up / power-down (regulator ON) . . . . . . . . . . . . . . . . . . . 205

Table 124. Reset and power control block characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Table 125. Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Table 126. Internal reference voltage calibration values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Table 127. Typical and maximum current consumption in Run mode, code with data processing

running from ITCM, LDO regulator ON. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 128. Typical and maximum current consumption in Run mode, code with data processing

running from Flash memory, cache ON,

LDO regulator ON. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Table 129. Typical and maximum current consumption in Run mode, code with data processing

running from Flash memory, cache OFF,

LDO regulator ON. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Table 130. Typical and maximum current consumption batch acquisition mode,

LDO regulator ON. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Table 131. Typical and maximum current consumption in Stop, LDO regulator ON . . . . . . . . . . . . . 211

Table 132. Typical and maximum current consumption in Sleep mode, LDO regulator . . . . . . . . . . 212

Table 133. Typical and maximum current consumption in Standby . . . . . . . . . . . . . . . . . . . . . . . . . . 212

Table 134. Typical and maximum current consumption in VBAT mode. . . . . . . . . . . . . . . . . . . . . . . 213

Table 135. Peripheral current consumption in Run mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Table 136. Low-power mode wakeup timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

Table 137. High-speed external user clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

Table 138. Low-speed external user clock characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

Table 139. 4-48 MHz HSE oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

Table 140. Low-speed external user clock characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Table 141. HSI48 oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Table 142. HSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

DS12556 Rev 6 11/336

STM32H750VB STM32H750ZB STM32H750IB STM32H750XB List of tables

12

Table 143. CSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Table 144. LSI oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

Table 145. PLL characteristics (wide VCO frequency range). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

Table 146. PLL characteristics (medium VCO frequency range) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

Table 147. Flash memory characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Table 148. Flash memory programming. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Table 149. Flash memory endurance and data retention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Table 150. EMS characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

Table 151. EMI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

Table 152. ESD absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

Table 153. Electrical sensitivities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

Table 154. I/O current injection susceptibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

Table 155. I/O static characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

Table 156. Output voltage characteristics for all I/Os except PC13, PC14, PC15 and PI8 . . . . . . . . 237

Table 157. Output voltage characteristics for PC13, PC14, PC15 and PI8 . . . . . . . . . . . . . . . . . . . . 238

Table 158. Output timing characteristics (HSLV OFF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

Table 159. Output timing characteristics (HSLV ON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

Table 160. NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

Table 161. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings . . . . . . . . . . . . . . . . . 244

Table 162. Asynchronous non-multiplexed SRAM/PSRAM/NOR read-NWAIT timings. . . . . . . . . . . 244

Table 163. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings . . . . . . . . . . . . . . . . . 246

Table 164. Asynchronous non-multiplexed SRAM/PSRAM/NOR write-NWAIT timings. . . . . . . . . . . 246

Table 165. Asynchronous multiplexed PSRAM/NOR read timings. . . . . . . . . . . . . . . . . . . . . . . . . . . 248

Table 166. Asynchronous multiplexed PSRAM/NOR read-NWAIT timings . . . . . . . . . . . . . . . . . . . . 248

Table 167. Asynchronous multiplexed PSRAM/NOR write timings . . . . . . . . . . . . . . . . . . . . . . . . . . 249

Table 168. Asynchronous multiplexed PSRAM/NOR write-NWAIT timings . . . . . . . . . . . . . . . . . . . . 249

Table 169. Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Table 170. Synchronous multiplexed PSRAM write timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

Table 171. Synchronous non-multiplexed NOR/PSRAM read timings. . . . . . . . . . . . . . . . . . . . . . . . 255

Table 172. Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

Table 173. Switching characteristics for NAND Flash read cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . 260

Table 174. Switching characteristics for NAND Flash write cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . 260

Table 175. SDRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Table 176. LPSDR SDRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Table 177. SDRAM Write timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

Table 178. LPSDR SDRAM Write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

Table 179. QUADSPI characteristics in SDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 265

Table 180. QUADSPI characteristics in DDR mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

Table 181. Delay Block characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

Table 182. ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

Table 183. Minimum sampling time vs RAIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

Table 184. ADC accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Table 185. DAC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

Table 186. DAC accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

Table 187. VREFBUF characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

Table 188. Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

Table 189. Temperature sensor calibration values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

Table 190. V BAT monitoring characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

Table 191. V BAT charging characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

Table 192. Temperature monitoring characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

Table 193. Voltage booster for analog switch characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

Table 194. COMP characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

List of tables STM32H750VB STM32H750ZB STM32H750IB STM32H750XB

12/336 DS12556 Rev 6

Table 195. Operational amplifier characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

Table 196. DFSDM measured timing - 1.62-3.6 V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

Table 197. DCMI characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

Table 198. LTDC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

Table 199. TIMx characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

Table 200. Minimum i2c_ker_ck frequency in all I2C modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

Table 201. I2C analog filter characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

Table 202. USART characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

Table 203. SPI dynamic characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

Table 204. I 2 S dynamic characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

Table 205. SAI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

Table 206. MDIO Slave timing parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

Table 207. Dynamics characteristics: SD / MMC characteristics, VDD = 2.7 to 3.6 V . . . . . . . . . . . . 303

Table 208. Dynamics characteristics: eMMC characteristics VDD = 1.71V to 1.9V. . . . . . . . . . . . . . 304

Table 209. Dynamics characteristics: USB ULPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

Table 210. Dynamics characteristics: Ethernet MAC signals for SMI . . . . . . . . . . . . . . . . . . . . . . . . 307

Table 211. Dynamics characteristics: Ethernet MAC signals for RMII . . . . . . . . . . . . . . . . . . . . . . . . 308

Table 212. Dynamics characteristics: Ethernet MAC signals for MII . . . . . . . . . . . . . . . . . . . . . . . . . 308

Table 213. Dynamics JTAG characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 309

Table 214. Dynamics SWD characteristics: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 310

Table 215. LQPF100 package mechanical data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

Table 216. LQFP144 package mechanical data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316

Table 217. LQFP176 package mechanical data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

Table 218. UFBGA176 25 package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

Table 219. UFBGA176 25 recommended PCB design rules (0.65 mm pitch BGA). . . . . . . . . . . . . 324

Table 220. TFBG240 25 ball package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

Table 221. TFBGA240 25 recommended PCB design rules (0.8 mm pitch). . . . . . . . . . . . . . . . . . . 328

Table 222. Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 329

Table 223. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332

DS12556 Rev 6 13/336

STM32H750VB STM32H750ZB STM32H750IB STM32H750XB List of figures

15

List of figures

Figure 1. STM32H750xB block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 2. Power-up/power-down sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 3. STM32H750xB bus matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 4. LQFP100 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 5. LQFP144 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 6. LQFP176 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 7. UFBGA176 25 ballout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 8. TFBGA240 25 ballout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 9. Pin loading conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 10. Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 11. Power supply scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 12. Current consumption measurement scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 13. External capacitor C EXT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Figure 14. High-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Figure 15. Low-speed external clock source AC timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Figure 16. Typical application with an 8 MHz crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Figure 17. Typical application with a 32.768 kHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Figure 18. VIL/VIH for all I/Os except BOOT0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Figure 19. Recommended NRST pin protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Figure 20. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms . . . . . . . . . . . . . . 138

Figure 21. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms . . . . . . . . . . . . . . 140

Figure 22. Asynchronous multiplexed PSRAM/NOR read waveforms. . . . . . . . . . . . . . . . . . . . . . . . 141

Figure 23. Asynchronous multiplexed PSRAM/NOR write waveforms . . . . . . . . . . . . . . . . . . . . . . . 143

Figure 24. Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Figure 25. Synchronous multiplexed PSRAM write timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Figure 26. Synchronous non-multiplexed NOR/PSRAM read timings. . . . . . . . . . . . . . . . . . . . . . . . 149

Figure 27. Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Figure 28. NAND controller waveforms for read access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Figure 29. NAND controller waveforms for write access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Figure 30. NAND controller waveforms for common memory read access. . . . . . . . . . . . . . . . . . . . 152

Figure 31. NAND controller waveforms for common memory write access. . . . . . . . . . . . . . . . . . . . 153

Figure 32. SDRAM read access waveforms (CL = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Figure 33. SDRAM write access waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Figure 34. Quad-SPI timing diagram - SDR mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Figure 35. Quad-SPI timing diagram - DDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Figure 36. ADC accuracy characteristics (example for 12-bit resolution) . . . . . . . . . . . . . . . . . . . . . 162

Figure 37. Typical connection diagram using the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Figure 38. Power supply and reference decoupling (V REF not connected to V DDA ). . . . . . . . . . . . . 164

Figure 39. Power supply and reference decoupling (V REF connected to V DDA ). . . . . . . . . . . . . . . . 164

Figure 40. 12-bit buffered /non-buffered DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Figure 41. Channel transceiver timing diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Figure 42. DCMI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Figure 43. LCD-TFT horizontal timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

Figure 44. LCD-TFT vertical timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 180

Figure 45. SPI timing diagram - slave mode and CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Figure 46. SPI timing diagram - slave mode and CPHA = 1 (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Figure 47. SPI timing diagram - master mode (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Figure 48. I 2 S slave timing diagram (Philips protocol) (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

List of figures STM32H750VB STM32H750ZB STM32H750IB STM32H750XB

14/336 DS12556 Rev 6

Figure 49. I 2 S master timing diagram (Philips protocol) (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Figure 50. SAI master timing waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Figure 51. SAI slave timing waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Figure 52. MDIO Slave timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

Figure 53. SDIO high-speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Figure 54. SD default mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Figure 55. DDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Figure 56. ULPI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Figure 57. Ethernet SMI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

Figure 58. Ethernet RMII timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

Figure 59. Ethernet MII timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Figure 60. JTAG timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Figure 61. SWD timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Figure 62. Pin loading conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Figure 63. Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Figure 64. Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

Figure 65. Current consumption measurement scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Figure 66. External capacitor C EXT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Figure 67. High-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

Figure 68. Low-speed external clock source AC timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

Figure 69. Typical application with an 8 MHz crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Figure 70. Typical application with a 32.768 kHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

Figure 71. VIL/VIH for all I/Os except BOOT0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

Figure 72. Recommended NRST pin protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

Figure 73. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms . . . . . . . . . . . . . . 243

Figure 74. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms . . . . . . . . . . . . . . 245

Figure 75. Asynchronous multiplexed PSRAM/NOR read waveforms. . . . . . . . . . . . . . . . . . . . . . . . 247

Figure 76. Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . 250

Figure 77. Synchronous multiplexed PSRAM write timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

Figure 78. Synchronous non-multiplexed NOR/PSRAM read timings. . . . . . . . . . . . . . . . . . . . . . . . 254

Figure 79. Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Figure 80. NAND controller waveforms for read access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

Figure 81. NAND controller waveforms for write access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

Figure 82. NAND controller waveforms for common memory read access. . . . . . . . . . . . . . . . . . . . 259

Figure 83. NAND controller waveforms for common memory write access. . . . . . . . . . . . . . . . . . . . 260

Figure 84. SDRAM read access waveforms (CL = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

Figure 85. SDRAM write access waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

Figure 86. QUADSPI timing diagram - SDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

Figure 87. Quad-SPI timing diagram - DDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

Figure 88. ADC accuracy characteristics (example for 12-bit resolution) . . . . . . . . . . . . . . . . . . . . . 274

Figure 89. Typical connection diagram using the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

Figure 90. Power supply and reference decoupling (V REF not connected to V DDA ). . . . . . . . . . . . . 275

Figure 91. Power supply and reference decoupling (V REF connected to V DDA ). . . . . . . . . . . . . . . . 275

Figure 92. 12-bit buffered /non-buffered DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

Figure 93. Channel transceiver timing diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

Figure 94. DCMI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

Figure 95. LCD-TFT horizontal timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

Figure 96. LCD-TFT vertical timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

Figure 97. USART timing diagram in Master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

Figure 98. USART timing diagram in Slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

Figure 99. SPI timing diagram - slave mode and CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

Figure 100. SPI timing diagram - slave mode and CPHA = 1 (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 297

DS12556 Rev 6 15/336

STM32H750VB STM32H750ZB STM32H750IB STM32H750XB List of figures

15

Figure 101. SPI timing diagram - master mode (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 298

Figure 102. I 2 S slave timing diagram (Philips protocol) (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

Figure 103. I 2 S master timing diagram (Philips protocol) (1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

Figure 104. SAI master timing waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

Figure 105. SAI slave timing waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

Figure 106. MDIO Slave timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

Figure 107. SDIO high-speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

Figure 108. SD default mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

Figure 109. DDR mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

Figure 110. ULPI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

Figure 111. Ethernet SMI timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 307

Figure 112. Ethernet RMII timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 308

Figure 113. Ethernet MII timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 309

Figure 114. JTAG timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 310

Figure 115. SWD timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 310

Figure 116. LQFP100 package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 311

Figure 117. LQFP100 recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

Figure 118. LQFP100 marking example (package top view). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 314

Figure 119. LQFP144 package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 315

Figure 120. LQFP144 package recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

Figure 121. LQFP144 marking example (package top view). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 318

Figure 122. LQFP176 package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

Figure 123. LQFP176 package recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 321

Figure 124. LQFP176 marking example (package top view). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

Figure 125. UFBGA176 25 package outline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

Figure 126. UFBGA176 25 package recommended footprint. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

Figure 127. UFBGA176 25 marking example (package top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . 325

Figure 128. TFBGA240 25 package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

Figure 129. TFBGA240 25 package recommended footprint. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

Figure 130. TFBGA240 25 marking example (package top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . 328

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论