实例介绍

【实例截图】

【核心代码】

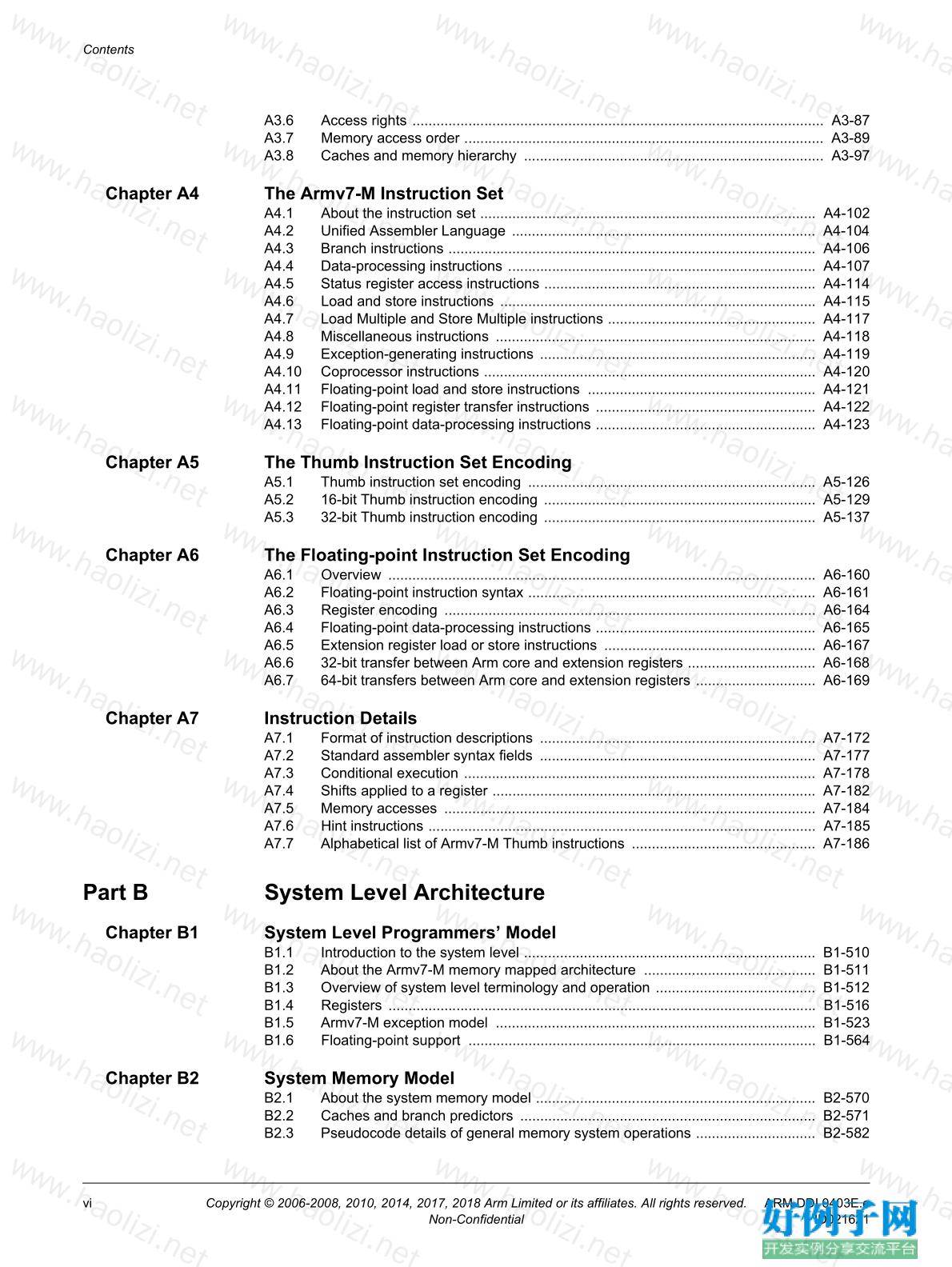

Contents

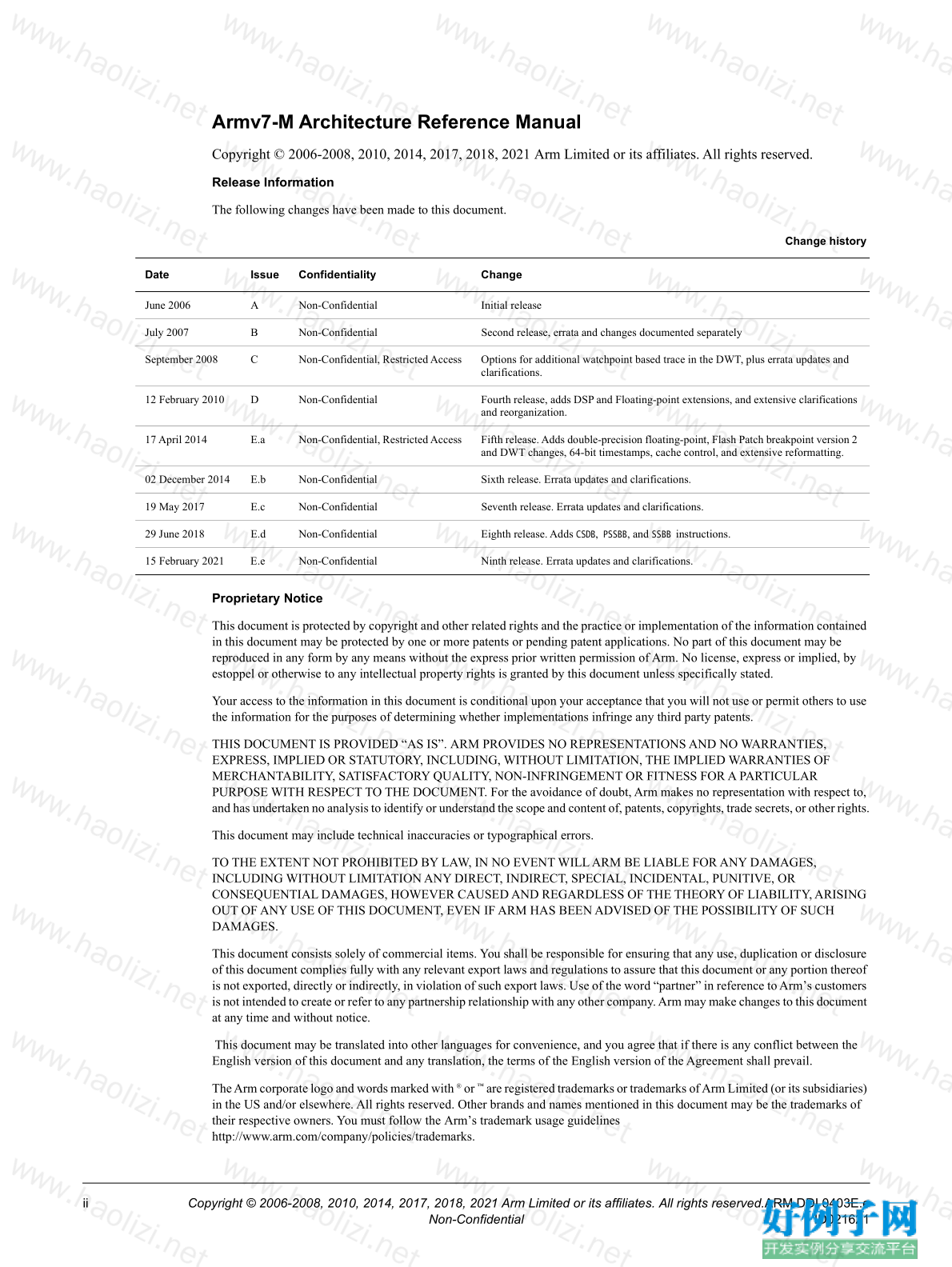

Armv7-M Architecture Reference Manual

Preface

About this manual ....................................................................................................... x

Using this manual ....................................................................................................... xi

Conventions .............................................................................................................. xiii

Further reading .......................................................................................................... xiv

Feedback .................................................................................................................. xv

Part A Application Level Architecture

Chapter A1 Introduction

A1.1 About the Armv7 architecture, and architecture profiles ..................................... A1-20

A1.2 The Armv7-M architecture profile ........................................................................ A1-21

A1.3 Architecture extensions ....................................................................................... A1-22

Chapter A2 Application Level Programmers’ Model

A2.1 About the application level programmers’ model ................................................ A2-24

A2.2 Arm processor data types and arithmetic ............................................................ A2-25

A2.3 Registers and Execution state ............................................................................ A2-30

A2.4 Exceptions, faults and interrupts ......................................................................... A2-33

A2.5 The optional Floating-point Extension ................................................................. A2-34

A2.6 Coprocessor support ........................................................................................... A2-61

Chapter A3 Arm Architecture Memory Model

A3.1 Address space .................................................................................................... A3-64

A3.2 Alignment support ............................................................................................... A3-65

A3.3 Endian support .................................................................................................... A3-67

A3.4 Synchronization and semaphores ....................................................................... A3-70

A3.5 Memory types and attributes and the memory order model ................................ A3-78

Contents

vi Copyright © 2006-2008, 2010, 2014, 2017, 2018 Arm Limited or its affiliates. All rights reserved. ARM DDI 0403E.e

Non-Confidential ID021621

A3.6 Access rights ....................................................................................................... A3-87

A3.7 Memory access order .......................................................................................... A3-89

A3.8 Caches and memory hierarchy ........................................................................... A3-97

Chapter A4 The Armv7-M Instruction Set

A4.1 About the instruction set .................................................................................... A4-102

A4.2 Unified Assembler Language ............................................................................ A4-104

A4.3 Branch instructions ............................................................................................ A4-106

A4.4 Data-processing instructions ............................................................................. A4-107

A4.5 Status register access instructions .................................................................... A4-114

A4.6 Load and store instructions ............................................................................... A4-115

A4.7 Load Multiple and Store Multiple instructions .................................................... A4-117

A4.8 Miscellaneous instructions ................................................................................ A4-118

A4.9 Exception-generating instructions ..................................................................... A4-119

A4.10 Coprocessor instructions ................................................................................... A4-120

A4.11 Floating-point load and store instructions ......................................................... A4-121

A4.12 Floating-point register transfer instructions ....................................................... A4-122

A4.13 Floating-point data-processing instructions ....................................................... A4-123

Chapter A5 The Thumb Instruction Set Encoding

A5.1 Thumb instruction set encoding ........................................................................ A5-126

A5.2 16-bit Thumb instruction encoding .................................................................... A5-129

A5.3 32-bit Thumb instruction encoding .................................................................... A5-137

Chapter A6 The Floating-point Instruction Set Encoding

A6.1 Overview ........................................................................................................... A6-160

A6.2 Floating-point instruction syntax ........................................................................ A6-161

A6.3 Register encoding ............................................................................................. A6-164

A6.4 Floating-point data-processing instructions ....................................................... A6-165

A6.5 Extension register load or store instructions ..................................................... A6-167

A6.6 32-bit transfer between Arm core and extension registers ................................ A6-168

A6.7 64-bit transfers between Arm core and extension registers .............................. A6-169

Chapter A7 Instruction Details

A7.1 Format of instruction descriptions ..................................................................... A7-172

A7.2 Standard assembler syntax fields ..................................................................... A7-177

A7.3 Conditional execution ........................................................................................ A7-178

A7.4 Shifts applied to a register ................................................................................. A7-182

A7.5 Memory accesses ............................................................................................. A7-184

A7.6 Hint instructions ................................................................................................. A7-185

A7.7 Alphabetical list of Armv7-M Thumb instructions .............................................. A7-186

Part B System Level Architecture

Chapter B1 System Level Programmers’ Model

B1.1 Introduction to the system level ......................................................................... B1-510

B1.2 About the Armv7-M memory mapped architecture ........................................... B1-511

B1.3 Overview of system level terminology and operation ........................................ B1-512

B1.4 Registers ........................................................................................................... B1-516

B1.5 Armv7-M exception model ................................................................................ B1-523

B1.6 Floating-point support ....................................................................................... B1-564

Chapter B2 System Memory Model

B2.1 About the system memory model ...................................................................... B2-570

B2.2 Caches and branch predictors .......................................................................... B2-571

B2.3 Pseudocode details of general memory system operations .............................. B2-582

Contents

ARM DDI 0403E.e Copyright © 2006-2008, 2010, 2014, 2017, 2018 Arm Limited or its affiliates. All rights reserved. vii

ID021621 Non-Confidential

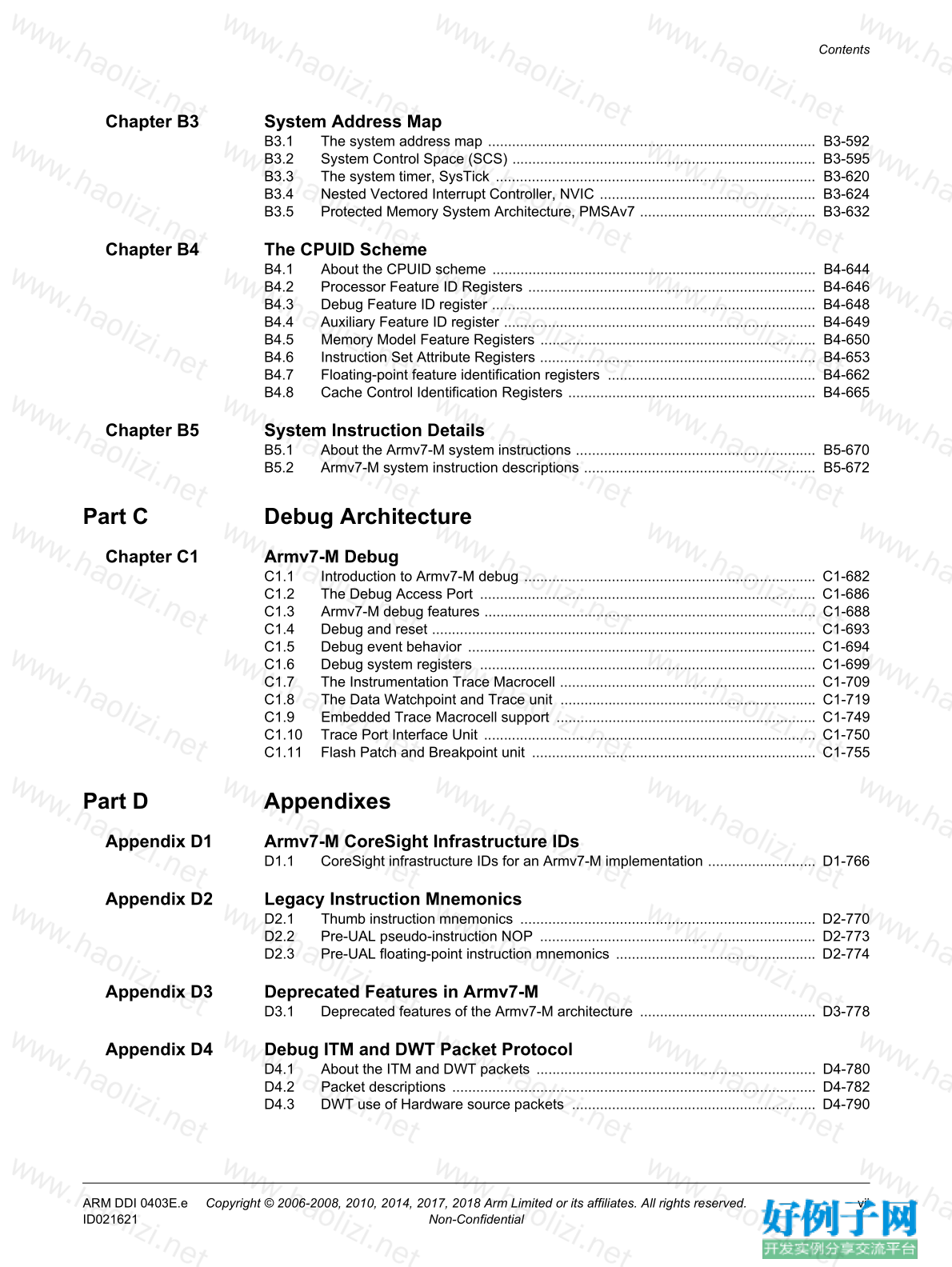

Chapter B3 System Address Map

B3.1 The system address map .................................................................................. B3-592

B3.2 System Control Space (SCS) ............................................................................ B3-595

B3.3 The system timer, SysTick ................................................................................ B3-620

B3.4 Nested Vectored Interrupt Controller, NVIC ...................................................... B3-624

B3.5 Protected Memory System Architecture, PMSAv7 ............................................ B3-632

Chapter B4 The CPUID Scheme

B4.1 About the CPUID scheme ................................................................................. B4-644

B4.2 Processor Feature ID Registers ........................................................................ B4-646

B4.3 Debug Feature ID register ................................................................................. B4-648

B4.4 Auxiliary Feature ID register .............................................................................. B4-649

B4.5 Memory Model Feature Registers ..................................................................... B4-650

B4.6 Instruction Set Attribute Registers ..................................................................... B4-653

B4.7 Floating-point feature identification registers .................................................... B4-662

B4.8 Cache Control Identification Registers .............................................................. B4-665

Chapter B5 System Instruction Details

B5.1 About the Armv7-M system instructions ............................................................ B5-670

B5.2 Armv7-M system instruction descriptions .......................................................... B5-672

Part C Debug Architecture

Chapter C1 Armv7-M Debug

C1.1 Introduction to Armv7-M debug ......................................................................... C1-682

C1.2 The Debug Access Port .................................................................................... C1-686

C1.3 Armv7-M debug features ................................................................................... C1-688

C1.4 Debug and reset ................................................................................................ C1-693

C1.5 Debug event behavior ....................................................................................... C1-694

C1.6 Debug system registers .................................................................................... C1-699

C1.7 The Instrumentation Trace Macrocell ................................................................ C1-709

C1.8 The Data Watchpoint and Trace unit ................................................................ C1-719

C1.9 Embedded Trace Macrocell support ................................................................. C1-749

C1.10 Trace Port Interface Unit ................................................................................... C1-750

C1.11 Flash Patch and Breakpoint unit ....................................................................... C1-755

Part D Appendixes

Appendix D1 Armv7-M CoreSight Infrastructure IDs

D1.1 CoreSight infrastructure IDs for an Armv7-M implementation ........................... D1-766

Appendix D2 Legacy Instruction Mnemonics

D2.1 Thumb instruction mnemonics .......................................................................... D2-770

D2.2 Pre-UAL pseudo-instruction NOP ..................................................................... D2-773

D2.3 Pre-UAL floating-point instruction mnemonics .................................................. D2-774

Appendix D3 Deprecated Features in Armv7-M

D3.1 Deprecated features of the Armv7-M architecture ............................................ D3-778

Appendix D4 Debug ITM and DWT Packet Protocol

D4.1 About the ITM and DWT packets ...................................................................... D4-780

D4.2 Packet descriptions ........................................................................................... D4-782

D4.3 DWT use of Hardware source packets ............................................................. D4-790

Contents

viii Copyright © 2006-2008, 2010, 2014, 2017, 2018 Arm Limited or its affiliates. All rights reserved. ARM DDI 0403E.e

Non-Confidential ID021621

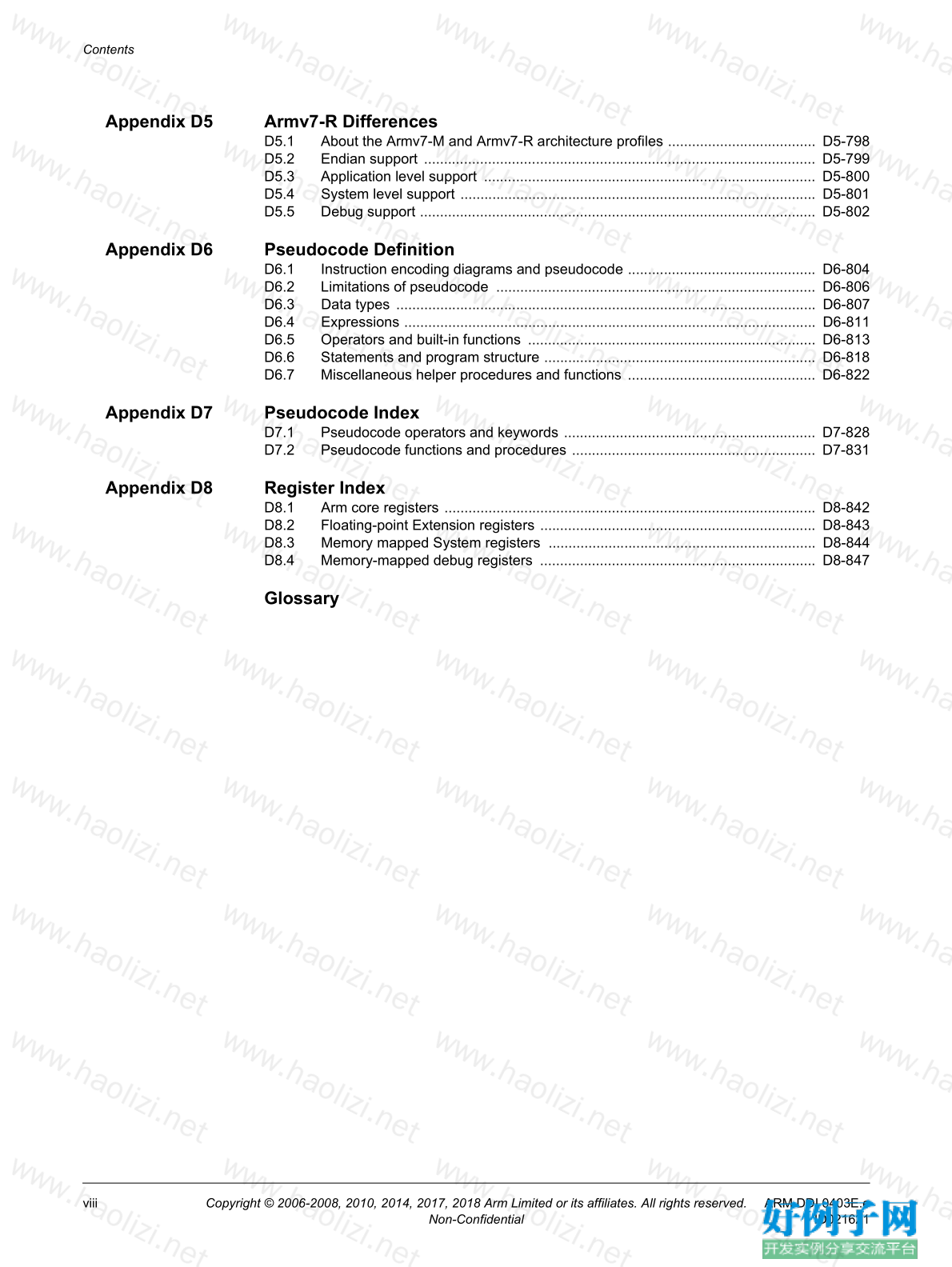

Appendix D5 Armv7-R Differences

D5.1 About the Armv7-M and Armv7-R architecture profiles ..................................... D5-798

D5.2 Endian support .................................................................................................. D5-799

D5.3 Application level support ................................................................................... D5-800

D5.4 System level support ......................................................................................... D5-801

D5.5 Debug support ................................................................................................... D5-802

Appendix D6 Pseudocode Definition

D6.1 Instruction encoding diagrams and pseudocode ............................................... D6-804

D6.2 Limitations of pseudocode ................................................................................ D6-806

D6.3 Data types ......................................................................................................... D6-807

D6.4 Expressions ....................................................................................................... D6-811

D6.5 Operators and built-in functions ........................................................................ D6-813

D6.6 Statements and program structure .................................................................... D6-818

D6.7 Miscellaneous helper procedures and functions ............................................... D6-822

Appendix D7 Pseudocode Index

D7.1 Pseudocode operators and keywords ............................................................... D7-828

D7.2 Pseudocode functions and procedures ............................................................. D7-831

Appendix D8 Register Index

D8.1 Arm core registers ............................................................................................. D8-842

D8.2 Floating-point Extension registers ..................................................................... D8-843

D8.3 Memory mapped System registers ................................................................... D8-844

D8.4 Memory-mapped debug registers ..................................................................... D8-847

Glossary

ARM DDI 0403E.eCopyright © 2006-2008, 2010, 2014, 2017, 2018, 2021 Arm Limited or its affiliates. All rights reserved. ix

ID021621 Non-Confidential

Preface

This preface describes the contents of this manual, then lists the conventions and terminology it

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论