【实例简介】RH850/E1L 用户手册:硬件

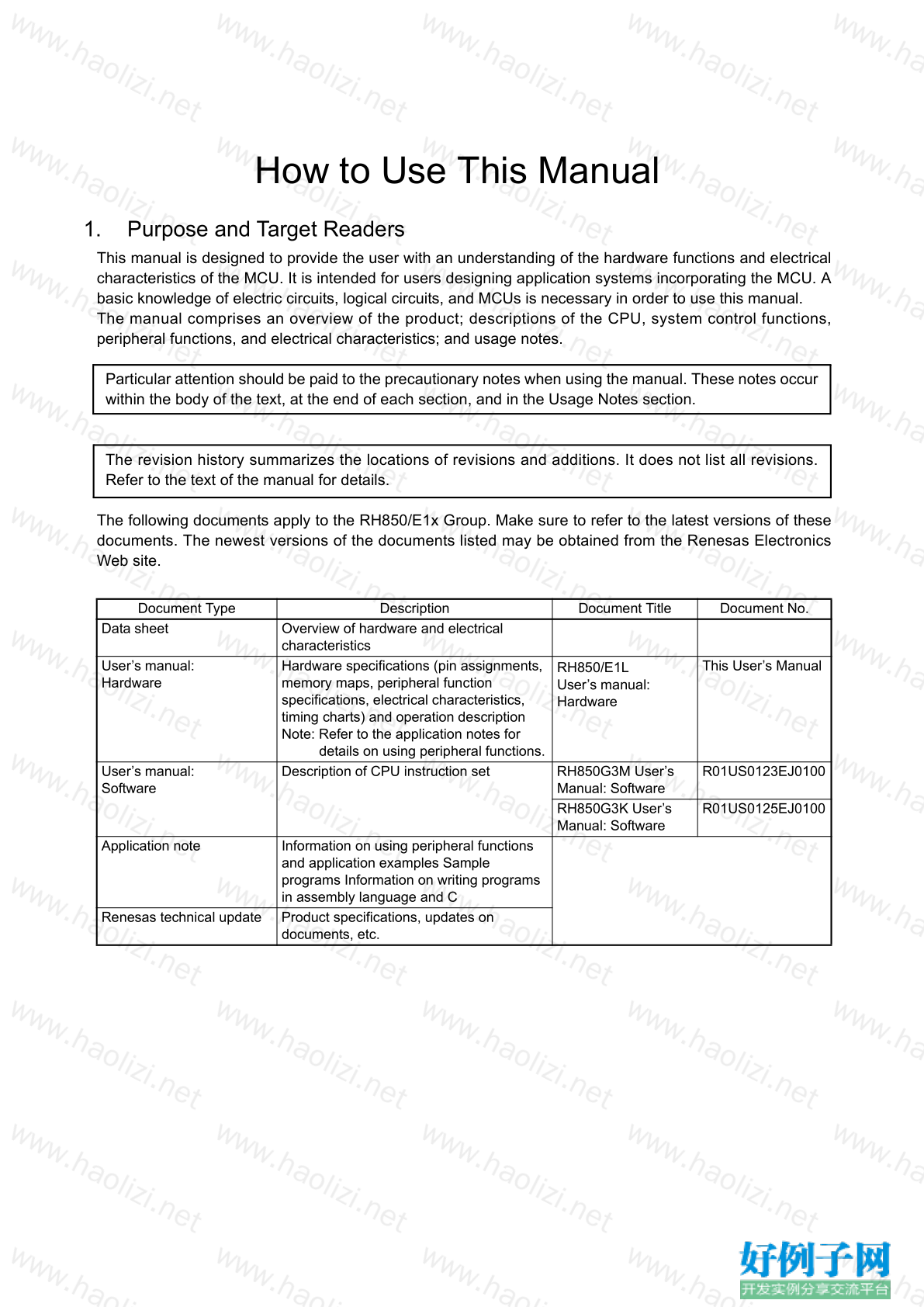

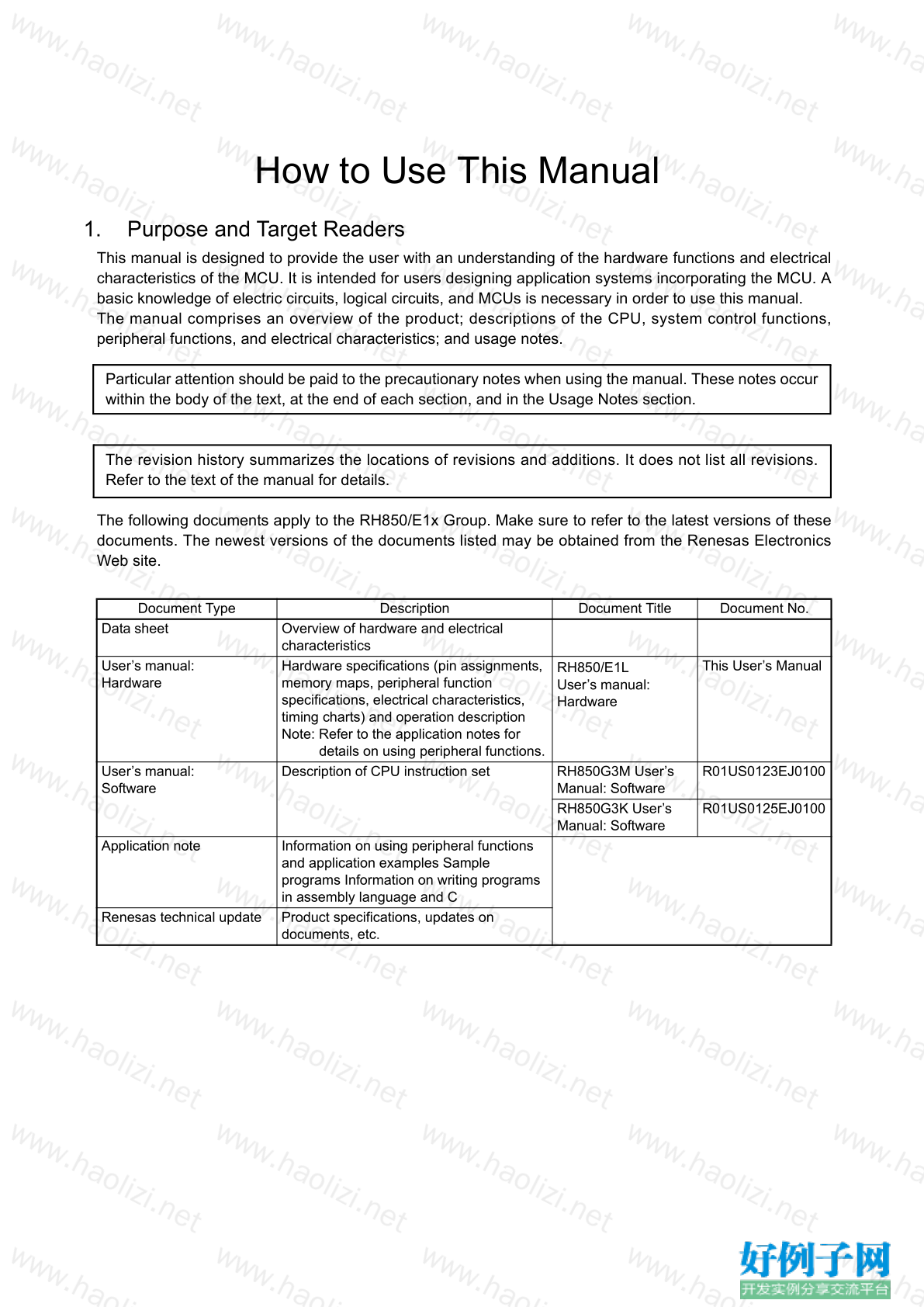

RH850/E1L User’s Manual: Hardware

【实例截图】

【核心代码】

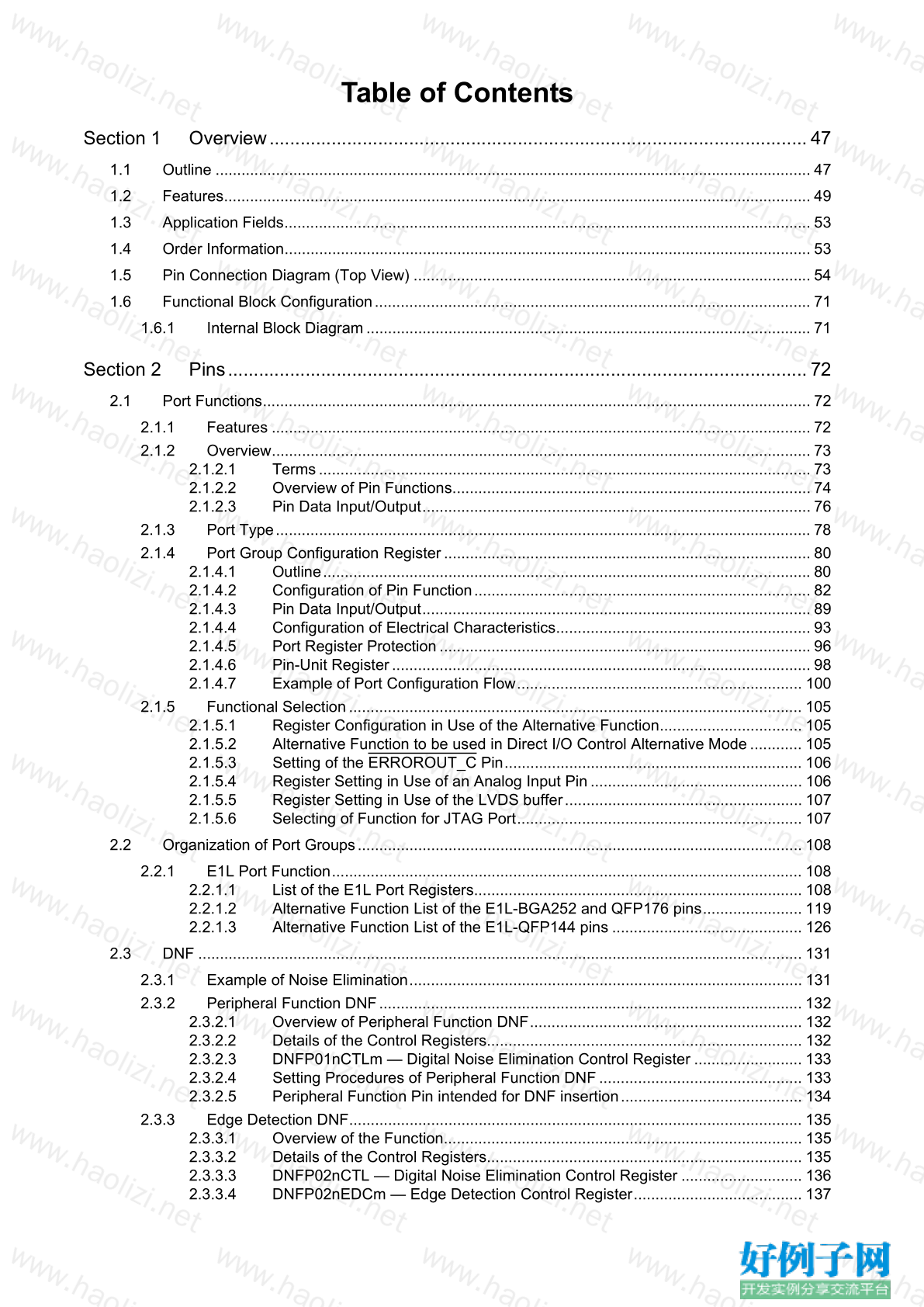

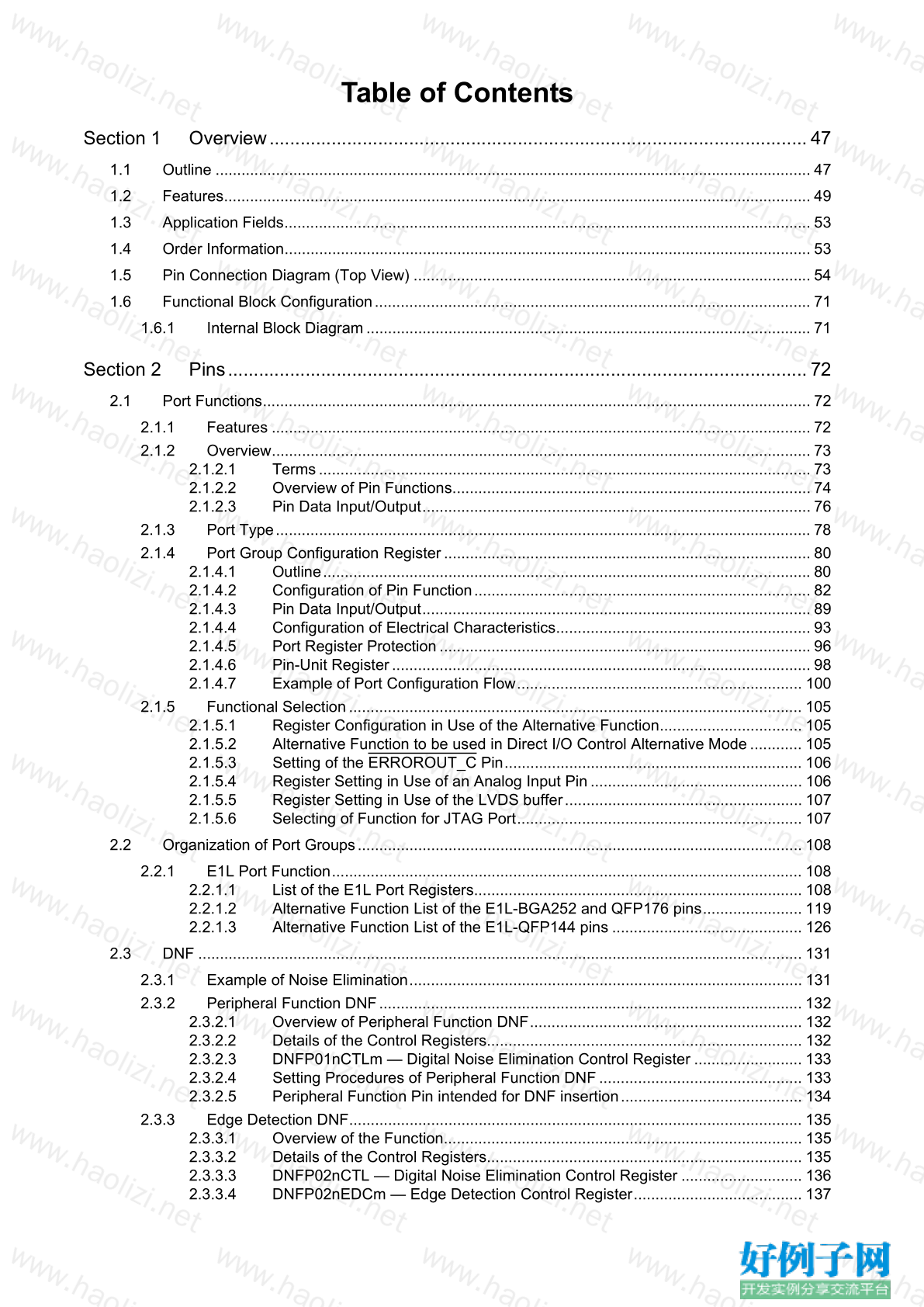

Table of Contents

Section 1 Overview........................................................................................................ 47

1.1 Outline .......................................................................................................................................... 47

1.2 Features........................................................................................................................................ 49

1.3 Application Fields.......................................................................................................................... 53

1.4 Order Information.......................................................................................................................... 53

1.5 Pin Connection Diagram (Top View) ............................................................................................ 54

1.6 Functional Block Configuration..................................................................................................... 71

1.6.1 Internal Block Diagram ....................................................................................................... 71

Section 2 Pins................................................................................................................ 72

2.1 Port Functions............................................................................................................................... 72

2.1.1 Features ............................................................................................................................. 72

2.1.2 Overview............................................................................................................................. 73

2.1.2.1 Terms .................................................................................................................. 73

2.1.2.2 Overview of Pin Functions................................................................................... 74

2.1.2.3 Pin Data Input/Output.......................................................................................... 76

2.1.3 Port Type............................................................................................................................ 78

2.1.4 Port Group Configuration Register ..................................................................................... 80

2.1.4.1 Outline................................................................................................................. 80

2.1.4.2 Configuration of Pin Function.............................................................................. 82

2.1.4.3 Pin Data Input/Output.......................................................................................... 89

2.1.4.4 Configuration of Electrical Characteristics........................................................... 93

2.1.4.5 Port Register Protection ...................................................................................... 96

2.1.4.6 Pin-Unit Register ................................................................................................. 98

2.1.4.7 Example of Port Configuration Flow.................................................................. 100

2.1.5 Functional Selection ......................................................................................................... 105

2.1.5.1 Register Configuration in Use of the Alternative Function................................. 105

2.1.5.2 Alternative Function to be used in Direct I/O Control Alternative Mode ............ 105

2.1.5.3 Setting of the ERROROUT_C Pin..................................................................... 106

2.1.5.4 Register Setting in Use of an Analog Input Pin ................................................. 106

2.1.5.5 Register Setting in Use of the LVDS buffer....................................................... 107

2.1.5.6 Selecting of Function for JTAG Port.................................................................. 107

2.2 Organization of Port Groups....................................................................................................... 108

2.2.1 E1L Port Function............................................................................................................. 108

2.2.1.1 List of the E1L Port Registers............................................................................ 108

2.2.1.2 Alternative Function List of the E1L-BGA252 and QFP176 pins....................... 119

2.2.1.3 Alternative Function List of the E1L-QFP144 pins ............................................ 126

2.3 DNF ............................................................................................................................................ 131

2.3.1 Example of Noise Elimination........................................................................................... 131

2.3.2 Peripheral Function DNF.................................................................................................. 132

2.3.2.1 Overview of Peripheral Function DNF............................................................... 132

2.3.2.2 Details of the Control Registers......................................................................... 132

2.3.2.3 DNFP01nCTLm — Digital Noise Elimination Control Register ......................... 133

2.3.2.4 Setting Procedures of Peripheral Function DNF ............................................... 133

2.3.2.5 Peripheral Function Pin intended for DNF insertion.......................................... 134

2.3.3 Edge Detection DNF......................................................................................................... 135

2.3.3.1 Overview of the Function................................................................................... 135

2.3.3.2 Details of the Control Registers......................................................................... 135

2.3.3.3 DNFP02nCTL — Digital Noise Elimination Control Register ............................ 136

2.3.3.4 DNFP02nEDCm — Edge Detection Control Register....................................... 1372.3.3.5 DNFP02nEDFm — Edge Detection Flag Register............................................ 138

2.3.3.6 Setting Procedures of Edge Detection DNF...................................................... 138

2.3.3.7 Pn_m Pins Intended for DNF Insertion.............................................................. 139

2.4 POD Control ............................................................................................................................... 141

2.4.1 Overview of the Function.................................................................................................. 141

2.5 Pin Description............................................................................................................................ 143

2.5.1 Overview........................................................................................................................... 143

2.5.2 List of Pin Functions ......................................................................................................... 143

2.5.3 Pin State........................................................................................................................... 154

2.5.4 Handling of Unused Pins.................................................................................................. 156

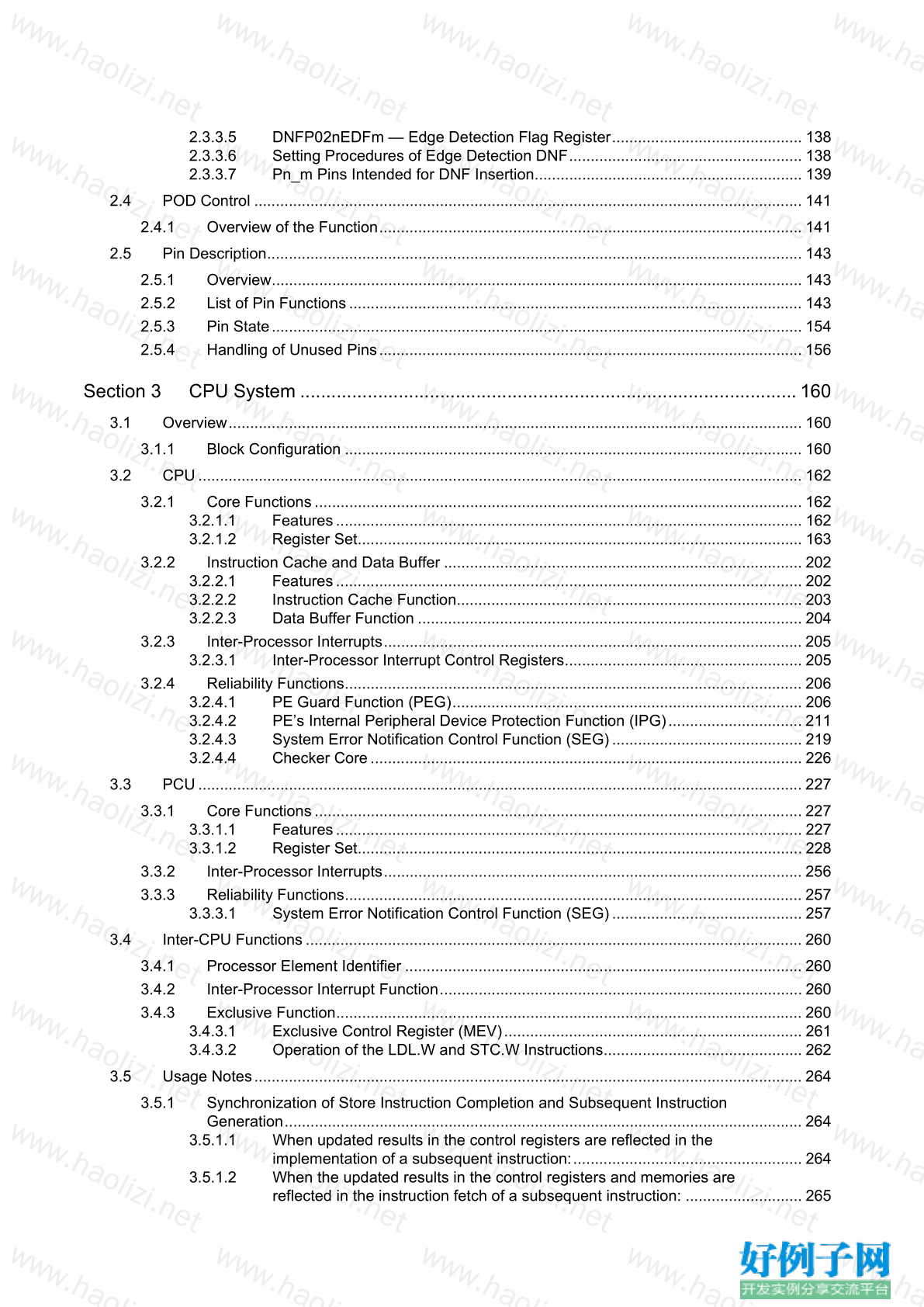

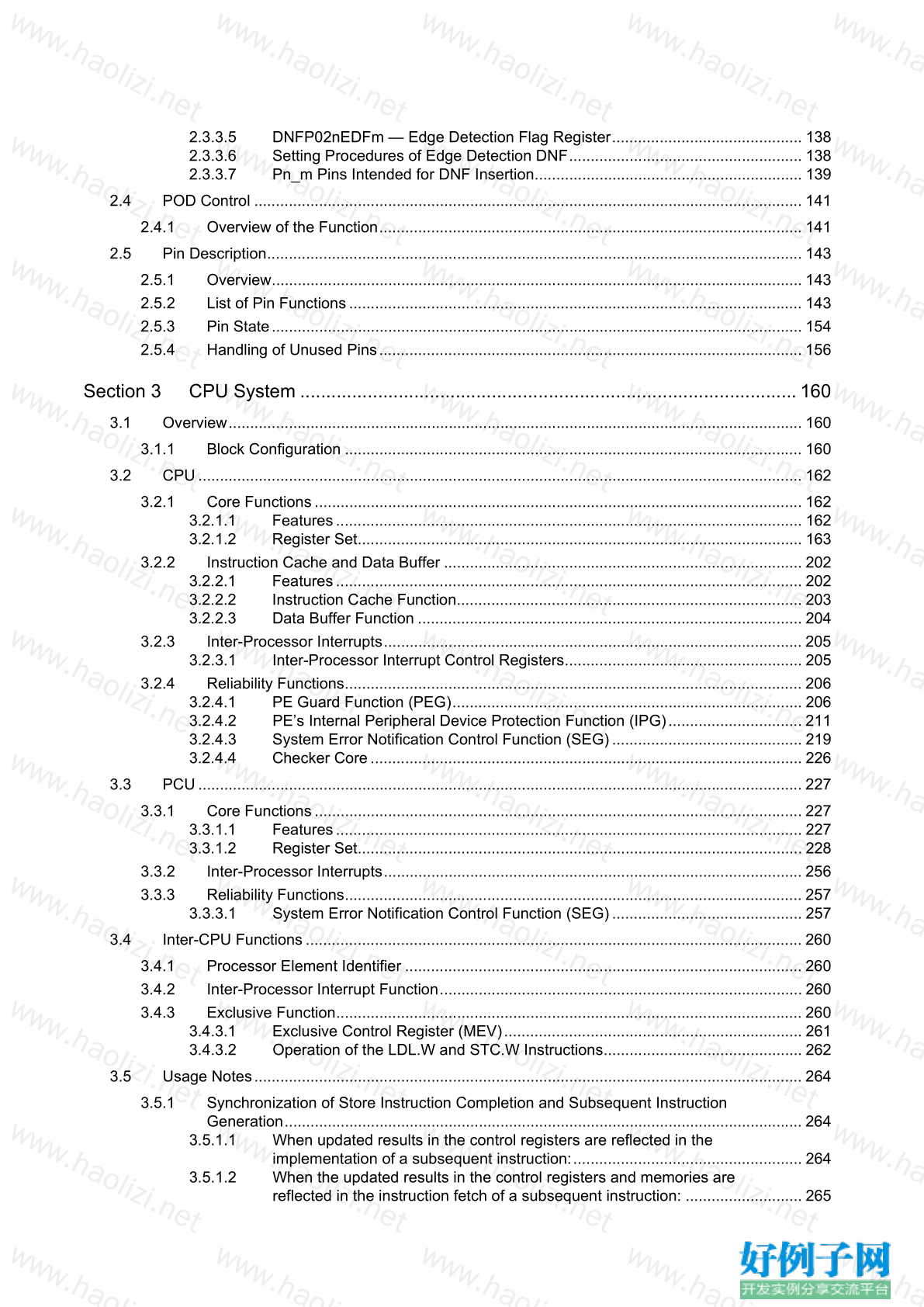

Section 3 CPU System ................................................................................................ 160

3.1 Overview..................................................................................................................................... 160

3.1.1 Block Configuration .......................................................................................................... 160

3.2 CPU ............................................................................................................................................ 162

3.2.1 Core Functions ................................................................................................................. 162

3.2.1.1 Features ............................................................................................................ 162

3.2.1.2 Register Set....................................................................................................... 163

3.2.2 Instruction Cache and Data Buffer ................................................................................... 202

3.2.2.1 Features ............................................................................................................ 202

3.2.2.2 Instruction Cache Function................................................................................ 203

3.2.2.3 Data Buffer Function ......................................................................................... 204

3.2.3 Inter-Processor Interrupts................................................................................................. 205

3.2.3.1 Inter-Processor Interrupt Control Registers....................................................... 205

3.2.4 Reliability Functions.......................................................................................................... 206

3.2.4.1 PE Guard Function (PEG)................................................................................. 206

3.2.4.2 PE’s Internal Peripheral Device Protection Function (IPG)............................... 211

3.2.4.3 System Error Notification Control Function (SEG) ............................................ 219

3.2.4.4 Checker Core .................................................................................................... 226

3.3 PCU ............................................................................................................................................ 227

3.3.1 Core Functions ................................................................................................................. 227

3.3.1.1 Features ............................................................................................................ 227

3.3.1.2 Register Set....................................................................................................... 228

3.3.2 Inter-Processor Interrupts................................................................................................. 256

3.3.3 Reliability Functions.......................................................................................................... 257

3.3.3.1 System Error Notification Control Function (SEG) ............................................ 257

3.4 Inter-CPU Functions ................................................................................................................... 260

3.4.1 Processor Element Identifier ............................................................................................ 260

3.4.2 Inter-Processor Interrupt Function.................................................................................... 260

3.4.3 Exclusive Function............................................................................................................ 260

3.4.3.1 Exclusive Control Register (MEV)..................................................................... 261

3.4.3.2 Operation of the LDL.W and STC.W Instructions.............................................. 262

3.5 Usage Notes............................................................................................................................... 264

3.5.1 Synchronization of Store Instruction Completion and Subsequent Instruction

Generation........................................................................................................................ 264

3.5.1.1 When updated results in the control registers are reflected in the

implementation of a subsequent instruction:..................................................... 264

3.5.1.2 When the updated results in the control registers and memories are

reflected in the instruction fetch of a subsequent instruction: ........................... 2653.5.1.3 When switching the code flash area.................................................................. 265

3.5.1.4 When executing the SYNCM instruction to wait for the completion of

update by the store instruction .......................................................................... 265

3.5.2 Accesses to Registers by Bit-Manipulation Instructions................................................... 266

3.5.3 Ensuring Coherency after Code Flash Programming....................................................... 266

3.5.4 Overwriting Context when Acknowledging Multiple Exceptions ....................................... 266

3.5.5 Usage Notes on Prefetching............................................................................................. 267

Section 4 Address Space............................................................................................. 268

4.1 Address Space ........................................................................................................................... 268

4.2 Address Space Viewed from Each Bus Master.......................................................................... 269

4.2.1 Space in which instructions can be fetched...................................................................... 269

4.2.2 Data space accessible by PE1......................................................................................... 269

4.2.3 Data space accessible by PCU ........................................................................................ 269

4.2.4 Data space accessible by DMA (DMAC, DTS)................................................................. 269

4.3 Global RAM and Retention RAM................................................................................................ 271

Section 5 Operating Mode ........................................................................................... 272

5.1 Features...................................................................................................................................... 272

5.2 Operating Mode.......................................................................................................................... 272

5.2.1 User Boot Mode................................................................................................................ 272

5.2.2 Serial Programming Mode................................................................................................ 272

5.2.3 Boundary Scan Mode....................................................................................................... 272

Section 6 Interrupt........................................................................................................ 273

6.1 Overview..................................................................................................................................... 273

6.2 Register Specifications ............................................................................................................... 275

6.2.1 Register Configuration...................................................................................................... 275

6.2.2 EIC0 to EIC511 — EI Level Interrupt Control Registers 0 to 511..................................... 277

6.2.3 IMR0 to IMR15 — EI Level Interrupt Mask Registers 0 to 15........................................... 279

6.2.4 EIBD0 to EIBD511 — EI Level Interrupt Bind Registers 0 to 511 .................................... 280

6.2.5 NMICTL — NMI Interrupt Control Register....................................................................... 281

6.2.6 EXINTCTL — External Interrupt Control Register............................................................ 282

6.2.7 EXINTSTR — External Interrupt Status Register............................................................. 283

6.2.8 EXINTSTC — External Interrupt Status Clear Register ................................................... 284

6.2.9 SINTR0 to SINTR3 — Software Interrupt Registers......................................................... 285

6.2.10 PINT0 to PINT7, PINTCLR0 to PINTCLR7 — Peripheral Interrupt Status Registers

and Peripheral Interrupt Status Clear Registers............................................................... 286

6.2.11 TIMER — Timer Interrupt Mask Enable Register............................................................. 290

6.3 Interrupt Sources ........................................................................................................................ 292

6.3.1 NMI Interrupts................................................................................................................... 292

6.3.2 IRQ Interrupts................................................................................................................... 292

6.3.3 ECM Interrupts ................................................................................................................. 292

6.3.4 Inter-Processor Interrupts................................................................................................. 292

6.3.5 Software Interrupts ........................................................................................................... 2936.3.6 On-Chip Peripheral Module Interrupts.............................................................................. 293

6.4 Interrupt Exception Handler and Priority Operations .................................................................. 294

6.5 Operation.................................................................................................................................... 308

6.5.1 External Interrupts (NMI/IRQ)........................................................................................... 308

6.5.2 Inter-Processor Interrupt................................................................................................... 308

6.5.3 Software Interrupt............................................................................................................. 308

6.5.4 DTS Interrupt Merge Function.......................................................................................... 308

6.5.5 ATU-IV/TSG2 Merge Function ......................................................................................... 309

6.5.6 Interrupt Processing Flow................................................................................................. 310

6.5.6.1 NMI Processing Flow ........................................................................................ 310

6.5.6.2 External Interrupt Processing Flow ................................................................... 311

6.5.6.3 Inter-Processor Interrupt Flow........................................................................... 313

6.5.6.4 Software Interrupt Processing Flow .................................................................. 314

6.5.6.5 DTS Interrupt Processing Flow ......................................................................... 316

6.6 Interrupt Response Times .......................................................................................................... 318

6.7 Using Interrupt Request Signals to Initiate Data Transfer .......................................................... 319

Section 7 DMA............................................................................................................. 320

7.1 Overview..................................................................................................................................... 320

7.1.1 Overview........................................................................................................................... 320

7.1.2 Term Definition ................................................................................................................. 321

7.2 DMA Function............................................................................................................................. 322

7.2.1 Basic Operation of DMA Transfer..................................................................................... 322

7.2.1.1 Transfer Mode................................................................................................... 322

7.2.1.2 Executing a DMA Cycle..................................................................................... 322

7.2.1.3 Updating Transfer Information........................................................................... 322

7.2.1.4 Last Transfer and Address Reload Transfer ..................................................... 323

7.2.1.5 Transfer Completion Interrupt and Transfer Count Match Interrupt Outputs..... 324

7.2.1.6 Continuous Transfer.......................................................................................... 324

7.2.2 Channel Priority Order...................................................................................................... 326

7.2.2.1 DMAC Channel Arbitration................................................................................ 326

7.2.2.2 DTS Channel Arbitration ................................................................................... 327

7.2.2.3 Interface Arbitration........................................................................................... 328

7.2.3 Reload Function ............................................................................................................... 329

7.2.3.1 Overview of the Reload Function ...................................................................... 329

7.2.3.2 Operation of Reload Function 1 ........................................................................ 329

7.2.3.3 Reload Function 2 ............................................................................................. 330

7.2.3.4 Timing of Setting DMAC Reload Registers ....................................................... 332

7.2.3.5 Timing of Setting DTS Reload Registers........................................................... 332

7.2.4 Chain Function ................................................................................................................. 333

7.2.4.1 Overview ........................................................................................................... 333

7.2.4.2 Setting Up the Chain Function .......................................................................... 334

7.2.4.3 Caution for Using the Chain Function ............................................................... 334

7.2.5 DMAC Operation .............................................................................................................. 335

7.2.5.1 Types of DMA Transfer Requests and Assigning DMA Transfer Requests...... 335

7.2.5.2 Generating and Accepting a Software DMA Transfer Request......................... 335

7.2.6 DTS Operation.................................................................................................................. 336

7.2.6.1 Types of DMA Transfer Requests and Assigning DMA Transfer Requests...... 336

7.2.6.2 Generating and Accepting a DMA Transfer Request........................................ 336

7.2.6.3 Executing DMA Transfer ................................................................................... 336

7.2.6.4 DTSRAM Access............................................................................................... 3377.3 Suspending, Resuming, and Aborting DMA Transfer and Clearing the DMA Transfer

Request ...................................................................................................................................... 338

7.3.1 Suspending and Resuming DMA Transfer by Software Control ...................................... 338

7.3.2 Suspending, Resuming, and Aborting Transfer by a DMAC Channel.............................. 338

7.3.3 Suspending, Resuming, and Aborting Transfer by the DTS............................................. 339

7.3.4 Masking and Clearing a Hardware DMA Transfer Request by the DTFR ........................ 341

7.3.5 Masking and Clearing a Hardware DMA Transfer Request by the DTSFSL.................... 341

7.3.6 List of Functions for Suspending, Resuming, and Aborting Transfer ............................... 342

7.4 Error Control ............................................................................................................................... 343

7.4.1 Type of Error..................................................................................................................... 343

7.4.2 DMA Transfer Error .......................................................................................................... 343

7.4.2.1 Operation of a DMAC When DMA Transfer Error Occurs................................. 343

7.4.2.2 Operation of a DTS When DMA Transfer Error Occurs .................................... 343

7.4.3 DTSRAM Error ................................................................................................................. 344

7.5 Reliability Function...................................................................................................................... 345

7.5.1 Overview........................................................................................................................... 345

7.5.2 Register Access Protection Function................................................................................ 345

7.5.2.1 Identifying the Accessing Master....................................................................... 345

7.5.2.2 Master Access................................................................................................... 345

7.5.2.3 Channel Assignment ......................................................................................... 345

7.5.2.4 Illegal Access .................................................................................................... 346

7.5.3 Master Information Inherit Function.................................................................................. 346

7.5.4 Other Reliability Functions................................................................................................ 347

7.5.4.1 Restriction on the Next Channel in the Chain ................................................... 347

7.6 Setting Up DMA Transfer............................................................................................................ 348

7.6.1 Overview of Setting Up DMA............................................................................................ 348

7.6.2 Setting Up the Overall DMA Operation............................................................................. 350

7.6.3 Setting Up the DMA Channel Setting ............................................................................... 350

7.6.3.1 Setting Up the DMAC Channel Setting ............................................................. 351

7.6.3.2 Setting Up the DTS Channel Setting................................................................. 352

7.7 DMA Trigger Source................................................................................................................... 353

7.7.1 List of DMA Trigger Sources ............................................................................................ 353

7.8 DTS Trigger Source.................................................................................................................... 357

7.8.1 List of DTS Trigger Sources ............................................................................................. 357

7.9 Global Register........................................................................................................................... 361

7.9.1 List of Global Register Addresses .................................................................................... 361

7.9.2 Details of Global Registers............................................................................................... 362

7.9.2.1 DMACTL — DMA Control Register................................................................... 362

7.9.2.2 DTSCTL1 — DTS Control Register 1................................................................ 363

7.9.2.3 DTSCTL2 — DTS Control Register 2................................................................ 364

7.9.2.4 DTSSTS — DTS Status Register...................................................................... 365

7.9.2.5 DMACER — DMAC Error Register ................................................................... 366

7.9.2.6 DTSER1 — DTS Error Register 1..................................................................... 367

7.9.2.7 DTSER2 — DTS Error Register 2..................................................................... 368

7.9.2.8 DTSERC — DTS Error Clear Register.............................................................. 369

7.9.2.9 DM0CMV — DMAC0 Register Access Protection Violation Register ............... 370

7.9.2.10 DTSCMV — DTS Register Access Protection Violation Register..................... 371

7.9.2.11 CMVC — Register Access Protection Violation Clear Register ........................ 372

7.9.2.12 DTSPRn — DTS Channel Priority Setting Register (n = 0 to 7)........................ 3737.9.2.13 DTRECCTL — DTSRAM ECC Control Register............................................... 377

7.9.2.14 DTRERINT — DTSRAM Error Notification Control Register............................. 378

7.9.2.15 DTRTSCTL — DTSRAM Test Control Register................................................ 379

7.9.2.16 DTRTWDAT — DTSRAM Test Write Data Register......................................... 380

7.9.2.17 DTRTRDAT — DTSRAM Test Read Data Register.......................................... 381

7.9.2.18 DMnnCM — DMAC Channel Master Setting Register (nn = 00 to 07) ............. 382

7.9.2.19 DTSnnnCM — DTS Channel Master Setting Register (nnn = 000 to 127) ....... 383

7.10 DMAC Channel Register ............................................................................................................ 385

7.10.1 DMAC Channel Register Address.................................................................................... 385

7.10.2 Details of DMAC Channel Registers ................................................................................ 386

7.10.2.1 DSAn — DMAC Source Address Register........................................................ 386

7.10.2.2 DDAn — DMAC Destination Address Register................................................. 387

7.10.2.3 DTCn — DMAC Transfer Count Register ......................................................... 388

7.10.2.4 DTCTn — DMAC Transfer Control Register ..................................................... 389

7.10.2.5 DRSAn — DMAC Reload Source Address Register......................................... 392

7.10.2.6 DRDAn — DMAC Reload Destination Address Register.................................. 393

7.10.2.7 DRTCn — DMAC Reload Transfer Count Register .......................................... 394

7.10.2.8 DTCCn — DMAC Transfer Count Compare Register....................................... 395

7.10.2.9 DCENn — DMAC Channel Operation Enable Setting Register........................ 396

7.10.2.10 DCSTn — DMAC Transfer Status Register ...................................................... 397

7.10.2.11 DCSTSn — DMAC Transfer Status Set Register.............................................. 399

7.10.2.12 DCSTCn — DMAC Transfer Status Clear Register .......................................... 400

7.10.2.13 DTFRn — DTFR Setting Register..................................................................... 401

7.10.2.14 DTFRRQn — DTFR Transfer Request Status Register.................................... 402

7.10.2.15 DTFRRQCn — DTFR Transfer Request Clear Register................................... 403

7.11 DTS Channel Register................................................................................................................ 404

7.11.1 Transfer information of the DTS (TI)................................................................................. 404

7.11.1.1 Structure of the TI.............................................................................................. 404

7.11.1.2 Organization of the TI in the DTSRAM.............................................................. 405

7.11.1.3 Accessing the TI................................................................................................ 406

7.11.1.4 Caution about accessing the TI......................................................................... 406

7.11.2 DTS Channel Register Address ....................................................................................... 407

7.11.3 Details of DTS Channel Registers.................................................................................... 408

7.11.3.1 DTSAnnn — DTS Source Address Register..................................................... 408

7.11.3.2 DTDAnnn — DTS Destination Address Register .............................................. 409

7.11.3.3 DTTCnnn — DTS Transfer Count Register....................................................... 410

7.11.3.4 DTTCTnnn — DTS Transfer Control Register .................................................. 411

7.11.3.5 DTRSAnnn — DTS Reload Source Address Register...................................... 414

7.11.3.6 DTRDAnnn — DTS Reload Destination Address Register ............................... 415

7.11.3.7 DTRTCnnn — DTS Reload Transfer Count Register........................................ 416

7.11.3.8 DTTCCnnn — DTS Transfer Count Compare Register .................................... 417

7.11.3.9 DTFSLnnn — DTSFSL Operation Setting Register .......................................... 418

7.11.3.10 DTFSTnnn — DTSFSL Transfer Request Status Register............................... 419

7.11.3.11 DTFSSnnn — DTSFSL Transfer Request Set Register.................................... 420

7.11.3.12 DTFSCnnn — DTSFSL Transfer Request Clear Register ................................ 420

Section 8 Resets.......................................................................................................... 421

8.1 Features...................................................................................................................................... 421

8.2 Reset State................................................................................................................................. 422

8.2.1 External Reset State......................................................................................................... 422

8.2.2 Internal Reset State.......................................................................................................... 422

8.3 Reset Sources ............................................................................................................................ 423

8.4 Register Specifications ............................................................................................................... 4248.4.1 List of Registers................................................................................................................ 424

8.4.2 RESF — Reset Source Determination Register............................................................... 425

8.4.3 RESFC — Reset Source Clear Register.......................................................................... 426

8.4.4 POF — Power-On Clear Flag Register ............................................................................ 427

8.4.5 POFC — Power-On Clear Flag Clear Register ................................................................ 427

8.4.6 SWRESA — Software Reset Request Register............................................................... 428

8.5 Software Reset ........................................................................................................................... 429

8.6 RAM Retention ........................................................................................................................... 429

8.7 Usage Notes............................................................................................................................... 429

Section 9 Power Supply Circuit.................................................................................... 430

9.1 Features...................................................................................................................................... 430

9.2 Example of Connection of Power Management IC..................................................................... 431

9.3 Power-on Sequence ................................................................................................................... 432

9.4 Usage Notes............................................................................................................................... 432

9.5 Guide to Mounting on Boards with an EPT................................................................................. 433

9.5.1 QFP .................................................................................................................................. 433

9.5.2 BGA.................................................................................................................................. 435

9.5.3 Reference Information...................................................................................................... 436

Section 10 Power Supply Voltage Monitor..................................................................... 437

10.1 Features...................................................................................................................................... 437

10.2 Configuration .............................................................................................................................. 437

10.3 Register Specifications ............................................................................................................... 438

10.3.1 DETFLG — CVM Detection Flag Register ....................................................................... 439

10.3.2 DETFLGC — CVM Detection Flag Clear Register........................................................... 440

10.3.3 VSCTL — CVM Control Register ..................................................................................... 441

10.3.4 HDETCTL — Upper Limit Voltage Setting Register ......................................................... 442

10.3.5 LDETCTL — Lower Limit Voltage Register...................................................................... 443

10.3.6 VSDETFCTL — Detection Signal Filter Control Register................................................. 444

10.4 Usage ......................................................................................................................................... 445

10.5 Notes on Usage.......................................................................................................................... 447

Section 11 Clock Controller ........................................................................................... 448

11.1 Features...................................................................................................................................... 448

11.2 Type of Clocks............................................................................................................................ 449

11.3 Input/Output Pins........................................................................................................................ 451

11.3.1 How to Connect a Crystal Resonator ............................................................................... 451

11.4 Register Specification................................................................................................................. 452

11.4.1 List of Registers................................................................................................................ 452

11.4.2 PLL0CLKS — PLL0 Status Register ................................................................................ 453

11.4.3 PLL0CLKC1 — PLL0 Control Register 1.......................................................................... 454

11.4.4 CKSC0CTL — Clock 0 Selection Control Register .......................................................... 456

11.4.5 CKSC0ACT — Clock 0 Selection Active Register............................................................ 45711.4.6 CLKD0DIV — Clock 0 Division Register .......................................................................... 458

11.4.7 CLKD0STAT — Clock 0 Division Status Register............................................................ 459

11.4.8 CKSC1CTL — Clock 1 Selection Control Register .......................................................... 460

11.4.9 CKSC1ACT — Clock 1 Selection Active Register............................................................ 461

11.4.10 PROT1PHCMD — Protect 1 Command Register ............................................................ 462

11.4.11 PROT1PS — Protect 1 Status Register ........................................................................... 464

11.5 Operation.................................................................................................................................... 465

11.5.1 Operation When the Divide Function Is Used .................................................................. 465

11.6 Notes .......................................................................................................................................... 468

11.6.1 Board Design Notes ......................................................................................................... 468

11.7 ASIC Clock ................................................................................................................................. 469

11.7.1 Features ........................................................................................................................... 469

11.7.2 Configuration .................................................................................................................... 469

11.7.3 Register Specifications..................................................................................................... 470

11.7.3.1 ACK0CKC — Clock Control Register................................................................ 471

11.7.3.2 ACK0CKCFLG — CKC Flag Register............................................................... 472

11.7.3.3 ACK0CKCTL — Clock Select Register ............................................................. 473

11.7.3.4 ACK0BRGA0CMP — BRGA0 Compare Register............................................. 474

11.7.3.5 ACK0CKCPCMD — CKC Protect Command Register ..................................... 475

11.7.3.6 ACK0CKCPS — CKC Protect Status Register ................................................. 477

11.7.4 Usage ............................................................................................................................... 478

11.7.4.1 CK Pin Output Function..................................................................................... 478

11.7.4.2 CK Output Baud Rate Generator Circuit (BRGA).............................................. 478

11.7.4.3 Control Register Rewrite Protect....................................................................... 479

11.7.4.4 CK Output Switching Procedure........................................................................ 480

Section 12 Standby Controller ....................................................................................... 482

12.1 Features...................................................................................................................................... 482

12.1.1 Types of Power-Down Mode ............................................................................................ 482

12.2 Operation.................................................................................................................................... 483

12.2.1 Power Off Standby Mode ................................................................................................. 483

12.2.2 Module Standby Function................................................................................................. 483

12.3 Register List................................................................................................................................ 484

12.3.1 List of Registers................................................................................................................ 484

12.3.2 EPTCNT — EPT Control Register.................................................................................... 485

12.3.3 PROT0PHCMD — Protection Command Register........................................................... 486

12.3.4 PROT0PS — Protection Command Status Register........................................................ 488

12.3.5 Module Standby Registers ............................................................................................... 489

12.3.5.1 MSRTSG — Module Standby Register – TSG2................................................ 489

12.3.5.2 MSRTAPA — Module Standby Register – TAPA.............................................. 490

12.3.5.3 MSROSTM — Module Standby Register – OSTM............................................ 491

12.3.5.4 MSRWDTA — Module Standby Register – WDTA ........................................... 491

12.3.5.5 MSRPIC — Module Standby Register – PIC .................................................... 492

12.3.5.6 MSRRCAN — Module Standby Register – RS-CAN ........................................ 492

12.3.5.7 MSRRLIN — Module Standby Register – RLIN2.............................................. 493

12.3.5.8 MSRSCI — Module Standby Register – SCI3 .................................................. 494

12.3.5.9 MSRCSIH — Module Standby Register – CSIH ............................................... 495

12.3.5.10 MSRSAD — Module Standby Register – SAR AD............................................ 496

12.3.5.11 MSRDAD — Module Standby Register – ΔΣAD ............................................... 49612.3.5.12 MSRATU — Module Standby Register – ATU-IV ............................................. 497

12.3.5.13 MSRAPA — Module Standby Register – APA.................................................. 497

12.3.5.14 MSRDFE — Module Standby Register – DFE.................................................. 498

12.3.5.15 MSRRHSB — Module Standby Register – RHSB ............................................ 499

12.3.6 MSRPCMD — MSR Protection Command Register ........................................................ 500

12.3.7 MSRPS — MSR Protection Status Register .................................................................... 502

Section 13 Clocked Serial Interface H (CSIH) ............................................................... 503

13.1 CSIH Features............................................................................................................................ 503

13.2 Notes on Pin Combination.......................................................................................................... 505

13.3 Function Overview...................................................................................................................... 506

13.4 List of the Usage Notes .............................................................................................................. 508

13.5 Functional Description ................................................................................................................ 510

13.5.1 Operating Modes (master/slave) ...................................................................................... 511

13.5.2 Master/Slave Connections................................................................................................ 513

13.5.3 Chip Selection (CS) Features........................................................................................... 515

13.5.4 Chip Select Timing Details ............................................................................................... 518

13.5.5 Transmission Clock Selection .......................................................................................... 521

13.5.6 Data transfer modes......................................................................................................... 523

13.5.7 Data Length Selection ...................................................................................................... 524

13.5.8 Serial Data Direction Selection......................................................................................... 527

13.5.9 Communication in Slave Mode......................................................................................... 528

13.5.10 CSIH interrupt requests.................................................................................................... 531

13.5.11 Handshake function.......................................................................................................... 538

13.5.12 Error Detection ................................................................................................................. 540

13.5.13 Loop-Back Mode .............................................................................................................. 544

13.5.14 Enforced Chip Select Idle Setting..................................................................................... 545

13.6 CSIH Control Registers .............................................................................................................. 546

13.6.1 CSIHnCTL0 — CSIH Control Register 0.......................................................................... 547

13.6.2 CSIHnCTL1 — CSIH Control Register 1.......................................................................... 548

13.6.3 CSIHnCTL2 — CSIH Control Register 2.......................................................................... 551

13.6.4 CSIHnSTR0 — CSIH Status Register 0 ........................................................................... 553

13.6.5 CSIHnSTCR0 — CSIH Status Clear Register 0............................................................... 555

13.6.6 CSIHnCFGx — CSIH Configuration Register x................................................................ 556

13.6.7 CSIHnTX0W — CSIH Transmit Data Register 0 for Word Access .................................. 561

13.6.8 CSIHnTX0H — CSIH Transmit Data Register 0 for Half Word Access............................ 563

13.6.9 CSIHnRX0W — CSIH Receive Data Register 0 for Word Access ................................... 564

13.6.10 CSIHnRX0H — CSIH Receive Data Register 0 for Half Word Access ............................ 565

13.6.11 CSIHnBRSi — CSIHn Baud Rate Setting Register i ........................................................ 566

13.7 Operating Procedures................................................................................................................. 567

13.7.1 Procedures in Direct Access Mode .................................................................................. 567

Section 14 Serial Communication Interface 3 (SCI3) .................................................... 571

14.1 Overview..................................................................................................................................... 571

14.1.1 Features of SCI3 .............................................................................................................. 57114.1.2 Outline of Functions.......................................................................................................... 571

14.1.3 Serial Communication Modes........................................................................................... 572

14.1.4 Block Diagram .................................................................................................................. 572

14.2 Input/Output Pins........................................................................................................................ 573

14.3 Register Descriptions.................................................................................................................. 574

14.3.1 SCI3nRSR — Receive Shift Register............................................................................... 575

14.3.2 SCI3nRDR — Receive Data Register .............................................................................. 575

14.3.3 SCI3nTDR — Transmit Data Register.............................................................................. 575

14.3.4 SCI3nTSR — Transmit Shift Register .............................................................................. 575

14.3.5 SCI3nSMR — Serial Mode Register ................................................................................ 576

14.3.6 SCI3nSCR — Serial Control Register .............................................................................. 577

14.3.7 SCI3nSSR — Serial Status Register................................................................................ 579

14.3.8 SCI3nSCMR — Serial Transfer Format Register............................................................. 581

14.3.9 SCI3nSEMR — Serial Extended Mode Register.............................................................. 582

14.3.10 SCI3nBRR — Bit Rate Register ....................................................................................... 583

14.3.11 SCI3nMDDR — Modulation Duty Register....................................................................... 586

14.4 Operation in Asynchronous Mode .............................................................................................. 587

14.4.1 Transmission/Receive Format.......................................................................................... 588

14.4.2 Receive Data Sampling Timing and Receive Margin ....................................................... 589

14.4.3 Clock................................................................................................................................. 590

14.4.4 Double-Speed Operation.................................................................................................. 590

14.4.5 SCI3 Initialization (Asynchronous Mode).......................................................................... 591

14.4.6 Serial Data Transmission (Asynchronous Mode) ............................................................. 592

14.4.7 Serial Data Receive (Asynchronous Mode)...................................................................... 595

14.5 Multi-Processor Communication Function.................................................................................. 599

14.5.1 Overview and Sample Connection ................................................................................... 599

14.5.2 Multi-Processor Serial Data Transmission ....................................................................... 600

14.5.3 Multi-Processor Serial Data Receive................................................................................ 601

14.6 Operation in Clock Synchronous Mode ...................................................................................... 605

14.6.1 Clock................................................................................................................................. 605

14.6.2 SCI3 Initialization (Clock Synchronous Mode) ................................................................. 606

14.6.3 Serial Data Transmission (Clock Synchronous Mode)..................................................... 607

14.6.4 Serial Data Receive (Clock Synchronous Mode) ............................................................. 610

14.6.5 Simultaneous Serial Data Transmission and Reception (Clock Synchronous Mode) ...... 612

14.7

Bit Rate Modulation Function...................................................................................................... 614

14.8 Interrupt Sources ........................................................................................................................ 615

14.9 Usage Notes............................................................................................................................... 616

14.9.1 Break Detection and Processing ...................................................................................... 616

14.9.2 Mark State and Break Output........................................................................................... 616

14.9.3 Receive Error Flags and Transmit Operations in Clock Synchronous Mode ................... 616

14.9.4 Relationship between Writing to SCI3nTDR and the TDRE Flag..................................... 616

14.9.5 Restrictions on Using an External Clock for Transmission in Clock Synchronous

Mode................................................................................................................................. 617

14.9.6 External Clock Input in Clock Synchronous Mode............................................................ 617Section 15 LIN Master Interface (RLIN2)....................................................................... 618

15.1 Overview of RH850/E1L RLIN2.................................................................................................. 618

15.1.1 Units and Channels .......................................................................................................... 618

15.1.2 Register Base Addresses................................................................................................. 618

15.1.3 Clock Supply..................................................................................................................... 619

15.1.4 Interrupt Request.............................................................................................................. 619

15.1.5 Reset Sources.................................................................................................................. 619

15.1.6 External Input/Output Signals........................................................................................... 619

15.2 Function...................................................................................................................................... 620

15.2.1 Functional Overview......................................................................................................... 620

15.2.2 Block Diagram .................................................................................................................. 621

15.3 Registers..................................................................................................................................... 622

15.3.1 List of Registers................................................................................................................ 622

15.3.2 Global Registers............................................................................................................... 623

15.3.2.1 RLN21nGLWBR — LIN Wake-up Baud Rate Select Register.......................... 623

15.3.2.2 RLN21nGLBRP0 — LIN Baud Rate Prescaler 0 Register ................................ 624

15.3.2.3 RLN21nGLBRP1 — LIN Baud Rate Prescaler 1 Register ................................ 625

15.3.2.4 RLN21nGLSTC — LIN Self-Test Control Register............................................ 626

15.3.3 Channel Registers............................................................................................................ 627

15.3.3.1 RLN21nmLiMD — LIN Mode Register .............................................................. 627

15.3.3.2 RLN21nmLiBFC — LIN Break Field Configuration Register............................. 628

15.3.3.3 RLN21nmLiSC — LIN Space Configuration Register ....................................... 629

15.3.3.4 RLN21nmLiWUP — LIN Wake-up Configuration Register................................ 630

15.3.3.5 RLN21nmLiIE — LIN Interrupt Enable Register................................................ 631

15.3.3.6 RLN21nmLiEDE — LIN Error Detection Enable Register................................. 632

15.3.3.7 RLN21nmLiCUC — LIN Control Register ......................................................... 634

15.3.3.8 RLN21nmLiTRC — LIN Transmission Control Register ................................... 635

15.3.3.9 RLN21nmLiMST — LIN Mode Status Register................................................. 636

15.3.3.10 RLN21nmLiST — LIN Status Register.............................................................. 637

15.3.3.11 RLN21nmLiEST — LIN Error Status Register................................................... 639

15.3.3.12 RLN21nmLiDFC — LIN Data Field Configuration Register............................... 641

15.3.3.13 RLN21nmLiIDB — LIN ID Buffer Register......................................................... 643

15.3.3.14 RLN21nmLiCBR — LIN Checksum Buffer Register.......................................... 644

15.3.3.15 RLN21nmLiDBRb — LIN Data Buffer b Register.............................................. 645

15.4 Interrupt Sources ........................................................................................................................ 646

15.5 Modes......................................................................................................................................... 647

15.6 LIN Reset Mode.......................................................................................................................... 649

15.7 LIN Operation Mode ................................................................................................................... 650

15.8 LIN Wake-up Mode..................................................................................................................... 650

15.9 Header Transmission/Response Transmission/Response Reception........................................ 651

15.9.1 Header Transmission ....................................................................................................... 651

15.9.2 Response Transmission................................................................................................... 652

15.9.3 Response Reception ........................................................................................................ 653

15.10 Data Transmission/Reception..................................................................................................... 654

15.10.1 Data Transmission............................................................................................................ 654

15.10.2 Data Reception................................................................................................................. 655

15.11 Transmit/Receive Data Buffering................................................................................................ 656

15.11.1 Transmission of LIN Frames ............................................................................................ 65615.11.2 Reception of LIN Frames.................................................................................................. 657

15.12 Wake-up Transmission/Reception.............................................................................................. 658

15.12.1 Wake-up Transmission..................................................................................................... 658

15.12.2 Wake-up Reception.......................................................................................................... 659

15.12.3 Wakeup Collision.............................................................................................................. 659

15.13 Status.......................................................................................................................................... 660

15.14 Error Status................................................................................................................................. 661

15.14.1 Types of Error Status........................................................................................................ 661

15.14.2 Target Time Area for Error Detection ............................................................................... 662

15.15 LIN Self-Test Mode..................................................................................................................... 663

15.15.1 Change to LIN Self-Test Mode......................................................................................... 664

15.15.2 Transmission in LIN Self-Test Mode ................................................................................ 665

15.15.3 Reception in LIN Self-Test Mode...................................................................................... 666

15.15.4 Terminating LIN Self-Test Mode....................................................................................... 668

15.16 Baud Rate Generator.................................................................................................................. 669

Section 16 CAN Interface (RS-CAN) ............................................................................. 671

16.1 Overview of RS-CAN.................................................................................................................. 671

16.1.1 Number of Units................................................................................................................ 671

16.1.2 Register Base Address..................................................................................................... 671

16.1.3 Clock Supply..................................................................................................................... 672

16.1.4 Interrupt and DMA / DTS.................................................................................................. 672

16.1.5 Reset Sources.................................................................................................................. 673

16.1.6 External I/O Signals.......................................................................................................... 673

16.2 Overview..................................................................................................................................... 674

16.2.1 Functional Outline............................................................................................................. 674

16.2.2 Block Diagram .................................................................................................................. 676

16.3 Register Descriptions.................................................................................................................. 677

16.3.1 Register List...................................................................................................................... 677

16.3.2 Register Details ................................................................................................................ 700

16.3.2.1 RSCAN0CmCFG — Channel Configuration Register (m = 0 to 3) ................... 700

16.3.2.2 RSCAN0CmCTR — Channel Control Register (m = 0 to 3) ............................. 702

16.3.2.3 RSCAN0CmSTS — Channel Status Register (m = 0 to 3) ............................... 706

16.3.2.4 RSCAN0CmERFL — Channel Error Flag Register (m = 0 to 3)....................... 708

16.3.2.5 RSCAN0GCFG — Global Configuration Register............................................. 712

16.3.2.6 RSCAN0GCTR — Global Control Register....................................................... 715

16.3.2.7 RSCAN0GSTS — Global Status Register ........................................................ 717

16.3.2.8 RSCAN0GERFL — Global Error Flag Register ................................................ 719

16.3.2.9 RSCAN0GTINTSTS0 — Global TX Interrupt Status Register 0 ....................... 720

16.3.2.10 RSCAN0GTSC — Global Timestamp Counter Register................................... 723

16.3.2.11 RSCAN0GAFLECTR — Receive Rule Entry Control Register ......................... 724

16.3.2.12 RSCAN0GAFLCFG0 — Receive Rule Configuration Register 0...................... 725

16.3.2.13 RSCAN0GAFLIDj — Receive Rule ID Register (j = 0 to 15)............................. 727

16.3.2.14 RSCAN0GAFLMj — Receive Rule Mask Register (j = 0 to 15) ........................ 728

16.3.2.15 RSCAN0GAFLP0j — Receive Rule Pointer 0 Register (j = 0 to 15) ................. 729

16.3.2.16 RSCAN0GAFLP1j — Receive Rule Pointer 1 Register (j = 0 to 15) ................. 731

16.3.2.17 RSCAN0RMNB — Receive Buffer Number Register........................................ 732

16.3.2.18 RSCAN0RMNDy — Receive Buffer New Data Register y (y = 0, 1)................. 73316.3.2.19 RSCAN0RMIDq — Receive Buffer ID Register (q = 0 to 63)............................ 734

16.3.2.20 RSCAN0RMPTRq — Receive Buffer Pointer Register (q = 0 to 63) ................ 735

16.3.2.21 RSCAN0RMDF0q — Receive Buffer Data Field 0 Register (q = 0 to 63)......... 736

16.3.2.22 RSCAN0RMDF1q — Receive Buffer Data Field 1 Register (q = 0 to 63)......... 737

16.3.2.23 RSCAN0RFCCx — Receive FIFO Buffer Configuration/Control Register

(x = 0 to 7)......................................................................................................... 738

16.3.2.24 RSCAN0RFSTSx — Receive FIFO Buffer Status Register (x = 0 to 7)............ 740

16.3.2.25 RSCAN0RFPCTRx — Receive FIFO Buffer Pointer Control Register

(x = 0 to 7)......................................................................................................... 742

16.3.2.26 RSCAN0RFIDx — Receive FIFO Buffer Access ID Register (x = 0 to 7) ......... 743

16.3.2.27 RSCAN0RFPTRx — Receive FIFO Buffer Access Pointer Register

(x = 0 to 7)......................................................................................................... 744

16.3.2.28 RSCAN0RFDF0x — Receive FIFO Buffer Access Data Field 0 Register

(x = 0 to 7)......................................................................................................... 745

16.3.2.29 RSCAN0RFDF1x — Receive FIFO Buffer Access Data Field 1 Register

(x = 0 to 7)......................................................................................................... 746

16.3.2.30 RSCAN0CFCCk — Transmit/Receive FIFO Buffer Configuration/

Control Register (k = 0 to 11)............................................................................ 747

16.3.2.31 RSCAN0CFSTSk — Transmit/Receive FIFO Buffer Status Register

(k = 0 to 11)....................................................................................................... 751

16.3.2.32 RSCAN0CFPCTRk — Transmit/Receive FIFO Buffer Pointer Control

Register (k = 0 to 11)......................................................................................... 754

16.3.2.33 RSCAN0CFIDk — Transmit/Receive FIFO Buffer Access ID Register

(k = 0 to 11)....................................................................................................... 756

16.3.2.34 RSCAN0CFPTRk — Transmit/Receive FIFO Buffer Access Pointer Register

(k = 0 to 11)....................................................................................................... 758

16.3.2.35 RSCAN0CFDF0k — Transmit/Receive FIFO Buffer Access Data Field 0

Register (k = 0 to 11)......................................................................................... 760

16.3.2.36 RSCAN0CFDF1k — Transmit/Receive FIFO Buffer Access Data Field 1

Register (k = 0 to 11)......................................................................................... 761

16.3.2.37 RSCAN0FESTS — FIFO Empty Status Register.............................................. 762

16.3.2.38 RSCAN0FFSTS — FIFO Full Status Register .................................................. 764

16.3.2.39 RSCAN0FMSTS — FIFO Message Lost Status Register................................. 766

16.3.2.40 RSCAN0RFISTS — Receive FIFO Buffer Interrupt Flag Status Register......... 768

16.3.2.41 RSCAN0CFRISTS — Transmit/Receive FIFO Buffer Reception Interrupt

Flag Status Register.......................................................................................... 769

16.3.2.42 RSCAN0CFTISTS — Transmit/Receive FIFO Buffer Transmission Interrupt

Flag Status Register.......................................................................................... 770

16.3.2.43 RSCAN0TMCp — Transmit Buffer Control Register (p = 0 to 63) .................... 771

16.3.2.44 RSCAN0TMSTSp — Transmit Buffer Status Register (p = 0 to 63) ................. 773

16.3.2.45 RSCAN0TMTRSTSy — Transmit Buffer Transmit Request Status Register y

(y = 0, 1)............................................................................................................ 775

16.3.2.46 RSCAN0TMTARSTSy — Transmit Buffer Transmit Abort Request Status

Register (y = 0, 1).............................................................................................. 777

16.3.2.47 RSCAN0TMTCSTSy — Transmit Buffer Transmit Complete Status Register

(y = 0, 1)............................................................................................................ 779

16.3.2.48 RSCAN0TMTASTSy — Transmit Buffer Transmit Abort Status Register

(y = 0, 1)............................................................................................................ 781

16.3.2.49 RSCAN0TMIECy — Transmit Buffer Interrupt Enable Configuration Register

(y = 0, 1)............................................................................................................ 783

16.3.2.50 RSCAN0TMIDp — Transmit Buffer ID Register (p = 0 to 63) ........................... 785

16.3.2.51 RSCAN0TMPTRp — Transmit Buffer Pointer Register (p = 0 to 63)................ 786

16.3.2.52 RSCAN0TMDF0p — Transmit Buffer Data Field 0 Register (p = 0 to 63) ........ 787

16.3.2.53 RSCAN0TMDF1p — Transmit Buffer Data Field 1 Register (p = 0 to 63) ........ 788

16.3.2.54 RSCAN0TXQCCm — Transmit Queue Configuration/Control Register

(m = 0 to 3)........................................................................................................ 789

16.3.2.55 RSCAN0TXQSTSm — Transmit Queue Status Register (m = 0 to 3).............. 79116.3.2.56 RSCAN0TXQPCTRm — Transmit Queue Pointer Control Register

(m = 0 to 3)........................................................................................................ 793

16.3.2.57 RSCAN0THLCCm — Transmit History List Configuration/Control Register

(m = 0 to 3)........................................................................................................ 794

16.3.2.58 RSCAN0THLSTSm — Transmit History List Status Register (m = 0 to 3) ....... 796

16.3.2.59 RSCAN0THLACCm — Transmit History List Access Register (m = 0 to 3) ..... 798

16.3.2.60 RSCAN0THLPCTRm — Transmit History List Pointer Control Register

(m = 0 to 3)........................................................................................................ 799

16.3.2.61 RSCAN0GTSTCFG — Global Test Configuration Register.............................. 800

16.3.2.62 RSCAN0GTSTCTR — Global Test Control Register........................................ 802

16.3.2.63 RSCAN0GLOCKK — Global Lock Key Register............................................... 803

16.3.2.64 RSCAN0RPGACCr — RAM Test Page Access Register (r = 0 to 63) ............. 804

16.4 Functions .................................................................................................................................... 805

16.4.1 Interrupt Sources.............................................................................................................. 805

16.4.2 CAN Modes ...................................................................................................................... 809

16.4.2.1 Global Modes .................................................................................................... 809

16.4.2.2 Global Stop Mode.............................................................................................. 810

16.4.2.3 Global Reset Mode............................................................................................ 810