实例介绍

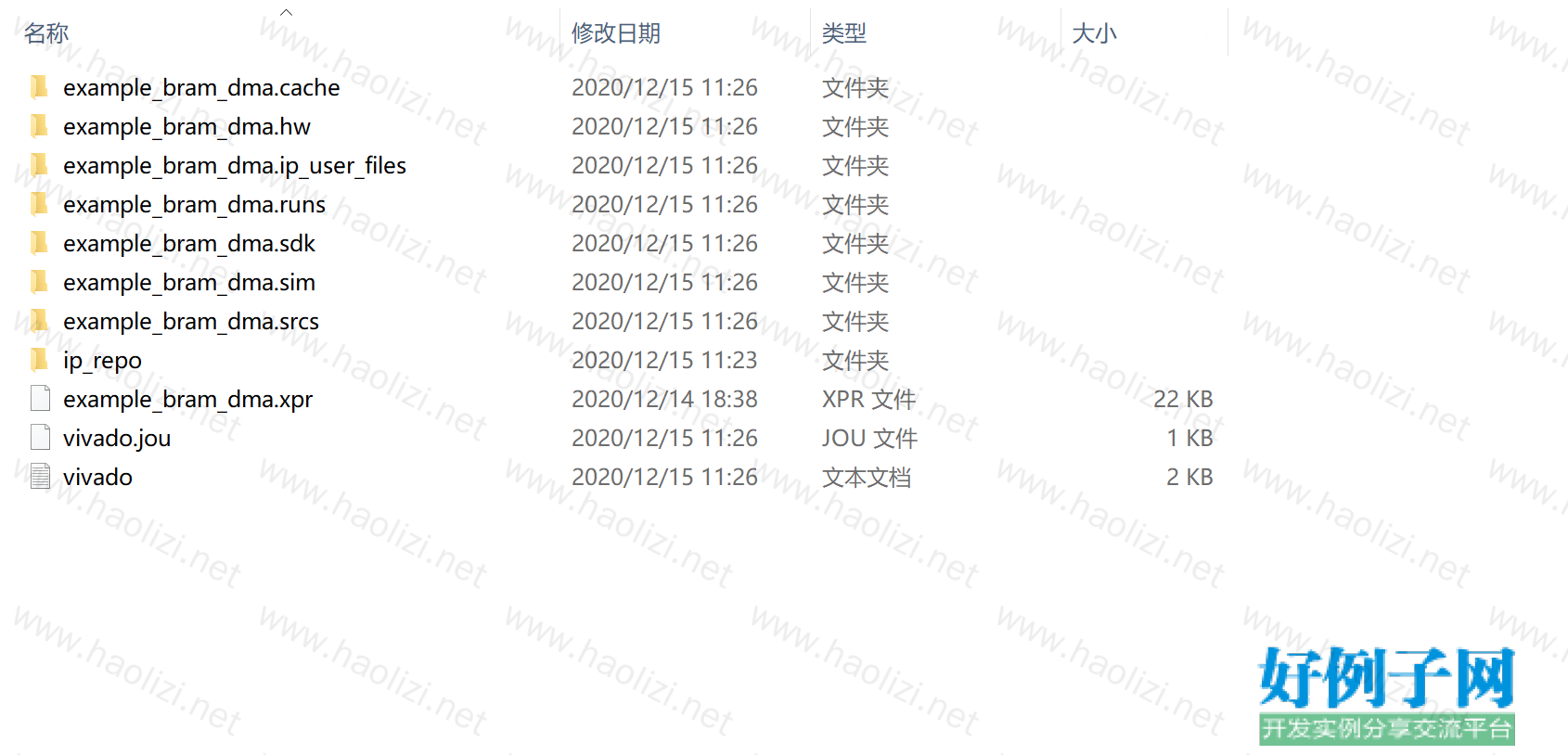

【实例截图】

【核心代码】

.

└── example_bram_dma

├── example_bram_dma.cache

│ ├── compile_simlib

│ │ ├── activehdl

│ │ ├── ies

│ │ ├── modelsim

│ │ ├── questa

│ │ ├── riviera

│ │ ├── vcs

│ │ └── xcelium

│ ├── ip

│ │ └── 2018.3

│ │ ├── 1231bce321126d9e

│ │ │ ├── 1231bce321126d9e.xci

│ │ │ ├── stats.txt

│ │ │ ├── system_axis_data_fifo_0_0.dcp

│ │ │ ├── system_axis_data_fifo_0_0_sim_netlist.v

│ │ │ ├── system_axis_data_fifo_0_0_sim_netlist.vhdl

│ │ │ ├── system_axis_data_fifo_0_0_stub.v

│ │ │ └── system_axis_data_fifo_0_0_stub.vhdl

│ │ ├── 1f9dce0fb4e96605

│ │ │ ├── 1f9dce0fb4e96605.xci

│ │ │ ├── system_xbar_0.dcp

│ │ │ ├── system_xbar_0_sim_netlist.v

│ │ │ ├── system_xbar_0_sim_netlist.vhdl

│ │ │ ├── system_xbar_0_stub.v

│ │ │ └── system_xbar_0_stub.vhdl

│ │ ├── 358b79ec8b33a7bc

│ │ │ ├── 358b79ec8b33a7bc.xci

│ │ │ ├── system_axi_dma_0_0.dcp

│ │ │ ├── system_axi_dma_0_0_sim_netlist.v

│ │ │ ├── system_axi_dma_0_0_sim_netlist.vhdl

│ │ │ ├── system_axi_dma_0_0_stub.v

│ │ │ └── system_axi_dma_0_0_stub.vhdl

│ │ ├── 4811d563bbc3979d

│ │ │ ├── 4811d563bbc3979d.xci

│ │ │ ├── system_system_ila_0_0.dcp

│ │ │ ├── system_system_ila_0_0_sim_netlist.v

│ │ │ ├── system_system_ila_0_0_sim_netlist.vhdl

│ │ │ ├── system_system_ila_0_0_stub.v

│ │ │ └── system_system_ila_0_0_stub.vhdl

│ │ ├── 5228946293ee29e3

│ │ │ ├── 5228946293ee29e3.xci

│ │ │ ├── stats.txt

│ │ │ ├── system_processing_system7_0_0.dcp

│ │ │ ├── system_processing_system7_0_0_sim_netlist.v

│ │ │ ├── system_processing_system7_0_0_sim_netlist.vhdl

│ │ │ ├── system_processing_system7_0_0_stub.v

│ │ │ └── system_processing_system7_0_0_stub.vhdl

│ │ ├── 6fc2d08344873b94

│ │ │ ├── 6fc2d08344873b94.xci

│ │ │ ├── stats.txt

│ │ │ ├── system_blk_mem_gen_0_0.dcp

│ │ │ ├── system_blk_mem_gen_0_0_sim_netlist.v

│ │ │ ├── system_blk_mem_gen_0_0_sim_netlist.vhdl

│ │ │ ├── system_blk_mem_gen_0_0_stub.v

│ │ │ └── system_blk_mem_gen_0_0_stub.vhdl

│ │ ├── 7cebfd8c06fbca3d

│ │ │ ├── 7cebfd8c06fbca3d.xci

│ │ │ ├── system_axi_smc_0.dcp

│ │ │ ├── system_axi_smc_0_sim_netlist.v

│ │ │ ├── system_axi_smc_0_sim_netlist.vhdl

│ │ │ ├── system_axi_smc_0_stub.v

│ │ │ └── system_axi_smc_0_stub.vhdl

│ │ ├── 7d7c7a2f1e6f208a

│ │ │ ├── 7d7c7a2f1e6f208a.xci

│ │ │ ├── system_system_ila_0_0.dcp

│ │ │ ├── system_system_ila_0_0_sim_netlist.v

│ │ │ ├── system_system_ila_0_0_sim_netlist.vhdl

│ │ │ ├── system_system_ila_0_0_stub.v

│ │ │ └── system_system_ila_0_0_stub.vhdl

│ │ ├── 88729755e9249c80

│ │ │ ├── 88729755e9249c80.xci

│ │ │ ├── system_system_ila_0_0.dcp

│ │ │ ├── system_system_ila_0_0_sim_netlist.v

│ │ │ ├── system_system_ila_0_0_sim_netlist.vhdl

│ │ │ ├── system_system_ila_0_0_stub.v

│ │ │ └── system_system_ila_0_0_stub.vhdl

│ │ ├── 8c52b4c5e0f9853f

│ │ │ ├── 8c52b4c5e0f9853f.xci

│ │ │ ├── stats.txt

│ │ │ ├── system_auto_pc_2.dcp

│ │ │ ├── system_auto_pc_2_sim_netlist.v

│ │ │ ├── system_auto_pc_2_sim_netlist.vhdl

│ │ │ ├── system_auto_pc_2_stub.v

│ │ │ └── system_auto_pc_2_stub.vhdl

│ │ ├── 9778ebf57c8c7e80

│ │ │ ├── 9778ebf57c8c7e80.xci

│ │ │ ├── stats.txt

│ │ │ ├── system_rst_ps7_0_100M_0.dcp

│ │ │ ├── system_rst_ps7_0_100M_0_sim_netlist.v

│ │ │ ├── system_rst_ps7_0_100M_0_sim_netlist.vhdl

│ │ │ ├── system_rst_ps7_0_100M_0_stub.v

│ │ │ └── system_rst_ps7_0_100M_0_stub.vhdl

│ │ ├── 97b51a3b79499bef

│ │ │ ├── 97b51a3b79499bef.xci

│ │ │ ├── stats.txt

│ │ │ ├── system_axi_bram_ctrl_0_0.dcp

│ │ │ ├── system_axi_bram_ctrl_0_0_sim_netlist.v

│ │ │ ├── system_axi_bram_ctrl_0_0_sim_netlist.vhdl

│ │ │ ├── system_axi_bram_ctrl_0_0_stub.v

│ │ │ └── system_axi_bram_ctrl_0_0_stub.vhdl

│ │ ├── b3f3d11d78802036

│ │ │ ├── b3f3d11d78802036.xci

│ │ │ ├── stats.txt

│ │ │ ├── system_bram_rd_0_0.dcp

│ │ │ ├── system_bram_rd_0_0_sim_netlist.v

│ │ │ ├── system_bram_rd_0_0_sim_netlist.vhdl

│ │ │ ├── system_bram_rd_0_0_stub.v

│ │ │ └── system_bram_rd_0_0_stub.vhdl

│ │ ├── b5b762810d755dc6

│ │ │ ├── b5b762810d755dc6.xci

│ │ │ ├── dbg_hub.dcp

│ │ │ ├── dbg_hub_sim_netlist.v

│ │ │ ├── dbg_hub_sim_netlist.vhdl

│ │ │ ├── dbg_hub_stub.v

│ │ │ ├── dbg_hub_stub.vhdl

│ │ │ └── stats.txt

│ │ ├── c22c0800449b1179

│ │ │ ├── c22c0800449b1179.xci

│ │ │ ├── stats.txt

│ │ │ ├── system_auto_pc_0.dcp

│ │ │ ├── system_auto_pc_0_sim_netlist.v

│ │ │ ├── system_auto_pc_0_sim_netlist.vhdl

│ │ │ ├── system_auto_pc_0_stub.v

│ │ │ └── system_auto_pc_0_stub.vhdl

│ │ └── f2f2af29c80cf5f6

│ │ ├── f2f2af29c80cf5f6.xci

│ │ ├── stats.txt

│ │ ├── system_xbar_0.dcp

│ │ ├── system_xbar_0_sim_netlist.v

│ │ ├── system_xbar_0_sim_netlist.vhdl

│ │ ├── system_xbar_0_stub.v

│ │ └── system_xbar_0_stub.vhdl

│ └── wt

│ ├── gui_handlers.wdf

│ ├── java_command_handlers.wdf

│ ├── project.wpc

│ ├── synthesis.wdf

│ ├── synthesis_details.wdf

│ └── webtalk_pa.xml

├── example_bram_dma.hw

│ ├── backup

│ │ └── hw_ila_data_1.ila

│ ├── example_bram_dma.lpr

│ └── hw_1

│ ├── hw.xml

│ ├── layout

│ └── wave

│ └── hw_ila_data_1

│ ├── hw_ila_data_1.wcfg

│ └── hw_ila_data_1.wdb

├── example_bram_dma.ip_user_files

│ ├── README.txt

│ ├── bd

│ │ └── system

│ │ ├── ip

│ │ │ ├── system_auto_pc_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_auto_pc_0.v

│ │ │ │ ├── system_auto_pc_0_sim_netlist.v

│ │ │ │ └── system_auto_pc_0_sim_netlist.vhdl

│ │ │ ├── system_auto_pc_1

│ │ │ │ ├── sim

│ │ │ │ │ └── system_auto_pc_1.v

│ │ │ │ ├── system_auto_pc_1_sim_netlist.v

│ │ │ │ └── system_auto_pc_1_sim_netlist.vhdl

│ │ │ ├── system_auto_pc_2

│ │ │ │ ├── sim

│ │ │ │ │ └── system_auto_pc_2.v

│ │ │ │ ├── system_auto_pc_2_sim_netlist.v

│ │ │ │ └── system_auto_pc_2_sim_netlist.vhdl

│ │ │ ├── system_axi_bram_ctrl_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_axi_bram_ctrl_0_0.vhd

│ │ │ │ ├── system_axi_bram_ctrl_0_0_sim_netlist.v

│ │ │ │ └── system_axi_bram_ctrl_0_0_sim_netlist.vhdl

│ │ │ ├── system_axi_dma_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_axi_dma_0_0.vhd

│ │ │ │ ├── system_axi_dma_0_0_sim_netlist.v

│ │ │ │ └── system_axi_dma_0_0_sim_netlist.vhdl

│ │ │ ├── system_axi_smc_0

│ │ │ │ ├── bd_0

│ │ │ │ │ ├── bd_44e3.bd

│ │ │ │ │ ├── ip

│ │ │ │ │ │ ├── ip_0

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ ├── bd_44e3_one_0.h

│ │ │ │ │ │ │ ├── bd_44e3_one_0.v

│ │ │ │ │ │ │ └── xlconstant_v1_1_5.h

│ │ │ │ │ │ ├── ip_1

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_psr_aclk_0.vhd

│ │ │ │ │ │ ├── ip_10

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_s00a2s_0.sv

│ │ │ │ │ │ ├── ip_11

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_sarn_0.sv

│ │ │ │ │ │ ├── ip_12

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_srn_0.sv

│ │ │ │ │ │ ├── ip_13

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_s01mmu_0.sv

│ │ │ │ │ │ ├── ip_14

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_s01tr_0.sv

│ │ │ │ │ │ ├── ip_15

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_s01sic_0.sv

│ │ │ │ │ │ ├── ip_16

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_s01a2s_0.sv

│ │ │ │ │ │ ├── ip_17

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_sawn_0.sv

│ │ │ │ │ │ ├── ip_18

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_swn_0.sv

│ │ │ │ │ │ ├── ip_19

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_sbn_0.sv

│ │ │ │ │ │ ├── ip_2

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_arsw_0.sv

│ │ │ │ │ │ ├── ip_20

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_m00s2a_0.sv

│ │ │ │ │ │ ├── ip_21

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_m00arn_0.sv

│ │ │ │ │ │ ├── ip_22

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_m00rn_0.sv

│ │ │ │ │ │ ├── ip_23

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_m00awn_0.sv

│ │ │ │ │ │ ├── ip_24

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_m00wn_0.sv

│ │ │ │ │ │ ├── ip_25

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_m00bn_0.sv

│ │ │ │ │ │ ├── ip_26

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_m00e_0.sv

│ │ │ │ │ │ ├── ip_3

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_rsw_0.sv

│ │ │ │ │ │ ├── ip_4

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_awsw_0.sv

│ │ │ │ │ │ ├── ip_5

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_wsw_0.sv

│ │ │ │ │ │ ├── ip_6

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_bsw_0.sv

│ │ │ │ │ │ ├── ip_7

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_s00mmu_0.sv

│ │ │ │ │ │ ├── ip_8

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_44e3_s00tr_0.sv

│ │ │ │ │ │ └── ip_9

│ │ │ │ │ │ └── sim

│ │ │ │ │ │ └── bd_44e3_s00sic_0.sv

│ │ │ │ │ └── sim

│ │ │ │ │ ├── bd_44e3.protoinst

│ │ │ │ │ └── bd_44e3.v

│ │ │ │ ├── sim

│ │ │ │ │ └── system_axi_smc_0.v

│ │ │ │ ├── system_axi_smc_0_sim_netlist.v

│ │ │ │ └── system_axi_smc_0_sim_netlist.vhdl

│ │ │ ├── system_axis_data_fifo_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_axis_data_fifo_0_0.v

│ │ │ │ ├── system_axis_data_fifo_0_0_sim_netlist.v

│ │ │ │ └── system_axis_data_fifo_0_0_sim_netlist.vhdl

│ │ │ ├── system_blk_mem_gen_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_blk_mem_gen_0_0.v

│ │ │ │ ├── system_blk_mem_gen_0_0_sim_netlist.v

│ │ │ │ └── system_blk_mem_gen_0_0_sim_netlist.vhdl

│ │ │ ├── system_bram_rd_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_bram_rd_0_0.v

│ │ │ │ ├── system_bram_rd_0_0_sim_netlist.v

│ │ │ │ └── system_bram_rd_0_0_sim_netlist.vhdl

│ │ │ ├── system_data_processing_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_data_processing_0_0.v

│ │ │ │ ├── system_data_processing_0_0_sim_netlist.v

│ │ │ │ └── system_data_processing_0_0_sim_netlist.vhdl

│ │ │ ├── system_gen_nums_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_gen_nums_0_0.v

│ │ │ │ ├── system_gen_nums_0_0_sim_netlist.v

│ │ │ │ └── system_gen_nums_0_0_sim_netlist.vhdl

│ │ │ ├── system_processing_system7_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_processing_system7_0_0.v

│ │ │ │ ├── system_processing_system7_0_0_sim_netlist.v

│ │ │ │ └── system_processing_system7_0_0_sim_netlist.vhdl

│ │ │ ├── system_rst_ps7_0_100M_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_rst_ps7_0_100M_0.vhd

│ │ │ │ ├── system_rst_ps7_0_100M_0_sim_netlist.v

│ │ │ │ └── system_rst_ps7_0_100M_0_sim_netlist.vhdl

│ │ │ ├── system_system_ila_0_0

│ │ │ │ ├── bd_0

│ │ │ │ │ ├── bd_d5b8.bd

│ │ │ │ │ ├── ip

│ │ │ │ │ │ ├── ip_0

│ │ │ │ │ │ │ └── sim

│ │ │ │ │ │ │ └── bd_d5b8_ila_lib_0.v

│ │ │ │ │ │ └── ip_1

│ │ │ │ │ │ ├── bd_d5b8_g_inst_0_gigantic_mux.v

│ │ │ │ │ │ └── sim

│ │ │ │ │ │ └── bd_d5b8_g_inst_0.v

│ │ │ │ │ └── sim

│ │ │ │ │ ├── bd_d5b8.protoinst

│ │ │ │ │ └── bd_d5b8.v

│ │ │ │ ├── sim

│ │ │ │ │ └── system_system_ila_0_0.v

│ │ │ │ ├── system_system_ila_0_0_sim_netlist.v

│ │ │ │ └── system_system_ila_0_0_sim_netlist.vhdl

│ │ │ ├── system_xbar_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_xbar_0.v

│ │ │ │ ├── system_xbar_0_sim_netlist.v

│ │ │ │ └── system_xbar_0_sim_netlist.vhdl

│ │ │ └── system_xlconcat_0_0

│ │ │ └── sim

│ │ │ └── system_xlconcat_0_0.v

│ │ ├── ipshared

│ │ │ └── 565b

│ │ │ ├── hdl

│ │ │ │ ├── bram_rd_v1_0.v

│ │ │ │ └── bram_rd_v1_0_S00_AXI.v

│ │ │ └── src

│ │ │ └── bram_rd.v

│ │ ├── sim

│ │ │ ├── system.protoinst

│ │ │ └── system.v

│ │ └── system.bmm

│ ├── mem_init_files

│ │ ├── bd_44e3_one_0.h

│ │ ├── libps7.dll

│ │ ├── libps7.so

│ │ ├── libremoteport.dll

│ │ ├── libremoteport.so

│ │ ├── mux_core.txt

│ │ ├── ps7_init.h

│ │ ├── ps7_init.html

│ │ ├── ps7_init.tcl

│ │ ├── ps7_init_gpl.h

│ │ ├── sc_post_elab.rld

│ │ ├── system_xlconstant_0_0.h

│ │ └── xlconstant_v1_1_5.h

│ └── sim_scripts

│ └── system

│ ├── README.txt

│ ├── activehdl

│ │ ├── README.txt

│ │ ├── bd_44e3_one_0.h

│ │ ├── compile.do

│ │ ├── file_info.txt

│ │ ├── glbl.v

│ │ ├── libps7.dll

│ │ ├── libps7.so

│ │ ├── libremoteport.dll

│ │ ├── libremoteport.so

│ │ ├── mux_core.txt

│ │ ├── ps7_init.html

│ │ ├── ps7_init.tcl

│ │ ├── sc_post_elab.rld

│ │ ├── simulate.do

│ │ ├── system.sh

│ │ ├── system.udo

│ │ ├── wave.do

│ │ └── xlconstant_v1_1_5.h

│ ├── ies

│ │ ├── README.txt

│ │ ├── bd_44e3_one_0.h

│ │ ├── file_info.txt

│ │ ├── glbl.v

│ │ ├── libps7.dll

│ │ ├── libps7.so

│ │ ├── libremoteport.dll

│ │ ├── libremoteport.so

│ │ ├── mux_core.txt

│ │ ├── ps7_init.html

│ │ ├── ps7_init.tcl

│ │ ├── run.f

│ │ ├── sc_post_elab.rld

│ │ ├── system.sh

│ │ └── xlconstant_v1_1_5.h

│ ├── modelsim

│ │ ├── README.txt

│ │ ├── bd_44e3_one_0.h

│ │ ├── compile.do

│ │ ├── file_info.txt

│ │ ├── glbl.v

│ │ ├── libps7.dll

│ │ ├── libps7.so

│ │ ├── libremoteport.dll

│ │ ├── libremoteport.so

│ │ ├── mux_core.txt

│ │ ├── ps7_init.html

│ │ ├── ps7_init.tcl

│ │ ├── sc_post_elab.rld

│ │ ├── simulate.do

│ │ ├── system.sh

│ │ ├── system.udo

│ │ ├── wave.do

│ │ └── xlconstant_v1_1_5.h

│ ├── questa

│ │ ├── README.txt

│ │ ├── bd_44e3_one_0.h

│ │ ├── compile.do

│ │ ├── elaborate.do

│ │ ├── file_info.txt

│ │ ├── glbl.v

│ │ ├── libps7.dll

│ │ ├── libps7.so

│ │ ├── libremoteport.dll

│ │ ├── libremoteport.so

│ │ ├── mux_core.txt

│ │ ├── ps7_init.html

│ │ ├── ps7_init.tcl

│ │ ├── sc_post_elab.rld

│ │ ├── simulate.do

│ │ ├── system.sh

│ │ ├── system.udo

│ │ ├── wave.do

│ │ └── xlconstant_v1_1_5.h

│ ├── riviera

│ │ ├── README.txt

│ │ ├── bd_44e3_one_0.h

│ │ ├── compile.do

│ │ ├── file_info.txt

│ │ ├── glbl.v

│ │ ├── libps7.dll

│ │ ├── libps7.so

│ │ ├── libremoteport.dll

│ │ ├── libremoteport.so

│ │ ├── mux_core.txt

│ │ ├── ps7_init.html

│ │ ├── ps7_init.tcl

│ │ ├── sc_post_elab.rld

│ │ ├── simulate.do

│ │ ├── system.sh

│ │ ├── system.udo

│ │ ├── wave.do

│ │ └── xlconstant_v1_1_5.h

│ ├── vcs

│ │ ├── README.txt

│ │ ├── bd_44e3_one_0.h

│ │ ├── file_info.txt

│ │ ├── glbl.v

│ │ ├── libps7.dll

│ │ ├── libps7.so

│ │ ├── libremoteport.dll

│ │ ├── libremoteport.so

│ │ ├── mux_core.txt

│ │ ├── ps7_init.html

│ │ ├── ps7_init.tcl

│ │ ├── sc_post_elab.rld

│ │ ├── simulate.do

│ │ ├── system.sh

│ │ └── xlconstant_v1_1_5.h

│ ├── xcelium

│ │ ├── README.txt

│ │ ├── bd_44e3_one_0.h

│ │ ├── file_info.txt

│ │ ├── glbl.v

│ │ ├── libps7.dll

│ │ ├── libps7.so

│ │ ├── libremoteport.dll

│ │ ├── libremoteport.so

│ │ ├── mux_core.txt

│ │ ├── ps7_init.html

│ │ ├── ps7_init.tcl

│ │ ├── run.f

│ │ ├── sc_post_elab.rld

│ │ ├── system.sh

│ │ └── xlconstant_v1_1_5.h

│ └── xsim

│ ├── README.txt

│ ├── bd_44e3_one_0.h

│ ├── cmd.tcl

│ ├── elab.opt

│ ├── example_bram_dma.smi

│ ├── file_info.txt

│ ├── glbl.v

│ ├── libps7.dll

│ ├── libps7.so

│ ├── libremoteport.dll

│ ├── libremoteport.so

│ ├── mux_core.txt

│ ├── protoinst_files

│ │ ├── bd_44e3.protoinst

│ │ ├── bd_d5b8.protoinst

│ │ └── system.protoinst

│ ├── ps7_init.html

│ ├── ps7_init.tcl

│ ├── sc_post_elab.rld

│ ├── system.sh

│ ├── vhdl.prj

│ ├── vlog.prj

│ ├── xlconstant_v1_1_5.h

│ └── xsim.ini

├── example_bram_dma.runs

│ ├── impl_1

│ │ ├── ISEWrap.js

│ │ ├── ISEWrap.sh

│ │ ├── debug_nets.ltx

│ │ ├── exception.log

│ │ ├── gen_run.xml

│ │ ├── htr.txt

│ │ ├── init_design.pb

│ │ ├── opt_design.pb

│ │ ├── place_design.pb

│ │ ├── project.wdf

│ │ ├── route_design.pb

│ │ ├── rundef.js

│ │ ├── runme.bat

│ │ ├── runme.log

│ │ ├── runme.sh

│ │ ├── system_wrapper.bit

│ │ ├── system_wrapper.hwdef

│ │ ├── system_wrapper.ltx

│ │ ├── system_wrapper.mmi

│ │ ├── system_wrapper.sysdef

│ │ ├── system_wrapper.tcl

│ │ ├── system_wrapper.vdi

│ │ ├── system_wrapper_bd.bmm

│ │ ├── system_wrapper_bus_skew_routed.pb

│ │ ├── system_wrapper_bus_skew_routed.rpt

│ │ ├── system_wrapper_bus_skew_routed.rpx

│ │ ├── system_wrapper_clock_utilization_routed.rpt

│ │ ├── system_wrapper_control_sets_placed.rpt

│ │ ├── system_wrapper_drc_opted.pb

│ │ ├── system_wrapper_drc_opted.rpt

│ │ ├── system_wrapper_drc_opted.rpx

│ │ ├── system_wrapper_drc_routed.pb

│ │ ├── system_wrapper_drc_routed.rpt

│ │ ├── system_wrapper_drc_routed.rpx

│ │ ├── system_wrapper_io_placed.rpt

│ │ ├── system_wrapper_methodology_drc_routed.pb

│ │ ├── system_wrapper_methodology_drc_routed.rpt

│ │ ├── system_wrapper_methodology_drc_routed.rpx

│ │ ├── system_wrapper_opt.dcp

│ │ ├── system_wrapper_placed.dcp

│ │ ├── system_wrapper_power_routed.rpt

│ │ ├── system_wrapper_power_routed.rpx

│ │ ├── system_wrapper_power_summary_routed.pb

│ │ ├── system_wrapper_route_status.pb

│ │ ├── system_wrapper_route_status.rpt

│ │ ├── system_wrapper_routed.dcp

│ │ ├── system_wrapper_timing_summary_routed.pb

│ │ ├── system_wrapper_timing_summary_routed.rpt

│ │ ├── system_wrapper_timing_summary_routed.rpx

│ │ ├── system_wrapper_utilization_placed.pb

│ │ ├── system_wrapper_utilization_placed.rpt

│ │ ├── usage_statistics_webtalk.html

│ │ ├── usage_statistics_webtalk.xml

│ │ ├── vivado.jou

│ │ ├── vivado.pb

│ │ └── write_bitstream.pb

│ ├── synth_1

│ │ ├── ISEWrap.js

│ │ ├── ISEWrap.sh

│ │ ├── __synthesis_is_complete__

│ │ ├── dont_touch.xdc

│ │ ├── gen_run.xml

│ │ ├── htr.txt

│ │ ├── project.wdf

│ │ ├── rundef.js

│ │ ├── runme.bat

│ │ ├── runme.log

│ │ ├── runme.sh

│ │ ├── system_wrapper.dcp

│ │ ├── system_wrapper.tcl

│ │ ├── system_wrapper.vds

│ │ ├── system_wrapper_utilization_synth.pb

│ │ ├── system_wrapper_utilization_synth.rpt

│ │ ├── vivado.jou

│ │ └── vivado.pb

│ ├── system_axi_dma_0_0_synth_1

│ │ ├── ISEWrap.js

│ │ ├── ISEWrap.sh

│ │ ├── __synthesis_is_complete__

│ │ ├── dont_touch.xdc

│ │ ├── gen_run.xml

│ │ ├── htr.txt

│ │ ├── rundef.js

│ │ ├── runme.bat

│ │ ├── runme.log

│ │ ├── runme.sh

│ │ ├── system_axi_dma_0_0.dcp

│ │ ├── system_axi_dma_0_0.tcl

│ │ ├── system_axi_dma_0_0.vds

│ │ ├── system_axi_dma_0_0_utilization_synth.pb

│ │ ├── system_axi_dma_0_0_utilization_synth.rpt

│ │ ├── vivado.jou

│ │ └── vivado.pb

│ ├── system_axi_smc_0_synth_1

│ │ ├── ISEWrap.js

│ │ ├── ISEWrap.sh

│ │ ├── __synthesis_is_complete__

│ │ ├── dont_touch.xdc

│ │ ├── gen_run.xml

│ │ ├── htr.txt

│ │ ├── rundef.js

│ │ ├── runme.bat

│ │ ├── runme.log

│ │ ├── runme.sh

│ │ ├── system_axi_smc_0.dcp

│ │ ├── system_axi_smc_0.tcl

│ │ ├── system_axi_smc_0.vds

│ │ ├── system_axi_smc_0_utilization_synth.pb

│ │ ├── system_axi_smc_0_utilization_synth.rpt

│ │ ├── vivado.jou

│ │ └── vivado.pb

│ ├── system_data_processing_0_0_synth_1

│ │ ├── ISEWrap.js

│ │ ├── ISEWrap.sh

│ │ ├── __synthesis_is_complete__

│ │ ├── gen_run.xml

│ │ ├── htr.txt

│ │ ├── project.wdf

│ │ ├── rundef.js

│ │ ├── runme.bat

│ │ ├── runme.log

│ │ ├── runme.sh

│ │ ├── system_data_processing_0_0.dcp

│ │ ├── system_data_processing_0_0.tcl

│ │ ├── system_data_processing_0_0.vds

│ │ ├── system_data_processing_0_0_sim_netlist.v

│ │ ├── system_data_processing_0_0_sim_netlist.vhdl

│ │ ├── system_data_processing_0_0_stub.v

│ │ ├── system_data_processing_0_0_stub.vhdl

│ │ ├── system_data_processing_0_0_utilization_synth.pb

│ │ ├── system_data_processing_0_0_utilization_synth.rpt

│ │ ├── vivado.jou

│ │ └── vivado.pb

│ ├── system_gen_nums_0_0_synth_1

│ │ ├── ISEWrap.js

│ │ ├── ISEWrap.sh

│ │ ├── __synthesis_is_complete__

│ │ ├── gen_run.xml

│ │ ├── htr.txt

│ │ ├── project.wdf

│ │ ├── rundef.js

│ │ ├── runme.bat

│ │ ├── runme.log

│ │ ├── runme.sh

│ │ ├── system_gen_nums_0_0.dcp

│ │ ├── system_gen_nums_0_0.tcl

│ │ ├── system_gen_nums_0_0.vds

│ │ ├── system_gen_nums_0_0_sim_netlist.v

│ │ ├── system_gen_nums_0_0_sim_netlist.vhdl

│ │ ├── system_gen_nums_0_0_stub.v

│ │ ├── system_gen_nums_0_0_stub.vhdl

│ │ ├── system_gen_nums_0_0_utilization_synth.pb

│ │ ├── system_gen_nums_0_0_utilization_synth.rpt

│ │ ├── vivado.jou

│ │ └── vivado.pb

│ └── system_system_ila_0_0_synth_1

│ ├── ISEWrap.js

│ ├── ISEWrap.sh

│ ├── __synthesis_is_complete__

│ ├── dont_touch.xdc

│ ├── gen_run.xml

│ ├── htr.txt

│ ├── rundef.js

│ ├── runme.bat

│ ├── runme.log

│ ├── runme.sh

│ ├── system_system_ila_0_0.dcp

│ ├── system_system_ila_0_0.tcl

│ ├── system_system_ila_0_0.vds

│ ├── system_system_ila_0_0_utilization_synth.pb

│ ├── system_system_ila_0_0_utilization_synth.rpt

│ ├── vivado.jou

│ └── vivado.pb

├── example_bram_dma.sdk

│ ├── RemoteSystemsTempFiles

│ ├── SDK.log

│ ├── dma_bram

│ │ ├── Debug

│ │ │ ├── Xilinx.spec

│ │ │ ├── dma_bram.elf

│ │ │ ├── dma_bram.elf.size

│ │ │ ├── makefile

│ │ │ ├── objects.mk

│ │ │ ├── sources.mk

│ │ │ └── src

│ │ │ ├── main.d

│ │ │ ├── main.o

│ │ │ ├── subdir.mk

│ │ │ └── utils

│ │ │ ├── common_util

│ │ │ │ └── subdir.mk

│ │ │ ├── dma

│ │ │ │ └── subdir.mk

│ │ │ ├── gpio

│ │ │ │ └── subdir.mk

│ │ │ └── intr

│ │ │ └── subdir.mk

│ │ └── src

│ │ ├── README.txt

│ │ ├── Xilinx.spec

│ │ ├── bk

│ │ ├── lscript.ld

│ │ └── main.cc

│ ├── dma_bram_bsp

│ │ ├── Makefile

│ │ ├── ps7_cortexa9_0

│ │ │ ├── code

│ │ │ ├── include

│ │ │ │ ├── _profile_timer_hw.h

│ │ │ │ ├── bram_rd.h

│ │ │ │ ├── bspconfig.h

│ │ │ │ ├── mblaze_nt_types.h

│ │ │ │ ├── profile.h

│ │ │ │ ├── sleep.h

│ │ │ │ ├── smc.h

│ │ │ │ ├── vectors.h

│ │ │ │ ├── xadcps.h

│ │ │ │ ├── xadcps_hw.h

│ │ │ │ ├── xaxidma.h

│ │ │ │ ├── xaxidma_bd.h

│ │ │ │ ├── xaxidma_bdring.h

│ │ │ │ ├── xaxidma_hw.h

│ │ │ │ ├── xaxidma_porting_guide.h

│ │ │ │ ├── xbasic_types.h

│ │ │ │ ├── xbram.h

│ │ │ │ ├── xbram_hw.h

│ │ │ │ ├── xcoresightpsdcc.h

│ │ │ │ ├── xcpu_cortexa9.h

│ │ │ │ ├── xddrps.h

│ │ │ │ ├── xdebug.h

│ │ │ │ ├── xdevcfg.h

│ │ │ │ ├── xdevcfg_hw.h

│ │ │ │ ├── xdmaps.h

│ │ │ │ ├── xdmaps_hw.h

│ │ │ │ ├── xenv.h

│ │ │ │ ├── xenv_standalone.h

│ │ │ │ ├── xil_assert.h

│ │ │ │ ├── xil_cache.h

│ │ │ │ ├── xil_cache_l.h

│ │ │ │ ├── xil_cache_vxworks.h

│ │ │ │ ├── xil_errata.h

│ │ │ │ ├── xil_exception.h

│ │ │ │ ├── xil_hal.h

│ │ │ │ ├── xil_io.h

│ │ │ │ ├── xil_macroback.h

│ │ │ │ ├── xil_mem.h

│ │ │ │ ├── xil_misc_psreset_api.h

│ │ │ │ ├── xil_mmu.h

│ │ │ │ ├── xil_printf.h

│ │ │ │ ├── xil_sleeptimer.h

│ │ │ │ ├── xil_testcache.h

│ │ │ │ ├── xil_testio.h

│ │ │ │ ├── xil_testmem.h

│ │ │ │ ├── xil_types.h

│ │ │ │ ├── xl2cc.h

│ │ │ │ ├── xl2cc_counter.h

│ │ │ │ ├── xparameters.h

│ │ │ │ ├── xparameters_ps.h

│ │ │ │ ├── xplatform_info.h

│ │ │ │ ├── xpm_counter.h

│ │ │ │ ├── xpseudo_asm.h

│ │ │ │ ├── xpseudo_asm_gcc.h

│ │ │ │ ├── xreg_cortexa9.h

│ │ │ │ ├── xscugic.h

│ │ │ │ ├── xscugic_hw.h

│ │ │ │ ├── xscutimer.h

│ │ │ │ ├── xscutimer_hw.h

│ │ │ │ ├── xscuwdt.h

│ │ │ │ ├── xscuwdt_hw.h

│ │ │ │ ├── xstatus.h

│ │ │ │ ├── xtime_l.h

│ │ │ │ ├── xuartps.h

│ │ │ │ └── xuartps_hw.h

│ │ │ ├── lib

│ │ │ │ └── libxil.a

│ │ │ └── libsrc

│ │ │ ├── axidma_v9_8

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── xaxidma.c

│ │ │ │ ├── xaxidma.h

│ │ │ │ ├── xaxidma_bd.c

│ │ │ │ ├── xaxidma_bd.h

│ │ │ │ ├── xaxidma_bdring.c

│ │ │ │ ├── xaxidma_bdring.h

│ │ │ │ ├── xaxidma_g.c

│ │ │ │ ├── xaxidma_hw.h

│ │ │ │ ├── xaxidma_porting_guide.h

│ │ │ │ ├── xaxidma_selftest.c

│ │ │ │ ├── xaxidma_sinit.c

│ │ │ │ └── xdebug.h

│ │ │ ├── bram_rd_v1_0

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── bram_rd.c

│ │ │ │ ├── bram_rd.h

│ │ │ │ └── bram_rd_selftest.c

│ │ │ ├── bram_v4_2

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── xbram.c

│ │ │ │ ├── xbram.h

│ │ │ │ ├── xbram_g.c

│ │ │ │ ├── xbram_hw.h

│ │ │ │ ├── xbram_intr.c

│ │ │ │ ├── xbram_selftest.c

│ │ │ │ └── xbram_sinit.c

│ │ │ ├── coresightps_dcc_v1_4

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── xcoresightpsdcc.c

│ │ │ │ └── xcoresightpsdcc.h

│ │ │ ├── cpu_cortexa9_v2_7

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ └── xcpu_cortexa9.h

│ │ │ ├── ddrps_v1_0

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ └── xddrps.h

│ │ │ ├── devcfg_v3_5

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── xdevcfg.c

│ │ │ │ ├── xdevcfg.h

│ │ │ │ ├── xdevcfg_g.c

│ │ │ │ ├── xdevcfg_hw.c

│ │ │ │ ├── xdevcfg_hw.h

│ │ │ │ ├── xdevcfg_intr.c

│ │ │ │ ├── xdevcfg_selftest.c

│ │ │ │ └── xdevcfg_sinit.c

│ │ │ ├── dmaps_v2_4

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── xdmaps.c

│ │ │ │ ├── xdmaps.h

│ │ │ │ ├── xdmaps_g.c

│ │ │ │ ├── xdmaps_hw.c

│ │ │ │ ├── xdmaps_hw.h

│ │ │ │ ├── xdmaps_selftest.c

│ │ │ │ └── xdmaps_sinit.c

│ │ │ ├── generic_v2_0

│ │ │ │ └── src

│ │ │ ├── scugic_v3_10

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── xscugic.c

│ │ │ │ ├── xscugic.h

│ │ │ │ ├── xscugic_g.c

│ │ │ │ ├── xscugic_hw.c

│ │ │ │ ├── xscugic_hw.h

│ │ │ │ ├── xscugic_intr.c

│ │ │ │ ├── xscugic_selftest.c

│ │ │ │ └── xscugic_sinit.c

│ │ │ ├── scutimer_v2_1

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── xscutimer.c

│ │ │ │ ├── xscutimer.h

│ │ │ │ ├── xscutimer_g.c

│ │ │ │ ├── xscutimer_hw.h

│ │ │ │ ├── xscutimer_selftest.c

│ │ │ │ └── xscutimer_sinit.c

│ │ │ ├── scuwdt_v2_1

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── xscuwdt.c

│ │ │ │ ├── xscuwdt.h

│ │ │ │ ├── xscuwdt_g.c

│ │ │ │ ├── xscuwdt_hw.h

│ │ │ │ ├── xscuwdt_selftest.c

│ │ │ │ └── xscuwdt_sinit.c

│ │ │ ├── standalone_v6_8

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── _exit.c

│ │ │ │ ├── _exit.o

│ │ │ │ ├── _open.c

│ │ │ │ ├── _open.o

│ │ │ │ ├── _sbrk.c

│ │ │ │ ├── _sbrk.o

│ │ │ │ ├── abort.c

│ │ │ │ ├── abort.o

│ │ │ │ ├── asm_vectors.S

│ │ │ │ ├── asm_vectors.o

│ │ │ │ ├── boot.S

│ │ │ │ ├── boot.o

│ │ │ │ ├── bspconfig.h

│ │ │ │ ├── changelog.txt

│ │ │ │ ├── close.c

│ │ │ │ ├── close.o

│ │ │ │ ├── config.make

│ │ │ │ ├── cpu_init.S

│ │ │ │ ├── cpu_init.o

│ │ │ │ ├── errno.c

│ │ │ │ ├── errno.o

│ │ │ │ ├── fcntl.c

│ │ │ │ ├── fcntl.o

│ │ │ │ ├── fstat.c

│ │ │ │ ├── fstat.o

│ │ │ │ ├── getpid.c

│ │ │ │ ├── getpid.o

│ │ │ │ ├── inbyte.c

│ │ │ │ ├── inbyte.o

│ │ │ │ ├── isatty.c

│ │ │ │ ├── isatty.o

│ │ │ │ ├── kill.c

│ │ │ │ ├── kill.o

│ │ │ │ ├── lseek.c

│ │ │ │ ├── lseek.o

│ │ │ │ ├── open.c

│ │ │ │ ├── open.o

│ │ │ │ ├── outbyte.c

│ │ │ │ ├── outbyte.o

│ │ │ │ ├── print.c

│ │ │ │ ├── print.o

│ │ │ │ ├── profile

│ │ │ │ │ ├── Makefile

│ │ │ │ │ ├── _profile_clean.c

│ │ │ │ │ ├── _profile_init.c

│ │ │ │ │ ├── _profile_timer_hw.c

│ │ │ │ │ ├── _profile_timer_hw.h

│ │ │ │ │ ├── dummy.S

│ │ │ │ │ ├── mblaze_nt_types.h

│ │ │ │ │ ├── profile.h

│ │ │ │ │ ├── profile_cg.c

│ │ │ │ │ ├── profile_config.h

│ │ │ │ │ ├── profile_hist.c

│ │ │ │ │ ├── profile_mcount_arm.S

│ │ │ │ │ ├── profile_mcount_mb.S

│ │ │ │ │ └── profile_mcount_ppc.S

│ │ │ │ ├── putnum.c

│ │ │ │ ├── putnum.o

│ │ │ │ ├── read.c

│ │ │ │ ├── read.o

│ │ │ │ ├── sbrk.c

│ │ │ │ ├── sbrk.o

│ │ │ │ ├── sleep.c

│ │ │ │ ├── sleep.h

│ │ │ │ ├── sleep.o

│ │ │ │ ├── smc.h

│ │ │ │ ├── translation_table.S

│ │ │ │ ├── translation_table.o

│ │ │ │ ├── unlink.c

│ │ │ │ ├── unlink.o

│ │ │ │ ├── usleep.c

│ │ │ │ ├── usleep.o

│ │ │ │ ├── vectors.c

│ │ │ │ ├── vectors.h

│ │ │ │ ├── vectors.o

│ │ │ │ ├── write.c

│ │ │ │ ├── write.o

│ │ │ │ ├── xbasic_types.h

│ │ │ │ ├── xdebug.h

│ │ │ │ ├── xenv.h

│ │ │ │ ├── xenv_standalone.h

│ │ │ │ ├── xil-crt0.S

│ │ │ │ ├── xil-crt0.o

│ │ │ │ ├── xil_assert.c

│ │ │ │ ├── xil_assert.h

│ │ │ │ ├── xil_assert.o

│ │ │ │ ├── xil_cache.c

│ │ │ │ ├── xil_cache.h

│ │ │ │ ├── xil_cache.o

│ │ │ │ ├── xil_cache_l.h

│ │ │ │ ├── xil_cache_vxworks.h

│ │ │ │ ├── xil_errata.h

│ │ │ │ ├── xil_exception.c

│ │ │ │ ├── xil_exception.h

│ │ │ │ ├── xil_exception.o

│ │ │ │ ├── xil_hal.h

│ │ │ │ ├── xil_io.c

│ │ │ │ ├── xil_io.h

│ │ │ │ ├── xil_io.o

│ │ │ │ ├── xil_macroback.h

│ │ │ │ ├── xil_mem.c

│ │ │ │ ├── xil_mem.h

│ │ │ │ ├── xil_mem.o

│ │ │ │ ├── xil_misc_psreset_api.c

│ │ │ │ ├── xil_misc_psreset_api.h

│ │ │ │ ├── xil_misc_psreset_api.o

│ │ │ │ ├── xil_mmu.c

│ │ │ │ ├── xil_mmu.h

│ │ │ │ ├── xil_mmu.o

│ │ │ │ ├── xil_printf.c

│ │ │ │ ├── xil_printf.h

│ │ │ │ ├── xil_printf.o

│ │ │ │ ├── xil_sleepcommon.c

│ │ │ │ ├── xil_sleepcommon.o

│ │ │ │ ├── xil_sleeptimer.c

│ │ │ │ ├── xil_sleeptimer.h

│ │ │ │ ├── xil_sleeptimer.o

│ │ │ │ ├── xil_testcache.c

│ │ │ │ ├── xil_testcache.h

│ │ │ │ ├── xil_testcache.o

│ │ │ │ ├── xil_testio.c

│ │ │ │ ├── xil_testio.h

│ │ │ │ ├── xil_testio.o

│ │ │ │ ├── xil_testmem.c

│ │ │ │ ├── xil_testmem.h

│ │ │ │ ├── xil_testmem.o

│ │ │ │ ├── xil_types.h

│ │ │ │ ├── xl2cc.h

│ │ │ │ ├── xl2cc_counter.c

│ │ │ │ ├── xl2cc_counter.h

│ │ │ │ ├── xl2cc_counter.o

│ │ │ │ ├── xparameters_ps.h

│ │ │ │ ├── xplatform_info.c

│ │ │ │ ├── xplatform_info.h

│ │ │ │ ├── xplatform_info.o

│ │ │ │ ├── xpm_counter.c

│ │ │ │ ├── xpm_counter.h

│ │ │ │ ├── xpm_counter.o

│ │ │ │ ├── xpseudo_asm.h

│ │ │ │ ├── xpseudo_asm_gcc.h

│ │ │ │ ├── xreg_cortexa9.h

│ │ │ │ ├── xstatus.h

│ │ │ │ ├── xtime_l.c

│ │ │ │ ├── xtime_l.h

│ │ │ │ └── xtime_l.o

│ │ │ ├── uartps_v3_7

│ │ │ │ └── src

│ │ │ │ ├── Makefile

│ │ │ │ ├── xuartps.c

│ │ │ │ ├── xuartps.h

│ │ │ │ ├── xuartps_g.c

│ │ │ │ ├── xuartps_hw.c

│ │ │ │ ├── xuartps_hw.h

│ │ │ │ ├── xuartps_intr.c

│ │ │ │ ├── xuartps_options.c

│ │ │ │ ├── xuartps_selftest.c

│ │ │ │ └── xuartps_sinit.c

│ │ │ └── xadcps_v2_3

│ │ │ └── src

│ │ │ ├── Makefile

│ │ │ ├── xadcps.c

│ │ │ ├── xadcps.h

│ │ │ ├── xadcps_g.c

│ │ │ ├── xadcps_hw.h

│ │ │ ├── xadcps_intr.c

│ │ │ ├── xadcps_selftest.c

│ │ │ └── xadcps_sinit.c

│ │ └── system.mss

│ ├── system_wrapper.hdf

│ ├── system_wrapper_hw_platform_0

│ │ ├── drivers

│ │ │ └── bram_rd_v1_0

│ │ │ ├── data

│ │ │ │ ├── bram_rd.mdd

│ │ │ │ └── bram_rd.tcl

│ │ │ └── src

│ │ │ ├── Makefile

│ │ │ ├── bram_rd.c

│ │ │ ├── bram_rd.h

│ │ │ └── bram_rd_selftest.c

│ │ ├── ps7_init.c

│ │ ├── ps7_init.h

│ │ ├── ps7_init.html

│ │ ├── ps7_init.tcl

│ │ ├── ps7_init_gpl.c

│ │ ├── ps7_init_gpl.h

│ │ ├── system.hdf

│ │ ├── system_wrapper.bit

│ │ └── system_wrapper.mmi

│ └── webtalk

│ ├── sdk_webtalk.tcl

│ ├── sdk_webtalk.wdm

│ ├── usage_statistics_ext_sdk.html

│ ├── usage_statistics_ext_sdk.xml

│ ├── webtalk.jou

│ ├── webtalk.log

│ ├── webtalk_12580.backup.jou

│ ├── webtalk_12580.backup.log

│ ├── webtalk_19948.backup.jou

│ ├── webtalk_19948.backup.log

│ ├── webtalk_376.backup.jou

│ └── webtalk_376.backup.log

├── example_bram_dma.sim

├── example_bram_dma.srcs

│ └── sources_1

│ ├── bd

│ │ ├── mref

│ │ │ ├── data_processing

│ │ │ │ ├── component.xml

│ │ │ │ └── xgui

│ │ │ │ └── data_processing_v1_0.tcl

│ │ │ └── gen_nums

│ │ │ ├── component.xml

│ │ │ └── xgui

│ │ │ └── gen_nums_v1_0.tcl

│ │ └── system

│ │ ├── hdl

│ │ │ └── system_wrapper.v

│ │ ├── hw_handoff

│ │ │ ├── system.hwh

│ │ │ └── system_bd.tcl

│ │ ├── ip

│ │ │ ├── system_auto_pc_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_auto_pc_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_auto_pc_0.v

│ │ │ │ ├── system_auto_pc_0.dcp

│ │ │ │ ├── system_auto_pc_0.xci

│ │ │ │ ├── system_auto_pc_0.xml

│ │ │ │ ├── system_auto_pc_0_ooc.xdc

│ │ │ │ ├── system_auto_pc_0_sim_netlist.v

│ │ │ │ ├── system_auto_pc_0_sim_netlist.vhdl

│ │ │ │ ├── system_auto_pc_0_stub.v

│ │ │ │ └── system_auto_pc_0_stub.vhdl

│ │ │ ├── system_auto_pc_1

│ │ │ │ ├── sim

│ │ │ │ │ └── system_auto_pc_1.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_auto_pc_1.v

│ │ │ │ ├── system_auto_pc_1.dcp

│ │ │ │ ├── system_auto_pc_1.xci

│ │ │ │ ├── system_auto_pc_1.xml

│ │ │ │ ├── system_auto_pc_1_ooc.xdc

│ │ │ │ ├── system_auto_pc_1_sim_netlist.v

│ │ │ │ ├── system_auto_pc_1_sim_netlist.vhdl

│ │ │ │ ├── system_auto_pc_1_stub.v

│ │ │ │ └── system_auto_pc_1_stub.vhdl

│ │ │ ├── system_auto_pc_2

│ │ │ │ ├── sim

│ │ │ │ │ └── system_auto_pc_2.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_auto_pc_2.v

│ │ │ │ ├── system_auto_pc_2.dcp

│ │ │ │ ├── system_auto_pc_2.xci

│ │ │ │ ├── system_auto_pc_2.xml

│ │ │ │ ├── system_auto_pc_2_ooc.xdc

│ │ │ │ ├── system_auto_pc_2_sim_netlist.v

│ │ │ │ ├── system_auto_pc_2_sim_netlist.vhdl

│ │ │ │ ├── system_auto_pc_2_stub.v

│ │ │ │ └── system_auto_pc_2_stub.vhdl

│ │ │ ├── system_axi_bram_ctrl_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_axi_bram_ctrl_0_0.vhd

│ │ │ │ ├── synth

│ │ │ │ │ └── system_axi_bram_ctrl_0_0.vhd

│ │ │ │ ├── system_axi_bram_ctrl_0_0.dcp

│ │ │ │ ├── system_axi_bram_ctrl_0_0.xci

│ │ │ │ ├── system_axi_bram_ctrl_0_0.xml

│ │ │ │ ├── system_axi_bram_ctrl_0_0_sim_netlist.v

│ │ │ │ ├── system_axi_bram_ctrl_0_0_sim_netlist.vhdl

│ │ │ │ ├── system_axi_bram_ctrl_0_0_stub.v

│ │ │ │ └── system_axi_bram_ctrl_0_0_stub.vhdl

│ │ │ ├── system_axi_dma_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_axi_dma_0_0.vhd

│ │ │ │ ├── synth

│ │ │ │ │ └── system_axi_dma_0_0.vhd

│ │ │ │ ├── system_axi_dma_0_0.dcp

│ │ │ │ ├── system_axi_dma_0_0.xci

│ │ │ │ ├── system_axi_dma_0_0.xdc

│ │ │ │ ├── system_axi_dma_0_0.xml

│ │ │ │ ├── system_axi_dma_0_0_clocks.xdc

│ │ │ │ ├── system_axi_dma_0_0_ooc.xdc

│ │ │ │ ├── system_axi_dma_0_0_sim_netlist.v

│ │ │ │ ├── system_axi_dma_0_0_sim_netlist.vhdl

│ │ │ │ ├── system_axi_dma_0_0_stub.v

│ │ │ │ └── system_axi_dma_0_0_stub.vhdl

│ │ │ ├── system_axi_smc_0

│ │ │ │ ├── bd_0

│ │ │ │ │ ├── bd_44e3.bd

│ │ │ │ │ ├── bd_44e3.bxml

│ │ │ │ │ ├── hdl

│ │ │ │ │ │ └── bd_44e3_wrapper.v

│ │ │ │ │ ├── hw_handoff

│ │ │ │ │ │ ├── system_axi_smc_0.hwh

│ │ │ │ │ │ └── system_axi_smc_0_bd.tcl

│ │ │ │ │ ├── ip

│ │ │ │ │ │ ├── ip_0

│ │ │ │ │ │ │ ├── bd_44e3_one_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_one_0.xml

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ ├── bd_44e3_one_0.h

│ │ │ │ │ │ │ │ ├── bd_44e3_one_0.v

│ │ │ │ │ │ │ │ └── xlconstant_v1_1_5.h

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_one_0.v

│ │ │ │ │ │ ├── ip_1

│ │ │ │ │ │ │ ├── bd_44e3_psr_aclk_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_psr_aclk_0.xdc

│ │ │ │ │ │ │ ├── bd_44e3_psr_aclk_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_psr_aclk_0_board.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_psr_aclk_0.vhd

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_psr_aclk_0.vhd

│ │ │ │ │ │ ├── ip_10

│ │ │ │ │ │ │ ├── bd_44e3_s00a2s_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_s00a2s_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_s00a2s_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_s00a2s_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_s00a2s_0.sv

│ │ │ │ │ │ ├── ip_11

│ │ │ │ │ │ │ ├── bd_44e3_sarn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_sarn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_sarn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_sarn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_sarn_0.sv

│ │ │ │ │ │ ├── ip_12

│ │ │ │ │ │ │ ├── bd_44e3_srn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_srn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_srn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_srn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_srn_0.sv

│ │ │ │ │ │ ├── ip_13

│ │ │ │ │ │ │ ├── bd_44e3_s01mmu_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_s01mmu_0.xml

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_s01mmu_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_s01mmu_0.sv

│ │ │ │ │ │ ├── ip_14

│ │ │ │ │ │ │ ├── bd_44e3_s01tr_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_s01tr_0.xml

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_s01tr_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_s01tr_0.sv

│ │ │ │ │ │ ├── ip_15

│ │ │ │ │ │ │ ├── bd_44e3_s01sic_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_s01sic_0.xml

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_s01sic_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_s01sic_0.sv

│ │ │ │ │ │ ├── ip_16

│ │ │ │ │ │ │ ├── bd_44e3_s01a2s_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_s01a2s_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_s01a2s_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_s01a2s_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_s01a2s_0.sv

│ │ │ │ │ │ ├── ip_17

│ │ │ │ │ │ │ ├── bd_44e3_sawn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_sawn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_sawn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_sawn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_sawn_0.sv

│ │ │ │ │ │ ├── ip_18

│ │ │ │ │ │ │ ├── bd_44e3_swn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_swn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_swn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_swn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_swn_0.sv

│ │ │ │ │ │ ├── ip_19

│ │ │ │ │ │ │ ├── bd_44e3_sbn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_sbn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_sbn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_sbn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_sbn_0.sv

│ │ │ │ │ │ ├── ip_2

│ │ │ │ │ │ │ ├── bd_44e3_arsw_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_arsw_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_arsw_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_arsw_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_arsw_0.sv

│ │ │ │ │ │ ├── ip_20

│ │ │ │ │ │ │ ├── bd_44e3_m00s2a_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_m00s2a_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_m00s2a_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_m00s2a_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_m00s2a_0.sv

│ │ │ │ │ │ ├── ip_21

│ │ │ │ │ │ │ ├── bd_44e3_m00arn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_m00arn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_m00arn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_m00arn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_m00arn_0.sv

│ │ │ │ │ │ ├── ip_22

│ │ │ │ │ │ │ ├── bd_44e3_m00rn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_m00rn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_m00rn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_m00rn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_m00rn_0.sv

│ │ │ │ │ │ ├── ip_23

│ │ │ │ │ │ │ ├── bd_44e3_m00awn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_m00awn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_m00awn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_m00awn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_m00awn_0.sv

│ │ │ │ │ │ ├── ip_24

│ │ │ │ │ │ │ ├── bd_44e3_m00wn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_m00wn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_m00wn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_m00wn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_m00wn_0.sv

│ │ │ │ │ │ ├── ip_25

│ │ │ │ │ │ │ ├── bd_44e3_m00bn_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_m00bn_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_m00bn_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_m00bn_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_m00bn_0.sv

│ │ │ │ │ │ ├── ip_26

│ │ │ │ │ │ │ ├── bd_44e3_m00e_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_m00e_0.xml

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_m00e_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_m00e_0.sv

│ │ │ │ │ │ ├── ip_3

│ │ │ │ │ │ │ ├── bd_44e3_rsw_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_rsw_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_rsw_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_rsw_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_rsw_0.sv

│ │ │ │ │ │ ├── ip_4

│ │ │ │ │ │ │ ├── bd_44e3_awsw_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_awsw_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_awsw_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_awsw_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_awsw_0.sv

│ │ │ │ │ │ ├── ip_5

│ │ │ │ │ │ │ ├── bd_44e3_wsw_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_wsw_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_wsw_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_wsw_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_wsw_0.sv

│ │ │ │ │ │ ├── ip_6

│ │ │ │ │ │ │ ├── bd_44e3_bsw_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_bsw_0.xml

│ │ │ │ │ │ │ ├── bd_44e3_bsw_0_ooc.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_bsw_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_bsw_0.sv

│ │ │ │ │ │ ├── ip_7

│ │ │ │ │ │ │ ├── bd_44e3_s00mmu_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_s00mmu_0.xml

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_s00mmu_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_s00mmu_0.sv

│ │ │ │ │ │ ├── ip_8

│ │ │ │ │ │ │ ├── bd_44e3_s00tr_0.xci

│ │ │ │ │ │ │ ├── bd_44e3_s00tr_0.xml

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_44e3_s00tr_0.sv

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_44e3_s00tr_0.sv

│ │ │ │ │ │ └── ip_9

│ │ │ │ │ │ ├── bd_44e3_s00sic_0.xci

│ │ │ │ │ │ ├── bd_44e3_s00sic_0.xml

│ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ └── bd_44e3_s00sic_0.sv

│ │ │ │ │ │ └── synth

│ │ │ │ │ │ └── bd_44e3_s00sic_0.sv

│ │ │ │ │ ├── sim

│ │ │ │ │ │ ├── bd_44e3.protoinst

│ │ │ │ │ │ └── bd_44e3.v

│ │ │ │ │ └── synth

│ │ │ │ │ ├── bd_44e3.v

│ │ │ │ │ └── system_axi_smc_0.hwdef

│ │ │ │ ├── ooc.xdc

│ │ │ │ ├── sc_post_elab.rld

│ │ │ │ ├── sim

│ │ │ │ │ └── system_axi_smc_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_axi_smc_0.v

│ │ │ │ ├── system_axi_smc_0.dcp

│ │ │ │ ├── system_axi_smc_0.xci

│ │ │ │ ├── system_axi_smc_0.xml

│ │ │ │ ├── system_axi_smc_0_sim_netlist.v

│ │ │ │ ├── system_axi_smc_0_sim_netlist.vhdl

│ │ │ │ ├── system_axi_smc_0_stub.v

│ │ │ │ └── system_axi_smc_0_stub.vhdl

│ │ │ ├── system_axis_data_fifo_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_axis_data_fifo_0_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_axis_data_fifo_0_0.v

│ │ │ │ ├── system_axis_data_fifo_0_0.dcp

│ │ │ │ ├── system_axis_data_fifo_0_0.xci

│ │ │ │ ├── system_axis_data_fifo_0_0.xml

│ │ │ │ ├── system_axis_data_fifo_0_0_sim_netlist.v

│ │ │ │ ├── system_axis_data_fifo_0_0_sim_netlist.vhdl

│ │ │ │ ├── system_axis_data_fifo_0_0_stub.v

│ │ │ │ └── system_axis_data_fifo_0_0_stub.vhdl

│ │ │ ├── system_blk_mem_gen_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_blk_mem_gen_0_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_blk_mem_gen_0_0.vhd

│ │ │ │ ├── system_blk_mem_gen_0_0.dcp

│ │ │ │ ├── system_blk_mem_gen_0_0.xci

│ │ │ │ ├── system_blk_mem_gen_0_0.xml

│ │ │ │ ├── system_blk_mem_gen_0_0_ooc.xdc

│ │ │ │ ├── system_blk_mem_gen_0_0_sim_netlist.v

│ │ │ │ ├── system_blk_mem_gen_0_0_sim_netlist.vhdl

│ │ │ │ ├── system_blk_mem_gen_0_0_stub.v

│ │ │ │ └── system_blk_mem_gen_0_0_stub.vhdl

│ │ │ ├── system_bram_rd_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_bram_rd_0_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_bram_rd_0_0.v

│ │ │ │ ├── system_bram_rd_0_0.dcp

│ │ │ │ ├── system_bram_rd_0_0.xci

│ │ │ │ ├── system_bram_rd_0_0.xml

│ │ │ │ ├── system_bram_rd_0_0_sim_netlist.v

│ │ │ │ ├── system_bram_rd_0_0_sim_netlist.vhdl

│ │ │ │ ├── system_bram_rd_0_0_stub.v

│ │ │ │ └── system_bram_rd_0_0_stub.vhdl

│ │ │ ├── system_data_processing_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_data_processing_0_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_data_processing_0_0.v

│ │ │ │ ├── system_data_processing_0_0.dcp

│ │ │ │ ├── system_data_processing_0_0.xci

│ │ │ │ ├── system_data_processing_0_0.xml

│ │ │ │ ├── system_data_processing_0_0_sim_netlist.v

│ │ │ │ ├── system_data_processing_0_0_sim_netlist.vhdl

│ │ │ │ ├── system_data_processing_0_0_stub.v

│ │ │ │ └── system_data_processing_0_0_stub.vhdl

│ │ │ ├── system_gen_nums_0_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_gen_nums_0_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_gen_nums_0_0.v

│ │ │ │ ├── system_gen_nums_0_0.dcp

│ │ │ │ ├── system_gen_nums_0_0.xci

│ │ │ │ ├── system_gen_nums_0_0.xml

│ │ │ │ ├── system_gen_nums_0_0_sim_netlist.v

│ │ │ │ ├── system_gen_nums_0_0_sim_netlist.vhdl

│ │ │ │ ├── system_gen_nums_0_0_stub.v

│ │ │ │ └── system_gen_nums_0_0_stub.vhdl

│ │ │ ├── system_processing_system7_0_0

│ │ │ │ ├── hdl

│ │ │ │ │ └── verilog

│ │ │ │ │ ├── processing_system7_v5_5_processing_system7.v

│ │ │ │ │ └── system_processing_system7_0_0.hwdef

│ │ │ │ ├── ps7_init.c

│ │ │ │ ├── ps7_init.h

│ │ │ │ ├── ps7_init.html

│ │ │ │ ├── ps7_init.tcl

│ │ │ │ ├── ps7_init_gpl.c

│ │ │ │ ├── ps7_init_gpl.h

│ │ │ │ ├── ps7_parameters.xml

│ │ │ │ ├── sim

│ │ │ │ │ ├── libps7.dll

│ │ │ │ │ ├── libps7.so

│ │ │ │ │ ├── libremoteport.dll

│ │ │ │ │ ├── libremoteport.so

│ │ │ │ │ ├── system_processing_system7_0_0.sv

│ │ │ │ │ └── system_processing_system7_0_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_processing_system7_0_0.v

│ │ │ │ ├── system_processing_system7_0_0.dcp

│ │ │ │ ├── system_processing_system7_0_0.xci

│ │ │ │ ├── system_processing_system7_0_0.xdc

│ │ │ │ ├── system_processing_system7_0_0.xml

│ │ │ │ ├── system_processing_system7_0_0_sim_netlist.v

│ │ │ │ ├── system_processing_system7_0_0_sim_netlist.vhdl

│ │ │ │ ├── system_processing_system7_0_0_stub.v

│ │ │ │ └── system_processing_system7_0_0_stub.vhdl

│ │ │ ├── system_ps7_0_axi_periph_0

│ │ │ │ ├── system_ps7_0_axi_periph_0.xci

│ │ │ │ └── system_ps7_0_axi_periph_0.xml

│ │ │ ├── system_rst_ps7_0_100M_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_rst_ps7_0_100M_0.vhd

│ │ │ │ ├── synth

│ │ │ │ │ └── system_rst_ps7_0_100M_0.vhd

│ │ │ │ ├── system_rst_ps7_0_100M_0.dcp

│ │ │ │ ├── system_rst_ps7_0_100M_0.xci

│ │ │ │ ├── system_rst_ps7_0_100M_0.xdc

│ │ │ │ ├── system_rst_ps7_0_100M_0.xml

│ │ │ │ ├── system_rst_ps7_0_100M_0_board.xdc

│ │ │ │ ├── system_rst_ps7_0_100M_0_sim_netlist.v

│ │ │ │ ├── system_rst_ps7_0_100M_0_sim_netlist.vhdl

│ │ │ │ ├── system_rst_ps7_0_100M_0_stub.v

│ │ │ │ └── system_rst_ps7_0_100M_0_stub.vhdl

│ │ │ ├── system_system_ila_0_0

│ │ │ │ ├── bd_0

│ │ │ │ │ ├── bd_d5b8.bd

│ │ │ │ │ ├── bd_d5b8_ooc.xdc

│ │ │ │ │ ├── hdl

│ │ │ │ │ │ └── bd_d5b8_wrapper.v

│ │ │ │ │ ├── hw_handoff

│ │ │ │ │ │ ├── system_system_ila_0_0.hwh

│ │ │ │ │ │ └── system_system_ila_0_0_bd.tcl

│ │ │ │ │ ├── ip

│ │ │ │ │ │ ├── ip_0

│ │ │ │ │ │ │ ├── bd_d5b8_ila_lib_0.xci

│ │ │ │ │ │ │ ├── bd_d5b8_ila_lib_0.xml

│ │ │ │ │ │ │ ├── bd_d5b8_ila_lib_0_ooc.xdc

│ │ │ │ │ │ │ ├── ila_v6_2

│ │ │ │ │ │ │ │ └── constraints

│ │ │ │ │ │ │ │ ├── ila.xdc

│ │ │ │ │ │ │ │ └── ila_impl.xdc

│ │ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ │ └── bd_d5b8_ila_lib_0.v

│ │ │ │ │ │ │ └── synth

│ │ │ │ │ │ │ └── bd_d5b8_ila_lib_0.v

│ │ │ │ │ │ └── ip_1

│ │ │ │ │ │ ├── bd_d5b8_g_inst_0.xci

│ │ │ │ │ │ ├── bd_d5b8_g_inst_0.xml

│ │ │ │ │ │ ├── bd_d5b8_g_inst_0_gigantic_mux.v

│ │ │ │ │ │ ├── mux_core.txt

│ │ │ │ │ │ ├── sim

│ │ │ │ │ │ │ └── bd_d5b8_g_inst_0.v

│ │ │ │ │ │ └── synth

│ │ │ │ │ │ └── bd_d5b8_g_inst_0.v

│ │ │ │ │ ├── sim

│ │ │ │ │ │ ├── bd_d5b8.protoinst

│ │ │ │ │ │ └── bd_d5b8.v

│ │ │ │ │ └── synth

│ │ │ │ │ ├── bd_d5b8.v

│ │ │ │ │ └── system_system_ila_0_0.hwdef

│ │ │ │ ├── sim

│ │ │ │ │ └── system_system_ila_0_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_system_ila_0_0.v

│ │ │ │ ├── system_system_ila_0_0.dcp

│ │ │ │ ├── system_system_ila_0_0.xci

│ │ │ │ ├── system_system_ila_0_0.xml

│ │ │ │ ├── system_system_ila_0_0_sim_netlist.v

│ │ │ │ ├── system_system_ila_0_0_sim_netlist.vhdl

│ │ │ │ ├── system_system_ila_0_0_stub.v

│ │ │ │ └── system_system_ila_0_0_stub.vhdl

│ │ │ ├── system_xbar_0

│ │ │ │ ├── sim

│ │ │ │ │ └── system_xbar_0.v

│ │ │ │ ├── synth

│ │ │ │ │ └── system_xbar_0.v

│ │ │ │ ├── system_xbar_0.dcp

│ │ │ │ ├── system_xbar_0.xci

│ │ │ │ ├── system_xbar_0.xml

│ │ │ │ ├── system_xbar_0_sim_netlist.v

│ │ │ │ ├── system_xbar_0_sim_netlist.vhdl

│ │ │ │ ├── system_xbar_0_stub.v

│ │ │ │ └── system_xbar_0_stub.vhdl

│ │ │ └── system_xlconcat_0_0

│ │ │ ├── sim

│ │ │ │ └── system_xlconcat_0_0.v

│ │ │ ├── synth

│ │ │ │ └── system_xlconcat_0_0.v

│ │ │ ├── system_xlconcat_0_0.xci

│ │ │ └── system_xlconcat_0_0.xml

│ │ ├── ipshared

│ │ │ ├── 0513

│ │ │ │ └── hdl

│ │ │ │ └── lib_pkg_v1_0_rfs.vhd

│ │ │ ├── 09b0

│ │ │ │ └── hdl

│ │ │ │ └── axi_dma_v7_1_vh_rfs.vhd

│ │ │ ├── 122e

│ │ │ │ └── hdl

│ │ │ │ ├── verilog

│ │ │ │ │ ├── xsdbs_v1_0_2_i2x.vh

│ │ │ │ │ └── xsdbs_v1_0_2_in.vh

│ │ │ │ └── xsdbs_v1_0_vl_rfs.v

│ │ │ ├── 1b7e

│ │ │ │ └── hdl

│ │ │ │ ├── ltlib_v1_0_vl_rfs.v

│ │ │ │ └── verilog

│ │ │ │ ├── ltlib_v1_0_0_lib_fn.vh

│ │ │ │ └── ltlib_v1_0_0_ver.vh

│ │ │ ├── 2751

│ │ │ │ ├── hdl

│ │ │ │ │ └── blk_mem_gen_v8_3_vhsyn_rfs.vhd

│ │ │ │ └── simulation

│ │ │ │ └── blk_mem_gen_v8_3.v

│ │ │ ├── 27fe

│ │ │ │ └── hdl

│ │ │ │ └── axi_bram_ctrl_v4_1_rfs.vhd

│ │ │ ├── 2f66

│ │ │ │ └── hdl

│ │ │ │ └── xlconcat_v2_1_vl_rfs.v

│ │ │ ├── 37c2

│ │ │ │ ├── hdl

│ │ │ │ │ └── blk_mem_gen_v8_4_vhsyn_rfs.vhd

│ │ │ │ └── simulation

│ │ │ │ └── blk_mem_gen_v8_4.v

│ │ │ ├── 4649

│ │ │ │ └── hdl

│ │ │ │ └── xlconstant_v1_1_vl_rfs.v

│ │ │ ├── 4efd

│ │ │ │ └── hdl

│ │ │ │ └── axis_data_fifo_v2_0_vl_rfs.v

│ │ │ ├── 51ce

│ │ │ │ └── hdl

│ │ │ │ └── lib_srl_fifo_v1_0_rfs.vhd

│ │ │ ├── 544a

│ │ │ │ └── hdl

│ │ │ │ └── lib_fifo_v1_0_rfs.vhd

│ │ │ ├── 565b

│ │ │ │ ├── hdl

│ │ │ │ │ ├── bram_rd_v1_0.v

│ │ │ │ │ └── bram_rd_v1_0_S00_AXI.v

│ │ │ │ └── src

│ │ │ │ └── bram_rd.v

│ │ │ ├── 64f4

│ │ │ │ ├── hdl

│ │ │ │ │ ├── fifo_generator_v13_2_rfs.v

│ │ │ │ │ ├── fifo_generator_v13_2_rfs.vhd

│ │ │ │ │ └── fifo_generator_v13_2_vhsyn_rfs.vhd

│ │ │ │ └── simulation

│ │ │ │ └── fifo_generator_vlog_beh.v

│ │ │ ├── 6c9d

│ │ │ │ └── hdl

│ │ │ │ └── axi_crossbar_v2_1_vl_rfs.v

│ │ │ ├── 7005

│ │ │ │ └── hdl

│ │ │ │ └── sc_sc2axi_v1_0_vl_rfs.sv

│ │ │ ├── 70cf

│ │ │ │ └── hdl

│ │ │ │ ├── processing_system7_vip_v1_0_6_apis.v

│ │ │ │ ├── processing_system7_vip_v1_0_6_axi_acp.v

│ │ │ │ ├── processing_system7_vip_v1_0_6_axi_gp.v

│ │ │ │ ├── processing_system7_vip_v1_0_6_axi_hp.v

│ │ │ │ ├── processing_system7_vip_v1_0_6_local_params.v

│ │ │ │ ├── processing_system7_vip_v1_0_6_reg_init.v

│ │ │ │ ├── processing_system7_vip_v1_0_6_reg_params.v

│ │ │ │ ├── processing_system7_vip_v1_0_6_unused_ports.v

│ │ │ │ └── processing_system7_vip_v1_0_vl_rfs.sv

│ │ │ ├── 7a04

│ │ │ │ └── hdl

│ │ │ │ └── axi_protocol_converter_v2_1_vl_rfs.v

│ │ │ ├── 7d3c

│ │ │ │ └── hdl

│ │ │ │ ├── verilog

│ │ │ │ │ ├── xsdbm_v3_0_0_bs.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_bs_core.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_bs_core_ext.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_bs_core_vec.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_bs_ext.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_bs_ports.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_bs_vec.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_bsid_ports.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_bsid_vec_ports.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_i2x.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_icn.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_id_map.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_id_vec_map.vh

│ │ │ │ │ ├── xsdbm_v3_0_0_in.vh

│ │ │ │ │ └── xsdbm_v3_0_0_sl_prt_map.vh

│ │ │ │ └── xsdbm_v3_0_vl_rfs.v

│ │ │ ├── 8713

│ │ │ │ └── hdl

│ │ │ │ ├── axis_infrastructure_v1_1_0.vh

│ │ │ │ └── axis_infrastructure_v1_1_vl_rfs.v

│ │ │ ├── 8842

│ │ │ │ └── hdl

│ │ │ │ └── proc_sys_reset_v5_0_vh_rfs.vhd

│ │ │ ├── 8fd3

│ │ │ │ └── hdl

│ │ │ │ └── verilog

│ │ │ │ ├── processing_system7_v5_5_atc.v

│ │ │ │ ├── processing_system7_v5_5_aw_atc.v

│ │ │ │ ├── processing_system7_v5_5_b_atc.v

│ │ │ │ ├── processing_system7_v5_5_trace_buffer.v

│ │ │ │ └── processing_system7_v5_5_w_atc.v

│ │ │ ├── 979d

│ │ │ │ └── hdl

│ │ │ │ ├── sc_util_v1_0_vl_rfs.sv

│ │ │ │ └── verilog

│ │ │ │ ├── sc_util_v1_0_4_constants.vh

│ │ │ │ └── sc_util_v1_0_4_structs.svh

│ │ │ ├── 98af

│ │ │ │ └── hdl

│ │ │ │ └── axi_vip_v1_1_vl_rfs.sv

│ │ │ ├── 9ade

│ │ │ │ └── hdl

│ │ │ │ └── sc_si_converter_v1_0_vl_rfs.sv

│ │ │ ├── b2d0

│ │ │ │ └── hdl

│ │ │ │ ├── sc_node_v1_0_vl_rfs.sv

│ │ │ │ └── verilog

│ │ │ │ └── sc_node_v1_0_10_t_reqsend.svh

│ │ │ ├── b387

│ │ │ │ └── hdl

│ │ │ │ └── sc_exit_v1_0_vl_rfs.sv

│ │ │ ├── b752

│ │ │ │ └── hdl

│ │ │ │ └── generic_baseblocks_v2_1_vl_rfs.v

│ │ │ ├── b89e

│ │ │ │ └── hdl

│ │ │ │ └── sc_axi2sc_v1_0_vl_rfs.sv

│ │ │ ├── c012

│ │ │ │ └── hdl

│ │ │ │ └── sc_switchboard_v1_0_vl_rfs.sv

│ │ │ ├── c45e

│ │ │ │ └── hdl

│ │ │ │ ├── ila_v6_2_syn_rfs.v

│ │ │ │ └── verilog

│ │ │ │ ├── ila_v6_2_8_ila_in.vh

│ │ │ │ ├── ila_v6_2_8_ila_lib_fn.vh

│ │ │ │ ├── ila_v6_2_8_ila_lparam.vh

│ │ │ │ ├── ila_v6_2_8_ila_param.vh

│ │ │ │ └── ila_v6_2_8_ila_ver.vh

│ │ │ ├── c4fd

│ │ │ │ └── hdl

│ │ │ │ └── axi_data_fifo_v2_1_vl_rfs.v

│ │ │ ├── ca72

│ │ │ │ └── hdl

│ │ │ │ └── sc_transaction_regulator_v1_0_vl_rfs.sv

│ │ │ ├── cc23

│ │ │ │ └── hdl

│ │ │ │ └── axi_register_slice_v2_1_vl_rfs.v

│ │ │ ├── d322

│ │ │ │ └── hdl

│ │ │ │ └── gigantic_mux_v1_0_cntr.v

│ │ │ ├── dfb3

│ │ │ │ └── hdl

│ │ │ │ └── axi_datamover_v5_1_vh_rfs.vhd

│ │ │ ├── e6d5

│ │ │ │ └── hdl

│ │ │ │ └── fifo_generator_v13_1_vhsyn_rfs.vhd

│ │ │ ├── ec67

│ │ │ │ └── hdl

│ │ │ │ ├── axi_infrastructure_v1_1_0.vh

│ │ │ │ └── axi_infrastructure_v1_1_vl_rfs.v

│ │ │ ├── ef1e

│ │ │ │ └── hdl

│ │ │ │ └── lib_cdc_v1_0_rfs.vhd

│ │ │ ├── efa7

│ │ │ │ └── hdl

│ │ │ │ └── axi_sg_v4_1_rfs.vhd

│ │ │ └── f85e

│ │ │ └── hdl

│ │ │ └── sc_mmu_v1_0_vl_rfs.sv

│ │ ├── sim

│ │ │ ├── system.protoinst

│ │ │ └── system.v

│ │ ├── synth

│ │ │ ├── system.hwdef

│ │ │ └── system.v

│ │ ├── system.bd

│ │ ├── system.bmm

│ │ ├── system.bxml

│ │ ├── system_ooc.xdc

│ │ └── ui

│ │ └── bd_c954508f.ui

│ └── new

│ ├── data_processing.v

│ └── gen_nums.v

├── example_bram_dma.xpr

├── ip_repo

│ └── bram_rd_1.0

│ ├── bd

│ │ └── bd.tcl

│ ├── component.xml

│ ├── drivers

│ │ └── bram_rd_v1_0

│ │ ├── data

│ │ │ ├── bram_rd.mdd

│ │ │ └── bram_rd.tcl

│ │ └── src

│ │ ├── Makefile

│ │ ├── bram_rd.c

│ │ ├── bram_rd.h

│ │ └── bram_rd_selftest.c

│ ├── example_designs

│ │ ├── bfm_design

│ │ │ ├── bram_rd_v1_0_tb.sv

│ │ │ └── design.tcl

│ │ └── debug_hw_design

│ │ ├── bram_rd_v1_0_hw_test.tcl

│ │ └── design.tcl

│ ├── hdl

│ │ ├── bram_rd.v

│ │ ├── bram_rd_v1_0.v

│ │ └── bram_rd_v1_0_S00_AXI.v

│ ├── src

│ │ └── bram_rd.v

│ └── xgui

│ └── bram_rd_v1_0.tcl

├── vivado.jou

└── vivado.log

490 directories, 1335 files

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论