实例介绍

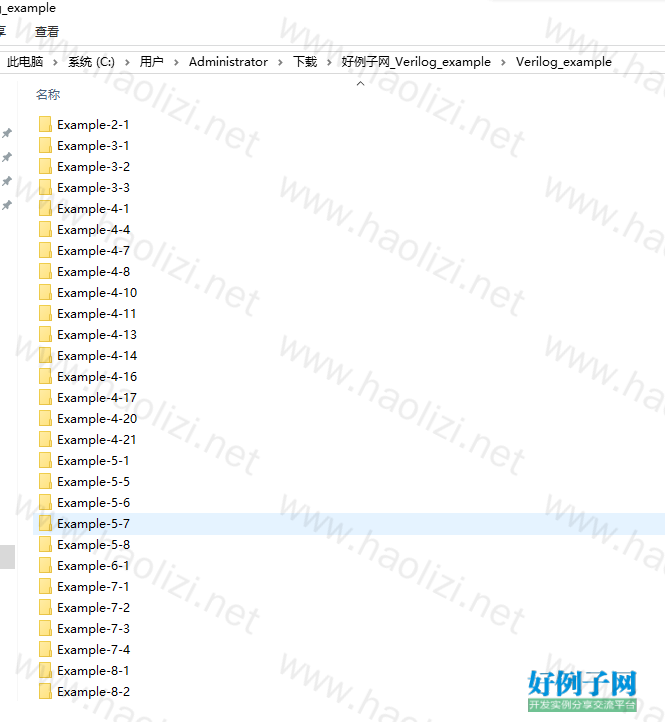

【实例截图】

【核心代码】

│ book_doem.v

│

├─Example-2-1

│ HelloVlog.v

│

├─Example-3-1

│ FullAdd.v

│ transcript

│

├─Example-3-2

│ FullAdd.v

│

├─Example-3-3

│ CRC10.v

│

├─Example-4-1

│ │ cnt.prd

│ │ cnt.prj

│ │ 示例说明.doc

│ │

│ ├─rev_1

│ │ │ cnt1.edf

│ │ │ cnt1.fse

│ │ │ cnt1.srm

│ │ │ cnt1.srr

│ │ │ cnt1.srs

│ │ │ cnt1.tlg

│ │ │ cnt2.edf

│ │ │ cnt2.fse

│ │ │ cnt2.srm

│ │ │ cnt2.srr

│ │ │ cnt2.srs

│ │ │ cnt2.tlg

│ │ │ cnt3.edf

│ │ │ cnt3.fse

│ │ │ cnt3.srm

│ │ │ cnt3.srr

│ │ │ cnt3.srs

│ │ │ cnt3.tlg

│ │ │

│ │ ├─par_1

│ │ └─syntmp

│ │ cnt1.plg

│ │ cnt2.msg

│ │ cnt2.plg

│ │ cnt3.msg

│ │ cnt3.plg

│ │

│ └─source

│ cnt1.v

│ cnt2.v

│ cnt3.v

│ syntmp.msg

│

├─Example-4-10

│ │ 示例说明.doc

│ │

│ ├─bibus

│ │ │ bibus.prd

│ │ │ bibus.prj

│ │ │ bibus.v

│ │ │ decode.v

│ │ │ syntmp.msg

│ │ │

│ │ └─rev_1

│ │ │ bibus.fse

│ │ │ bibus.srd

│ │ │ bibus.srm

│ │ │ bibus.srr

│ │ │ bibus.srs

│ │ │ bibus.sxr

│ │ │ bibus.tcl

│ │ │ bibus.tlg

│ │ │ bibus.vqm

│ │ │ bibus.xrf

│ │ │ bibus_cons.tcl

│ │ │ bibus_rm.tcl

│ │ │ rpt_bibus.areasrr

│ │ │ rpt_bibus_areasrr.htm

│ │ │

│ │ ├─syntmp

│ │ │ bibus.msg

│ │ │ bibus.plg

│ │ │ bibus_cons_ui.tcl

│ │ │

│ │ └─verif

│ │ bibus.vif

│ │

│ ├─complex_bibus

│ │ │ complex_bibus.prd

│ │ │ complex_bibus.prj

│ │ │ complex_bibus.v

│ │ │ complex_bibus2.v

│ │ │ counter.v

│ │ │ decode.v

│ │ │ syntmp.msg

│ │ │

│ │ └─rev_1

│ │ │ AutoConstraint_complex_bibus.sdc

│ │ │ complex_bibus.fse

│ │ │ complex_bibus.srd

│ │ │ complex_bibus.srm

│ │ │ complex_bibus.srr

│ │ │ complex_bibus.srs

│ │ │ complex_bibus.sxr

│ │ │ complex_bibus.tcl

│ │ │ complex_bibus.tlg

│ │ │ complex_bibus.vqm

│ │ │ complex_bibus.xrf

│ │ │ complex_bibus2.fse

│ │ │ complex_bibus2.srd

│ │ │ complex_bibus2.srm

│ │ │ complex_bibus2.srr

│ │ │ complex_bibus2.srs

│ │ │ complex_bibus2.sxr

│ │ │ complex_bibus2.tcl

│ │ │ complex_bibus2.tlg

│ │ │ complex_bibus2.vqm

│ │ │ complex_bibus2.xrf

│ │ │ complex_bibus2_cons.tcl

│ │ │ complex_bibus2_rm.tcl

│ │ │ complex_bibus_cons.tcl

│ │ │ complex_bibus_rm.tcl

│ │ │ decode.srr

│ │ │ rpt_complex_bibus.areasrr

│ │ │ rpt_complex_bibus_areasrr.htm

│ │ │

│ │ ├─par_1

│ │ ├─syntmp

│ │ │ complex_bibus.msg

│ │ │ complex_bibus.plg

│ │ │ complex_bibus2.plg

│ │ │ complex_bibus2_cons_ui.tcl

│ │ │ complex_bibus_cons_ui.tcl

│ │ │

│ │ └─verif

│ │ complex_bibus.vif

│ │ complex_bibus2.vif

│ │

│ └─source

│ bibus.v

│ complex_bibus.v

│ complex_bibus2.v

│ counter.v

│ decode.v

│

├─Example-4-11

│ │ mux.prd

│ │ mux.prj

│ │ mux.v

│ │ mux2.v

│ │ syntmp.msg

│ │ 示例说明.doc

│ │

│ ├─rev_1

│ │ │ AutoConstraint_mux.sdc

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │ mux.edf

│ │ │ mux.edn

│ │ │ mux.fse

│ │ │ mux.ncf

│ │ │ mux.prf

│ │ │ mux.srd

│ │ │ mux.srm

│ │ │ mux.srr

│ │ │ mux.srs

│ │ │ mux.sxr

│ │ │ mux.tcl

│ │ │ mux.tlg

│ │ │ mux.vqm

│ │ │ mux.xrf

│ │ │ mux2.edf

│ │ │ mux2.fse

│ │ │ mux2.ncf

│ │ │ mux2.srd

│ │ │ mux2.srm

│ │ │ mux2.srr

│ │ │ mux2.srs

│ │ │ mux2.tlg

│ │ │ mux_cons.tcl

│ │ │ mux_rm.tcl

│ │ │ rpt_mux.areasrr

│ │ │ rpt_mux_areasrr.htm

│ │ │

│ │ ├─syntmp

│ │ │ mux.plg

│ │ │ mux2.msg

│ │ │ mux2.plg

│ │ │ mux_cons_ui.tcl

│ │ │

│ │ └─verif

│ │ mux.vif

│ │ mux2.vif

│ │

│ └─source

│ mux.v

│ mux2.v

│

├─Example-4-13

│ │ 示例说明.doc

│ │

│ ├─ram_basic

│ │ │ ram_basic.prd

│ │ │ ram_basic.prj

│ │ │ ram_basic.v

│ │ │

│ │ └─rev_2

│ │ │ .recordref

│ │ │ AutoConstraint_ram_basic.sdc

│ │ │ ram_basic.edf

│ │ │ ram_basic.fse

│ │ │ ram_basic.ncf

│ │ │ ram_basic.srd

│ │ │ ram_basic.srm

│ │ │ ram_basic.srr

│ │ │ ram_basic.srs

│ │ │ ram_basic.tlg

│ │ │ rpt_ram_basic.areasrr

│ │ │ rpt_ram_basic_areasrr.htm

│ │ │ traplog.tlg

│ │ │

│ │ ├─par_1

│ │ ├─syntmp

│ │ │ ram_basic.msg

│ │ │ ram_basic.plg

│ │ │

│ │ └─verif

│ │ ram_basic.vif

│ │

│ ├─sim

│ │ │ ram_basic.cr.mti

│ │ │ ram_basic.mpf

│ │ │ ram_basic.v

│ │ │ ram_basic_tb.v

│ │ │ transcript

│ │ │ vsim.wlf

│ │ │ wave.do

│ │ │

│ │ └─work

│ │ │ _info

│ │ │

│ │ ├─ram_basic

│ │ │ verilog.asm

│ │ │ _primary.dat

│ │ │ _primary.vhd

│ │ │

│ │ └─ram_basic_tb

│ │ verilog.asm

│ │ _primary.dat

│ │ _primary.vhd

│ │

│ └─source

│ ram_basic.v

│

├─Example-4-14

│ │ 示例说明.doc

│ │

│ ├─clk_3div

│ │ │ clk_3div.v

│ │ │ clk_3div_tb.v

│ │ │

│ │ ├─sim

│ │ │ │ clk_div3.cr.mti

│ │ │ │ clk_div3.mpf

│ │ │ │ vsim.wlf

│ │ │ │ wave.do

│ │ │ │

│ │ │ └─work

│ │ │ │ _info

│ │ │ │

│ │ │ ├─clk_3div

│ │ │ │ verilog.asm

│ │ │ │ _primary.dat

│ │ │ │ _primary.vhd

│ │ │ │

│ │ │ └─clk_3div_tb

│ │ │ verilog.asm

│ │ │ _primary.dat

│ │ │ _primary.vhd

│ │ │

│ │ └─synthesis

│ │ │ clk_div3.prd

│ │ │ clk_div3.prj

│ │ │

│ │ └─rev_1

│ │ │ clk_3div.edf

│ │ │ clk_3div.fse

│ │ │ clk_3div.srm

│ │ │ clk_3div.srr

│ │ │ clk_3div.srs

│ │ │ clk_3div.tlg

│ │ │

│ │ └─syntmp

│ │ clk_3div.msg

│ │ clk_3div.plg

│ │

│ ├─clk_div_phase

│ │ │ clk_div_phase.prd

│ │ │ clk_div_phase.prj

│ │ │ clk_div_phase.v

│ │ │ clk_div_phase_tb.v

│ │ │

│ │ ├─rev_1

│ │ │ │ AutoConstraint_clk_div_phase.sdc

│ │ │ │ clk_div_phase.edf

│ │ │ │ clk_div_phase.fse

│ │ │ │ clk_div_phase.ncf

│ │ │ │ clk_div_phase.srd

│ │ │ │ clk_div_phase.srm

│ │ │ │ clk_div_phase.srr

│ │ │ │ clk_div_phase.srs

│ │ │ │ clk_div_phase.tlg

│ │ │ │ rpt_clk_div_phase.areasrr

│ │ │ │ rpt_clk_div_phase_areasrr.htm

│ │ │ │

│ │ │ ├─par_1

│ │ │ ├─syntmp

│ │ │ │ clk_div_phase.msg

│ │ │ │ clk_div_phase.plg

│ │ │ │

│ │ │ └─verif

│ │ │ clk_div_phase.vif

│ │ │

│ │ └─sim

│ │ │ clk_div.cr.mti

│ │ │ clk_div.mpf

│ │ │ transcript

│ │ │ vsim.wlf

│ │ │ wave.do

│ │ │

│ │ └─work

│ │ │ _info

│ │ │

│ │ ├─clk_div_phase

│ │ │ verilog.asm

│ │ │ _primary.dat

│ │ │ _primary.vhd

│ │ │

│ │ └─clk_div_phase_tb

│ │ verilog.asm

│ │ _primary.dat

│ │ _primary.vhd

│ │

│ └─source

├─Example-4-16

│ │ srl2pal.prd

│ │ srl2pal.prj

│ │ srl2pal.v

│ │ 示例说明.doc

│ │

│ ├─rev_1

│ │ │ AutoConstraint_srl2pal.sdc

│ │ │ rpt_srl2pal.areasrr

│ │ │ rpt_srl2pal_areasrr.htm

│ │ │ srl2pal.edf

│ │ │ srl2pal.fse

│ │ │ srl2pal.ncf

│ │ │ srl2pal.srd

│ │ │ srl2pal.srm

│ │ │ srl2pal.srr

│ │ │ srl2pal.srs

│ │ │ srl2pal.tlg

│ │ │

│ │ ├─par_1

│ │ ├─syntmp

│ │ │ srl2pal.msg

│ │ │ srl2pal.plg

│ │ │

│ │ └─verif

│ │ srl2pal.vif

│ │

│ └─source

│ srl2pal.v

│

├─Example-4-17

│ │ 示例说明.doc

│ │

│ ├─asyn_rst

│ │ │ asyn_rst.prd

│ │ │ asyn_rst.prj

│ │ │ asyn_rst.v

│ │ │

│ │ └─rev_1

│ │ │ asyn_rst.edn

│ │ │ asyn_rst.fse

│ │ │ asyn_rst.prf

│ │ │ asyn_rst.srm

│ │ │ asyn_rst.srr

│ │ │ asyn_rst.srs

│ │ │ asyn_rst.tlg

│ │ │ AutoConstraint_asyn_rst.sdc

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │

│ │ └─syntmp

│ │ asyn_rst.msg

│ │ asyn_rst.plg

│ │

│ ├─asyn_rst_syn_release

│ │ asyn_rst_syn_release.v

│ │ asyn_rst_syn_release.v.txt

│ │

│ ├─source

│ └─syn_rst

│ │ syntmp.msg

│ │ syn_rst.prd

│ │ syn_rst.prj

│ │ syn_rst.v

│ │

│ ├─rev_2

│ │ │ AutoConstraint_syn_rst.sdc

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │ syn_rst.edn

│ │ │ syn_rst.fse

│ │ │ syn_rst.prf

│ │ │ syn_rst.srm

│ │ │ syn_rst.srr

│ │ │ syn_rst.srs

│ │ │ syn_rst.tlg

│ │ │

│ │ ├─par_1

│ │ └─syntmp

│ │ syn_rst.msg

│ │ syn_rst.plg

│ │

│ └─sim

├─Example-4-20

│ │ 示例说明.doc

│ │

│ ├─case

│ │ │ case1.v

│ │ │ syntmp.msg

│ │ │

│ │ ├─PrecisionRTL

│ │ │ │ case.psp

│ │ │ │ case_RTL_schematic.bmp

│ │ │ │ case_schematic.bmp

│ │ │ │

│ │ │ └─case_impl_1

│ │ │ │ case1.edf

│ │ │ │ case1.prf

│ │ │ │ case1.xdb

│ │ │ │ case1_area.rep

│ │ │ │ case1_con_rep.sdc

│ │ │ │ case1_rtl.ixdb

│ │ │ │ case1_tech_con_rep.sdc

│ │ │ │ case1_timing.rep

│ │ │ │ case_impl_1.psi

│ │ │ │ hdlAnalyze_verilogfile

│ │ │ │ precision.log

│ │ │ │ precision_rtl.sdc

│ │ │ │ precision_tech.sdc

│ │ │ │ unfolded_operators.txt

│ │ │ │

│ │ │ ├─rtlc.out

│ │ │ │ │ .rtlc_compile

│ │ │ │ │ .top

│ │ │ │ │ autotop.conf

│ │ │ │ │ legalmodmap.db

│ │ │ │ │ rtlc.args

│ │ │ │ │ rtlc_args1.file

│ │ │ │ │ vmw.mem_contents

│ │ │ │ │

│ │ │ │ ├─depend

│ │ │ │ │ TOPMODULE.list

│ │ │ │ │

│ │ │ │ ├─EXEM_MACRO_DIR

│ │ │ │ ├─INCR

│ │ │ │ │ │ emptymod.list

│ │ │ │ │ │ hier.list

│ │ │ │ │ │ incr_driver.log

│ │ │ │ │ │ incr_rtlc.log

│ │ │ │ │ │

│ │ │ │ │ └─AREA

│ │ │ │ ├─MEM

│ │ │ │ ├─NET

│ │ │ │ └─NM

│ │ │ └─rtlc_libs

│ │ │ └─work

│ │ │ case1.mod

│ │ │ case1.mod.body

│ │ │ rtlc_version_info

│ │ │

│ │ └─SynplifyPro

│ │ │ case1.prd

│ │ │ case1.prj

│ │ │ case_rtl_view.bmp

│ │ │ case_tech_view.bmp

│ │ │

│ │ └─rev_2

│ │ │ AutoConstraint_case1.sdc

│ │ │ case1.edn

│ │ │ case1.fse

│ │ │ case1.prf

│ │ │ case1.srm

│ │ │ case1.srr

│ │ │ case1.srs

│ │ │ case1.tlg

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │

│ │ ├─par_1

│ │ └─syntmp

│ │ case1.msg

│ │ case1.plg

│ │

│ ├─decode

│ │ ├─case

│ │ │ │ case_decode.v

│ │ │ │ decode_case.psp

│ │ │ │ precision_RTL_schematic.bmp

│ │ │ │ precision_schematic.bmp

│ │ │ │ synplify.prd

│ │ │ │ synplify.prj

│ │ │ │ synplify_rtl_view.bmp

│ │ │ │ synplify_tech_view.bmp

│ │ │ │

│ │ │ ├─decode_case_impl_1

│ │ │ │ │ case_decode.edf

│ │ │ │ │ case_decode.prf

│ │ │ │ │ case_decode.xdb

│ │ │ │ │ case_decode_area.rep

│ │ │ │ │ case_decode_con_rep.sdc

│ │ │ │ │ case_decode_rtl.ixdb

│ │ │ │ │ case_decode_tech_con_rep.sdc

│ │ │ │ │ case_decode_timing.rep

│ │ │ │ │ decode_case_impl_1.psi

│ │ │ │ │ hdlAnalyze_verilogfile

│ │ │ │ │ precision.log

│ │ │ │ │ precision_rtl.sdc

│ │ │ │ │ precision_tech.sdc

│ │ │ │ │ unfolded_operators.txt

│ │ │ │ │

│ │ │ │ ├─rtlc.out

│ │ │ │ │ │ .rtlc_compile

│ │ │ │ │ │ .top

│ │ │ │ │ │ autotop.conf

│ │ │ │ │ │ legalmodmap.db

│ │ │ │ │ │ rtlc.args

│ │ │ │ │ │ rtlc_args1.file

│ │ │ │ │ │ vmw.mem_contents

│ │ │ │ │ │

│ │ │ │ │ ├─depend

│ │ │ │ │ │ TOPMODULE.list

│ │ │ │ │ │

│ │ │ │ │ ├─EXEM_MACRO_DIR

│ │ │ │ │ ├─INCR

│ │ │ │ │ │ │ emptymod.list

│ │ │ │ │ │ │ hier.list

│ │ │ │ │ │ │ incr_driver.log

│ │ │ │ │ │ │ incr_rtlc.log

│ │ │ │ │ │ │

│ │ │ │ │ │ └─AREA

│ │ │ │ │ ├─MEM

│ │ │ │ │ ├─NET

│ │ │ │ │ └─NM

│ │ │ │ └─rtlc_libs

│ │ │ │ └─work

│ │ │ │ case_decode.mod

│ │ │ │ case_decode.mod.body

│ │ │ │ rtlc_version_info

│ │ │ │

│ │ │ └─rev_1

│ │ │ │ AutoConstraint_case_decode.sdc

│ │ │ │ case_decode.edn

│ │ │ │ case_decode.fse

│ │ │ │ case_decode.prf

│ │ │ │ case_decode.srm

│ │ │ │ case_decode.srr

│ │ │ │ case_decode.srs

│ │ │ │ case_decode.tlg

│ │ │ │ generic.fse

│ │ │ │ generic.srd

│ │ │ │

│ │ │ └─syntmp

│ │ │ case_decode.msg

│ │ │ case_decode.plg

│ │ │

│ │ ├─if_mult

│ │ │ │ if_mult_decode.prd

│ │ │ │ if_mult_decode.prj

│ │ │ │ if_mult_decode.v

│ │ │ │ if_mult_decode_RTL_veiw.bmp

│ │ │ │ if_mult_decode_tech_veiw.bmp

│ │ │ │ if_mult_RTL_schematic.bmp

│ │ │ │ if_mult_schematic.bmp

│ │ │ │ precision.psp

│ │ │ │

│ │ │ ├─precision_impl_1

│ │ │ │ │ hdlAnalyze_verilogfile

│ │ │ │ │ if_mult_decode.edf

│ │ │ │ │ if_mult_decode.prf

│ │ │ │ │ if_mult_decode.xdb

│ │ │ │ │ if_mult_decode_area.rep

│ │ │ │ │ if_mult_decode_con_rep.sdc

│ │ │ │ │ if_mult_decode_rtl.ixdb

│ │ │ │ │ if_mult_decode_tech_con_rep.sdc

│ │ │ │ │ if_mult_decode_timing.rep

│ │ │ │ │ precision.log

│ │ │ │ │ precision_impl_1.psi

│ │ │ │ │ precision_rtl.sdc

│ │ │ │ │ precision_tech.sdc

│ │ │ │ │ unfolded_operators.txt

│ │ │ │ │

│ │ │ │ ├─rtlc.out

│ │ │ │ │ │ .rtlc_compile

│ │ │ │ │ │ .top

│ │ │ │ │ │ autotop.conf

│ │ │ │ │ │ legalmodmap.db

│ │ │ │ │ │ rtlc.args

│ │ │ │ │ │ rtlc_args1.file

│ │ │ │ │ │ vmw.mem_contents

│ │ │ │ │ │

│ │ │ │ │ ├─depend

│ │ │ │ │ │ TOPMODULE.list

│ │ │ │ │ │

│ │ │ │ │ ├─EXEM_MACRO_DIR

│ │ │ │ │ ├─INCR

│ │ │ │ │ │ │ emptymod.list

│ │ │ │ │ │ │ hier.list

│ │ │ │ │ │ │ incr_driver.log

│ │ │ │ │ │ │ incr_rtlc.log

│ │ │ │ │ │ │

│ │ │ │ │ │ └─AREA

│ │ │ │ │ ├─MEM

│ │ │ │ │ ├─NET

│ │ │ │ │ └─NM

│ │ │ │ └─rtlc_libs

│ │ │ │ └─work

│ │ │ │ if_mult_decode.mod

│ │ │ │ if_mult_decode.mod.body

│ │ │ │ rtlc_version_info

│ │ │ │

│ │ │ └─rev_2

│ │ │ │ AutoConstraint_if_mult_decode.sdc

│ │ │ │ generic.fse

│ │ │ │ generic.srd

│ │ │ │ if_mult_decode.edn

│ │ │ │ if_mult_decode.fse

│ │ │ │ if_mult_decode.prf

│ │ │ │ if_mult_decode.srm

│ │ │ │ if_mult_decode.srr

│ │ │ │ if_mult_decode.srs

│ │ │ │ if_mult_decode.tlg

│ │ │ │

│ │ │ └─syntmp

│ │ │ if_mult_decode.msg

│ │ │ if_mult_decode.plg

│ │ │

│ │ └─if_single

│ │ │ if_single_decode.prd

│ │ │ if_single_decode.prj

│ │ │ if_single_decode.v

│ │ │ if_single_decode_RTL_view.bmp

│ │ │ if_single_decode_tech_view.bmp

│ │ │ if_single_RTL_schematic.bmp

│ │ │ if_single_schematic.bmp

│ │ │ precision.log

│ │ │ precision.psp

│ │ │

│ │ ├─precision_impl_1

│ │ │ │ hdlAnalyze_verilogfile

│ │ │ │ if_single_decode.edf

│ │ │ │ if_single_decode.prf

│ │ │ │ if_single_decode.xdb

│ │ │ │ if_single_decode_area.rep

│ │ │ │ if_single_decode_con_rep.sdc

│ │ │ │ if_single_decode_rtl.ixdb

│ │ │ │ if_single_decode_tech_con_rep.sdc

│ │ │ │ if_single_decode_timing.rep

│ │ │ │ precision.log

│ │ │ │ precision_impl_1.psi

│ │ │ │ precision_rtl.sdc

│ │ │ │ precision_tech.sdc

│ │ │ │ unfolded_operators.txt

│ │ │ │

│ │ │ ├─rtlc.out

│ │ │ │ │ .rtlc_compile

│ │ │ │ │ .top

│ │ │ │ │ autotop.conf

│ │ │ │ │ legalmodmap.db

│ │ │ │ │ rtlc.args

│ │ │ │ │ rtlc_args1.file

│ │ │ │ │ vmw.mem_contents

│ │ │ │ │

│ │ │ │ ├─depend

│ │ │ │ │ TOPMODULE.list

│ │ │ │ │

│ │ │ │ ├─EXEM_MACRO_DIR

│ │ │ │ ├─INCR

│ │ │ │ │ │ emptymod.list

│ │ │ │ │ │ hier.list

│ │ │ │ │ │ incr_driver.log

│ │ │ │ │ │ incr_rtlc.log

│ │ │ │ │ │

│ │ │ │ │ └─AREA

│ │ │ │ ├─MEM

│ │ │ │ ├─NET

│ │ │ │ └─NM

│ │ │ └─rtlc_libs

│ │ │ └─work

│ │ │ if_single_decode.mod

│ │ │ if_single_decode.mod.body

│ │ │ rtlc_version_info

│ │ │

│ │ └─rev_1

│ │ │ AutoConstraint_if_single_decode.sdc

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │ if_single_decode.edn

│ │ │ if_single_decode.fse

│ │ │ if_single_decode.prf

│ │ │ if_single_decode.srm

│ │ │ if_single_decode.srr

│ │ │ if_single_decode.srs

│ │ │ if_single_decode.tlg

│ │ │

│ │ └─syntmp

│ │ if_single_decode.msg

│ │ if_single_decode.plg

│ │

│ ├─if_mult

│ │ │ latch_mult_if.v

│ │ │ mult_if.v

│ │ │

│ │ ├─Latch_if_mult

│ │ │ │ latch_if_mult.prd

│ │ │ │ latch_if_mult.prj

│ │ │ │ latch_mult_if.v

│ │ │ │ Latch_Synplify_RTL_view.bmp

│ │ │ │ Latch_Synplify_tech_view.bmp

│ │ │ │

│ │ │ └─rev_2

│ │ │ │ AutoConstraint_mult_if.sdc

│ │ │ │ generic.fse

│ │ │ │ generic.srd

│ │ │ │ latch_mult_if.edn

│ │ │ │ latch_mult_if.fse

│ │ │ │ latch_mult_if.prf

│ │ │ │ latch_mult_if.srm

│ │ │ │ latch_mult_if.srr

│ │ │ │ latch_mult_if.srs

│ │ │ │ latch_mult_if.tlg

│ │ │ │

│ │ │ └─syntmp

│ │ │ latch_mult_if.msg

│ │ │ latch_mult_if.plg

│ │ │

│ │ ├─PrecisionRTL

│ │ │ │ if_mult.psp

│ │ │ │ if_mult_RTL_schematic.bmp

│ │ │ │ if_mult_schematic.bmp

│ │ │ │

│ │ │ └─if_mult_impl_1

│ │ │ │ hdlAnalyze_verilogfile

│ │ │ │ if_mult_impl_1.psi

│ │ │ │ mult_if.edf

│ │ │ │ mult_if.prf

│ │ │ │ mult_if.xdb

│ │ │ │ mult_if_area.rep

│ │ │ │ mult_if_con_rep.sdc

│ │ │ │ mult_if_rtl.ixdb

│ │ │ │ mult_if_tech_con_rep.sdc

│ │ │ │ mult_if_timing.rep

│ │ │ │ precision.log

│ │ │ │ precision_rtl.sdc

│ │ │ │ precision_tech.sdc

│ │ │ │ unfolded_operators.txt

│ │ │ │

│ │ │ ├─rtlc.out

│ │ │ │ │ .rtlc_compile

│ │ │ │ │ .top

│ │ │ │ │ autotop.conf

│ │ │ │ │ legalmodmap.db

│ │ │ │ │ rtlc.args

│ │ │ │ │ rtlc_args1.file

│ │ │ │ │ vmw.mem_contents

│ │ │ │ │

│ │ │ │ ├─depend

│ │ │ │ │ TOPMODULE.list

│ │ │ │ │

│ │ │ │ ├─EXEM_MACRO_DIR

│ │ │ │ ├─INCR

│ │ │ │ │ │ emptymod.list

│ │ │ │ │ │ hier.list

│ │ │ │ │ │ incr_driver.log

│ │ │ │ │ │ incr_rtlc.log

│ │ │ │ │ │

│ │ │ │ │ └─AREA

│ │ │ │ ├─MEM

│ │ │ │ ├─NET

│ │ │ │ └─NM

│ │ │ └─rtlc_libs

│ │ │ └─work

│ │ │ mult_if.mod

│ │ │ mult_if.mod.body

│ │ │ rtlc_version_info

│ │ │

│ │ └─SynplifyPro

│ │ │ if_mult.prd

│ │ │ if_mult.prj

│ │ │ if_mult_rtl_view.bmp

│ │ │ if_mult_tech_view.bmp

│ │ │ syntmp.msg

│ │ │

│ │ └─rev_1

│ │ │ AutoConstraint_mult_if.sdc

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │ mult_if.edn

│ │ │ mult_if.fse

│ │ │ mult_if.prf

│ │ │ mult_if.srm

│ │ │ mult_if.srr

│ │ │ mult_if.srs

│ │ │ mult_if.tlg

│ │ │

│ │ └─syntmp

│ │ mult_if.msg

│ │ mult_if.plg

│ │

│ └─if_single

│ │ single_if.v

│ │

│ ├─PrecisionRTL

│ │ │ if_single.psp

│ │ │ if_single_RTL_schemaitc.bmp

│ │ │ if_single_schematic.bmp

│ │ │

│ │ └─if_single_impl_1

│ │ │ hdlAnalyze_verilogfile

│ │ │ if_single_impl_1.psi

│ │ │ precision.log

│ │ │ precision_rtl.sdc

│ │ │ precision_tech.sdc

│ │ │ single_if.edf

│ │ │ single_if.prf

│ │ │ single_if.xdb

│ │ │ single_if_area.rep

│ │ │ single_if_con_rep.sdc

│ │ │ single_if_rtl.ixdb

│ │ │ single_if_tech_con_rep.sdc

│ │ │ single_if_timing.rep

│ │ │ unfolded_operators.txt

│ │ │

│ │ ├─rtlc.out

│ │ │ │ .rtlc_compile

│ │ │ │ .top

│ │ │ │ autotop.conf

│ │ │ │ legalmodmap.db

│ │ │ │ rtlc.args

│ │ │ │ rtlc_args1.file

│ │ │ │ vmw.mem_contents

│ │ │ │

│ │ │ ├─depend

│ │ │ │ TOPMODULE.list

│ │ │ │

│ │ │ ├─EXEM_MACRO_DIR

│ │ │ ├─INCR

│ │ │ │ │ emptymod.list

│ │ │ │ │ hier.list

│ │ │ │ │ incr_driver.log

│ │ │ │ │ incr_rtlc.log

│ │ │ │ │

│ │ │ │ └─AREA

│ │ │ ├─MEM

│ │ │ ├─NET

│ │ │ └─NM

│ │ └─rtlc_libs

│ │ └─work

│ │ rtlc_version_info

│ │ single_if.mod

│ │ single_if.mod.body

│ │

│ └─SynplifyPro

│ │ if_single.prd

│ │ if_single.prj

│ │ if_single_rtl_view.bmp

│ │ if_single_tech_view.bmp

│ │ syntmp.msg

│ │

│ └─rev_2

│ │ AutoConstraint_single_if.sdc

│ │ generic.fse

│ │ generic.srd

│ │ single_if.edn

│ │ single_if.fse

│ │ single_if.prf

│ │ single_if.srm

│ │ single_if.srr

│ │ single_if.srs

│ │ single_if.tlg

│ │

│ └─syntmp

│ single_if.msg

│ single_if.plg

│

├─Example-4-21

│ │ 示例说明.doc

│ │

│ ├─asyn_bad

│ │ │ asyn_bad.prd

│ │ │ asyn_bad.prj

│ │ │ decode.v

│ │ │ read_reg.v

│ │ │ top.v

│ │ │ write_reg.v

│ │ │

│ │ └─rev_1

│ │ │ AutoConstraint_top.sdc

│ │ │ decode.edn

│ │ │ decode.fse

│ │ │ decode.prf

│ │ │ decode.srm

│ │ │ decode.srr

│ │ │ decode.srs

│ │ │ decode.tlg

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │

│ │ └─syntmp

│ │ decode.msg

│ │ decode.plg

│ │

│ ├─oe_edge

│ │ │ decode.v

│ │ │ oe_edge.prd

│ │ │ oe_edge.prj

│ │ │ read_reg.v

│ │ │ top.v

│ │ │ write_reg.v

│ │ │

│ │ └─rev_2

│ │ │ AutoConstraint_top.sdc

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │ top.edn

│ │ │ top.fse

│ │ │ top.prf

│ │ │ top.srm

│ │ │ top.srr

│ │ │ top.srs

│ │ │ top.tlg

│ │ │

│ │ └─syntmp

│ │ top.msg

│ │ top.plg

│ │

│ └─syn_wr

│ │ decode.v

│ │ read_reg.v

│ │ syntmp.msg

│ │ syn_wr.prd

│ │ syn_wr.prj

│ │ top.v

│ │ write_reg.v

│ │

│ └─rev_1

│ │ generic.fse

│ │ generic.srd

│ │ top.edn

│ │ top.fse

│ │ top.prf

│ │ top.srm

│ │ top.srr

│ │ top.srs

│ │ top.tlg

│ │

│ └─syntmp

│ top.msg

│ top.plg

│

├─Example-4-4

│ │ reg_counter.prd

│ │ reg_counter.prj

│ │ reg_counter.v

│ │ 示例说明.doc

│ │

│ ├─rev_2

│ │ │ reg_counter.edf

│ │ │ reg_counter.fse

│ │ │ reg_counter.ncf

│ │ │ reg_counter.srd

│ │ │ reg_counter.srm

│ │ │ reg_counter.srr

│ │ │ reg_counter.srs

│ │ │ reg_counter.tlg

│ │ │ rpt_reg_counter.areasrr

│ │ │ rpt_reg_counter_areasrr.htm

│ │ │

│ │ ├─par_1

│ │ ├─syntmp

│ │ │ reg_counter.msg

│ │ │ reg_counter.plg

│ │ │

│ │ └─verif

│ │ reg_counter.vif

│ │

│ ├─sim

│ │ reg_counter.v

│ │

│ └─source

│ reg_counter.v

│

├─Example-4-7

│ │ clock_edge.prd

│ │ clock_edge.prj

│ │ clock_edge.v

│ │ syntmp.msg

│ │ 示例说明.doc

│ │

│ ├─rev_2

│ │ │ clock_edge.edn

│ │ │ clock_edge.fse

│ │ │ clock_edge.prf

│ │ │ clock_edge.srm

│ │ │ clock_edge.srr

│ │ │ clock_edge.srs

│ │ │ clock_edge.tlg

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │

│ │ ├─par_1

│ │ └─syntmp

│ │ clock_edge.msg

│ │ clock_edge.plg

│ │

│ ├─sim

│ │ │ clock_edge.v

│ │ │ clock_edge_tb.v

│ │ │ sim_clock_edge.cr.mti

│ │ │ sim_clock_edge.mpf

│ │ │ transcript

│ │ │ vsim.wlf

│ │ │ wave.do

│ │ │

│ │ └─work

│ │ │ _info

│ │ │

│ │ ├─clock_edge

│ │ │ verilog.asm

│ │ │ _primary.dat

│ │ │ _primary.vhd

│ │ │

│ │ └─clock_edge_tb

│ │ verilog.asm

│ │ _primary.dat

│ │ _primary.vhd

│ │

│ └─source

│ clock_edge.v

│ clock_edge_tb.v

│

├─Example-4-8

│ │ decode_cmb.prd

│ │ decode_cmb.prj

│ │ decode_cmb.v

│ │ decode_cmb2.v

│ │ 示例说明.doc

│ │

│ ├─rev_2

│ │ │ decode_cmb.edn

│ │ │ decode_cmb.fse

│ │ │ decode_cmb.prf

│ │ │ decode_cmb.srm

│ │ │ decode_cmb.srr

│ │ │ decode_cmb.srs

│ │ │ decode_cmb.tlg

│ │ │ decode_cmb2.edn

│ │ │ decode_cmb2.fse

│ │ │ decode_cmb2.prf

│ │ │ decode_cmb2.srm

│ │ │ decode_cmb2.srr

│ │ │ decode_cmb2.srs

│ │ │ decode_cmb2.tlg

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │

│ │ └─syntmp

│ │ decode_cmb.plg

│ │ decode_cmb2.msg

│ │ decode_cmb2.plg

│ │

│ ├─sim

│ │ │ decode_cmb.cr.mti

│ │ │ decode_cmb.mpf

│ │ │ decode_cmb.v

│ │ │ decode_cmb2.v

│ │ │ decode_cmb_tb.v

│ │ │ transcript

│ │ │ vsim.wlf

│ │ │

│ │ └─work

│ │ │ _info

│ │ │

│ │ ├─decode_cmb

│ │ │ verilog.asm

│ │ │ _primary.dat

│ │ │ _primary.vhd

│ │ │

│ │ ├─decode_cmb2

│ │ │ verilog.asm

│ │ │ _primary.dat

│ │ │ _primary.vhd

│ │ │

│ │ └─decode_cmb_tb

│ │ verilog.asm

│ │ _primary.dat

│ │ _primary.vhd

│ │

│ └─source

│ decode_cmb.v

│ decode_cmb2.v

│ decode_cmb_tb.v

│

├─Example-5-1

│ │ FHTPART_resource.bmp

│ │ FHTPART_resource.gif

│ │ wchfht_resource.bmp

│ │ wchfht_resource.gif

│ │ workspace_VS.prd

│ │ workspace_VS.prj

│ │ 示例说明.doc

│ │

│ ├─after_optimized

│ │ │ after_optimized.prd

│ │ │ after_optimized.prj

│ │ │ wch_fht.v

│ │ │

│ │ └─rev_2

│ │ │ wch_fht.fse

│ │ │ wch_fht.srd

│ │ │ wch_fht.srm

│ │ │ wch_fht.srr

│ │ │ wch_fht.srs

│ │ │ wch_fht.sxr

│ │ │ wch_fht.tcl

│ │ │ wch_fht.tlg

│ │ │ wch_fht.vqm

│ │ │ wch_fht.xrf

│ │ │ wch_fht_cons.tcl

│ │ │ wch_fht_rm.tcl

│ │ │

│ │ └─syntmp

│ │ wch_fht.plg

│ │

│ ├─before_optimized

│ │ │ before_optimized.prd

│ │ │ before_optimized.prj

│ │ │ fhtpart.v

│ │ │ fht_unit1.v

│ │ │ fht_unit2.v

│ │ │ fht_unit3.v

│ │ │ fht_unit4.v

│ │ │

│ │ └─rev_1

│ │ │ AutoConstraint_fhtpart.sdc

│ │ │ fhtpart.fse

│ │ │ fhtpart.srd

│ │ │ fhtpart.srm

│ │ │ fhtpart.srr

│ │ │ fhtpart.srs

│ │ │ fhtpart.sxr

│ │ │ fhtpart.tcl

│ │ │ fhtpart.tlg

│ │ │ fhtpart.vqm

│ │ │ fhtpart.xrf

│ │ │ fhtpart_cons.tcl

│ │ │ fhtpart_rm.tcl

│ │ │

│ │ └─syntmp

│ │ fhtpart.plg

│ │

│ └─soure

│ ├─after_optimized

│ │ wch_fht.v

│ │

│ └─before_optimized

│ fhtpart.v

│ fht_unit1.v

│ fht_unit2.v

│ fht_unit3.v

│ fht_unit4.v

│

├─Example-5-5

│ │ latch.prd

│ │ latch.prj

│ │ latch.v

│ │ syntmp.msg

│ │ 示例说明.doc

│ │

│ ├─rev_2

│ │ │ AutoConstraint_latch.sdc

│ │ │ latch.edf

│ │ │ latch.fse

│ │ │ latch.ncf

│ │ │ latch.srd

│ │ │ latch.srm

│ │ │ latch.srr

│ │ │ latch.srs

│ │ │ latch.tlg

│ │ │ rpt_latch.areasrr

│ │ │ rpt_latch_areasrr.htm

│ │ │

│ │ ├─par_1

│ │ ├─syntmp

│ │ │ latch.msg

│ │ │ latch.plg

│ │ │

│ │ └─verif

│ │ latch.vif

│ │

│ └─source

│ latch.v

│

├─Example-5-6

│ │ resource_share.prd

│ │ resource_share.prj

│ │ 示例说明.doc

│ │

│ ├─rev_1

│ │ │ AutoConstraint_resource_share1.sdc

│ │ │ AutoConstraint_resource_share2.sdc

│ │ │ resource_share1.fse

│ │ │ resource_share1.srd

│ │ │ resource_share1.srm

│ │ │ resource_share1.srr

│ │ │ resource_share1.srs

│ │ │ resource_share1.sxr

│ │ │ resource_share1.tcl

│ │ │ resource_share1.tlg

│ │ │ resource_share1.vqm

│ │ │ resource_share1.xrf

│ │ │ resource_share1_cons.tcl

│ │ │ resource_share1_rm.tcl

│ │ │ resource_share2.fse

│ │ │ resource_share2.srd

│ │ │ resource_share2.srm

│ │ │ resource_share2.srr

│ │ │ resource_share2.srs

│ │ │ resource_share2.sxr

│ │ │ resource_share2.tcl

│ │ │ resource_share2.tlg

│ │ │ resource_share2.vqm

│ │ │ resource_share2.xrf

│ │ │ resource_share2_cons.tcl

│ │ │ resource_share2_rm.tcl

│ │ │ rpt_resource_share1.areasrr

│ │ │ rpt_resource_share1_areasrr.htm

│ │ │ rpt_resource_share2.areasrr

│ │ │ rpt_resource_share2_areasrr.htm

│ │ │

│ │ ├─syntmp

│ │ │ resource_share1.msg

│ │ │ resource_share1.plg

│ │ │ resource_share1_cons_ui.tcl

│ │ │ resource_share2.plg

│ │ │ resource_share2_cons_ui.tcl

│ │ │

│ │ └─verif

│ │ resource_share1.vif

│ │ resource_share2.vif

│ │

│ └─source

│ resource_share1.v

│ resource_share2.v

│ syntmp.msg

│

├─Example-5-7

│ │ mod_copy.prd

│ │ mod_copy.prj

│ │ 示例说明.doc

│ │

│ ├─rev_1

│ │ │ AutoConstraint_mod_copy1.sdc

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │ mod_copy1.edn

│ │ │ mod_copy1.fse

│ │ │ mod_copy1.prf

│ │ │ mod_copy1.srm

│ │ │ mod_copy1.srr

│ │ │ mod_copy1.srs

│ │ │ mod_copy1.tlg

│ │ │ mod_copy2.edn

│ │ │ mod_copy2.fse

│ │ │ mod_copy2.prf

│ │ │ mod_copy2.srm

│ │ │ mod_copy2.srr

│ │ │ mod_copy2.srs

│ │ │ mod_copy2.tlg

│ │ │

│ │ ├─par_1

│ │ └─syntmp

│ │ mod_copy1.msg

│ │ mod_copy1.plg

│ │ mod_copy2.plg

│ │ proj.msg

│ │

│ └─source

│ mod_copy1.v

│ mod_copy2.v

│ syntmp.msg

│

├─Example-5-8

│ │ shannon.prd

│ │ shannon.prj

│ │ 示例说明.doc

│ │

│ ├─rev_2

│ │ │ AutoConstraint_shannon_fast.sdc

│ │ │ AutoConstraint_un_shannon.sdc

│ │ │ rpt_shannon_fast.areasrr

│ │ │ rpt_shannon_fast_areasrr.htm

│ │ │ rpt_un_shannon.areasrr

│ │ │ rpt_un_shannon_areasrr.htm

│ │ │ shannon_fast.fse

│ │ │ shannon_fast.srd

│ │ │ shannon_fast.srm

│ │ │ shannon_fast.srr

│ │ │ shannon_fast.srs

│ │ │ shannon_fast.sxr

│ │ │ shannon_fast.tcl

│ │ │ shannon_fast.tlg

│ │ │ shannon_fast.vqm

│ │ │ shannon_fast.xrf

│ │ │ shannon_fast_cons.tcl

│ │ │ shannon_fast_rm.tcl

│ │ │ un_shannon.fse

│ │ │ un_shannon.srd

│ │ │ un_shannon.srm

│ │ │ un_shannon.srr

│ │ │ un_shannon.srs

│ │ │ un_shannon.sxr

│ │ │ un_shannon.tcl

│ │ │ un_shannon.tlg

│ │ │ un_shannon.vqm

│ │ │ un_shannon.xrf

│ │ │ un_shannon_cons.tcl

│ │ │ un_shannon_rm.tcl

│ │ │

│ │ ├─syntmp

│ │ │ shannon_fast.plg

│ │ │ shannon_fast_cons_ui.tcl

│ │ │ un_shannon.msg

│ │ │ un_shannon.plg

│ │ │ un_shannon_cons_ui.tcl

│ │ │

│ │ └─verif

│ │ shannon_fast.vif

│ │ un_shannon.vif

│ │

│ └─source

│ shannon_fast.v

│ syntmp.msg

│ un_shannon.v

│

├─Example-6-1

│ │ 示例说明.doc

│ │

│ └─FSM

│ ├─state1

│ │ │ state1.prd

│ │ │ state1.prj

│ │ │ state1.v

│ │ │ syntmp.msg

│ │ │

│ │ └─rev_1

│ │ │ AutoConstraint_state1.sdc

│ │ │ fsmviewer.fsm

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │ NS.txt

│ │ │ state1.edn

│ │ │ state1.fse

│ │ │ state1.prf

│ │ │ state1.srm

│ │ │ state1.srr

│ │ │ state1.srs

│ │ │ state1.tlg

│ │ │ state1.vqm

│ │ │

│ │ ├─syntmp

│ │ │ state1.msg

│ │ │ state1.plg

│ │ │

│ │ └─verif

│ │ state1.vif

│ │

│ ├─state2

│ │ │ state2.prd

│ │ │ state2.prj

│ │ │ state2.v

│ │ │ syntmp.msg

│ │ │

│ │ └─rev_1

│ │ │ AutoConstraint_state2.sdc

│ │ │ CS.txt

│ │ │ fsmviewer.fsm

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │ rpt_state2.areasrr

│ │ │ rpt_state2_areasrr.htm

│ │ │ state2.edn

│ │ │ state2.fse

│ │ │ state2.prf

│ │ │ state2.srd

│ │ │ state2.srm

│ │ │ state2.srr

│ │ │ state2.srs

│ │ │ state2.sxr

│ │ │ state2.tcl

│ │ │ state2.tlg

│ │ │ state2.vqm

│ │ │ state2.xrf

│ │ │ state2_cons.tcl

│ │ │ state2_fsm.sdc

│ │ │ state2_rm.tcl

│ │ │

│ │ ├─syntmp

│ │ │ fsm_tmp_cons_ui.tcl

│ │ │ state2.msg

│ │ │ state2.plg

│ │ │ state2_cons_ui.tcl

│ │ │

│ │ └─verif

│ │ state2.vif

│ │

│ ├─state3

│ │ │ state3.prd

│ │ │ state3.prj

│ │ │ state3.v

│ │ │

│ │ └─rev_2

│ │ │ AutoConstraint_state2.sdc

│ │ │ CS.txt

│ │ │ fsmviewer.fsm

│ │ │ generic.fse

│ │ │ generic.srd

│ │ │ state3.edn

│ │ │ state3.fse

│ │ │ state3.prf

│ │ │ state3.srm

│ │ │ state3.srr

│ │ │ state3.srs

│ │ │ state3.tlg

│ │ │

│ │ └─syntmp

│ │ state3.msg

│ │ state3.plg

│ │

│ └─state_default

│ │ state2_default.v

│ │ state_default.prd

│ │ state_default.prj

│ │

│ └─rev_2

│ │ AutoConstraint_state2_default.sdc

│ │ CS.txt

│ │ fsmviewer.fsm

│ │ generic.fse

│ │ generic.srd

│ │ state2_default.edn

│ │ state2_default.fse

│ │ state2_default.prf

│ │ state2_default.srm

│ │ state2_default.srr

│ │ state2_default.srs

│ │ state2_default.tlg

│ │

│ └─syntmp

│ state2_default.plg

│

├─Example-7-1

│ │ 示例说明.doc

│ │

│ └─Proj

│ altera_mf.v

│ MPI.v

│ NorTestBench.v

│ sim.do

│ SPRAM.v

│ STM.v

│ Testbench_readme.txt

│ wave.do

│

├─Example-7-2

│ │ 示例说明.doc

│ │

│ └─Proj

│ altera_mf.v

│ MPI.v

│ NorTestBench.v

│ Read_In_File.txt

│ sim.do

│ SPRAM.v

│ STM.v

│ Testbench_readme.txt

│ wave.do

│

├─Example-7-3

│ │ 示例说明.doc

│ │

│ └─Proj

│ altera_mf.v

│ harness.v

│ MPI.v

│ NorTestBench.v

│ Read_In_File.txt

│ sim.do

│ SPRAM.v

│ STM.v

│ testcase.v

│ uP_BFM.v

│ wave.do

│

├─Example-7-4

│ │ 示例说明.doc

│ │

│ └─Proj

│ altera_mf.v

│ harness.v

│ MPI.v

│ NorTestBench.v

│ Read_In_File.txt

│ Sim.do

│ SPRAM.v

│ STM.v

│ testcase.v

│ uP_BFM.v

│ wave.do

│

├─Example-8-1

│ │ 示例说明.doc

│ │

│ └─sim

│ INV_DFF.v

│ sim.do

│

└─Example-8-2

│ 示例说明.doc

│

├─Blocking_LHS_Delay

│ sim.do

│ tb.v

│ wave.do

│

├─Blocking_RHS_Delay

│ sim.do

│ tb.v

│ wave.do

│

├─NonBlocking_LHS_Delay

│ sim.do

│ tb.v

│ wave.do

│

└─NonBlocking_RHS_Delay

sim.do

tb.v

wave.do

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论