实例介绍

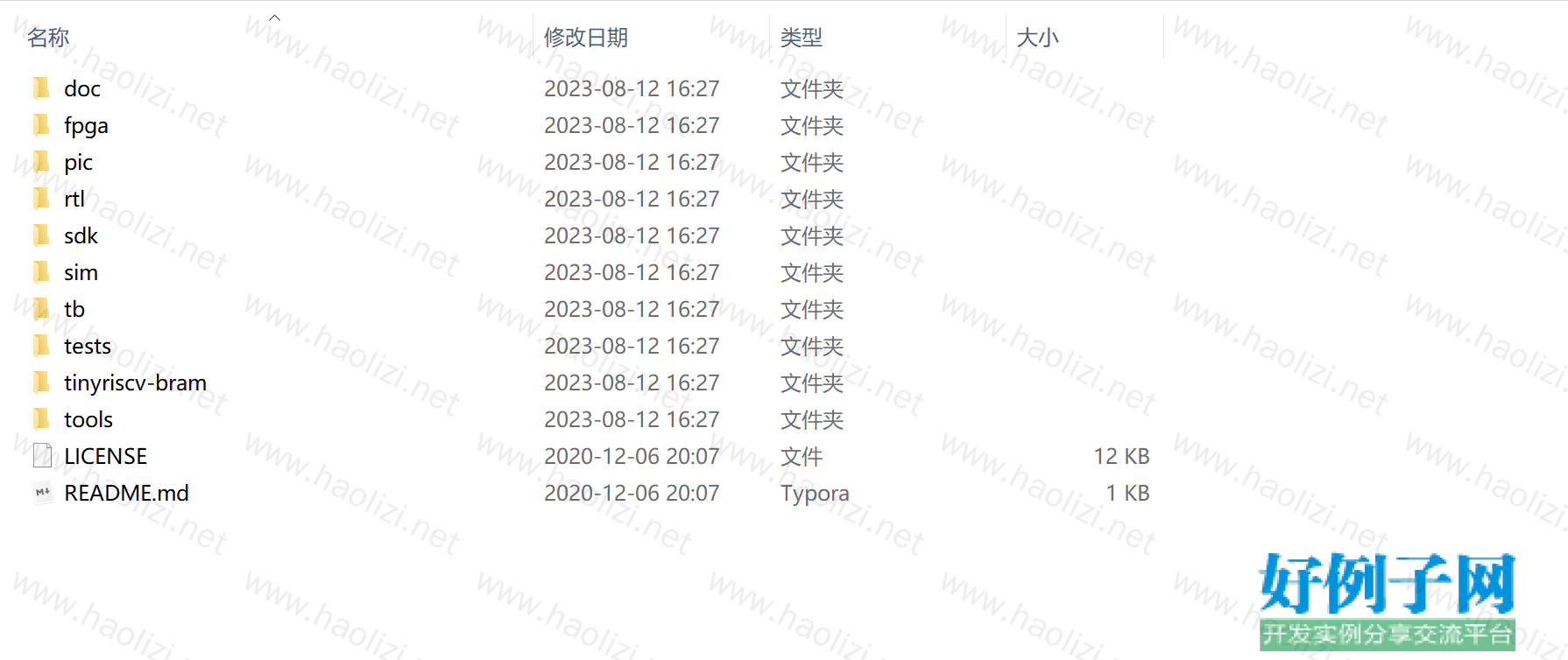

【实例截图】

【核心代码】

.

├── RISC-V源代码.rar

└── tinyriscv-a1

├── LICENSE

├── README.md

├── doc

│ ├── RISC-V-Reader-Chinese-v2p1.pdf

│ ├── riscv-debug-release.pdf

│ ├── riscv-privileged.pdf

│ └── riscv-spec.pdf

├── fpga

│ ├── README.md

│ ├── constrs

│ │ └── tinyriscv.xdc

│ └── images

│ ├── add_mcs_device.png

│ ├── add_sim.png

│ ├── add_src_1.png

│ ├── add_src_2.png

│ ├── add_src_3.png

│ ├── add_src_4.png

│ ├── add_src_5.png

│ ├── add_src_6.png

│ ├── add_src_7.png

│ ├── add_src_8.png

│ ├── config_mcs.png

│ ├── create_prj_1.png

│ ├── create_prj_2.png

│ ├── create_prj_3.png

│ ├── create_prj_4.png

│ ├── create_prj_5.png

│ ├── create_prj_6.png

│ ├── create_prj_7.png

│ ├── defines.png

│ ├── download_1.png

│ ├── download_2.png

│ ├── download_3.png

│ ├── download_4.png

│ ├── mcs_ok.png

│ ├── mcs_prog.png

│ ├── openocd.png

│ ├── openocd_cli.png

│ ├── select_spi.png

│ └── uart_debug.png

├── pic

│ ├── addr_alloc.jpg

│ ├── arch.jpg

│ ├── new_test_output.png

│ ├── other_coremark.png

│ ├── test_output.png

│ └── tinyriscv_coremark.png

├── rtl

│ ├── core

│ │ ├── I_cache.v

│ │ ├── bpu.v

│ │ ├── clint.v

│ │ ├── csr_reg.v

│ │ ├── defines.v

│ │ ├── divider.v

│ │ ├── exu.v

│ │ ├── exu_alu_datapath.v

│ │ ├── exu_commit.v

│ │ ├── exu_dispatch.v

│ │ ├── exu_mem.v

│ │ ├── exu_muldiv.v

│ │ ├── gpr_reg.v

│ │ ├── idu.v

│ │ ├── idu_exu.v

│ │ ├── ifu.v

│ │ ├── ifu_idu.v

│ │ ├── pipe_ctrl.v

│ │ ├── rst_ctrl.v

│ │ └── tinyriscv_core.v

│ ├── debug

│ │ ├── jtag_dm.v

│ │ ├── jtag_driver.v

│ │ └── jtag_top.v

│ ├── perips

│ │ ├── gpio.v

│ │ ├── ram.v

│ │ ├── rom.v

│ │ ├── timer.v

│ │ └── uart.v

│ ├── sys_bus

│ │ └── rib.v

│ ├── top

│ │ └── tinyriscv_soc_top.v

│ └── utils

│ ├── full_handshake_rx.v

│ ├── full_handshake_tx.v

│ ├── gen_buf.v

│ ├── gen_dff.v

│ ├── gen_ram.v

│ └── vld_rdy.v

├── sdk

│ ├── README.md

│ ├── bsp

│ │ ├── README.md

│ │ ├── common.mk

│ │ ├── include

│ │ │ ├── gpio.h

│ │ │ ├── timer.h

│ │ │ ├── trap_code.h

│ │ │ ├── uart.h

│ │ │ ├── utils.h

│ │ │ └── xprintf.h

│ │ ├── init.c

│ │ ├── init.o

│ │ ├── lib

│ │ │ ├── uart.c

│ │ │ ├── uart.o

│ │ │ ├── utils.c

│ │ │ ├── utils.o

│ │ │ ├── xprintf.c

│ │ │ └── xprintf.o

│ │ ├── link.lds

│ │ ├── start.S

│ │ ├── start.o

│ │ ├── trap_entry.S

│ │ ├── trap_entry.o

│ │ ├── trap_handler.c

│ │ └── trap_handler.o

│ └── examples

│ ├── FreeRTOS

│ │ ├── Demo

│ │ │ └── tinyriscv_GCC

│ │ └── Source

│ │ ├── croutine.c

│ │ ├── event_groups.c

│ │ ├── include

│ │ ├── list.c

│ │ ├── portable

│ │ ├── queue.c

│ │ ├── readme.txt

│ │ ├── stream_buffer.c

│ │ ├── tasks.c

│ │ └── timers.c

│ ├── README.md

│ ├── coremark

│ │ ├── Makefile

│ │ ├── core_list_join.c

│ │ ├── core_list_join.o

│ │ ├── core_main.c

│ │ ├── core_main.o

│ │ ├── core_matrix.c

│ │ ├── core_matrix.o

│ │ ├── core_portme.c

│ │ ├── core_portme.h

│ │ ├── core_portme.o

│ │ ├── core_state.c

│ │ ├── core_state.o

│ │ ├── core_util.c

│ │ ├── core_util.o

│ │ ├── coremark

│ │ ├── coremark.bin

│ │ ├── coremark.dump

│ │ └── coremark.h

│ ├── gpio

│ │ ├── Makefile

│ │ ├── README.md

│ │ ├── gpio

│ │ ├── gpio.bin

│ │ ├── gpio.dump

│ │ ├── main.c

│ │ └── main.o

│ ├── simple

│ │ ├── Makefile

│ │ ├── README.md

│ │ └── main.c

│ ├── timer_int

│ │ ├── Makefile

│ │ ├── README.md

│ │ └── main.c

│ ├── uart_rx

│ │ ├── Makefile

│ │ ├── README.md

│ │ └── main.c

│ └── uart_tx

│ ├── Makefile

│ ├── README.md

│ ├── main.c

│ ├── main.o

│ ├── uart_tx

│ ├── uart_tx.bin

│ └── uart_tx.dump

├── sim

│ ├── README.md

│ ├── compile_rtl.py

│ ├── compliance_test

│ │ ├── README.md

│ │ ├── compliance_test.py

│ │ ├── inst.data

│ │ ├── out.vvp

│ │ ├── run.log

│ │ ├── signature.output

│ │ └── tinyriscv_soc_tb.vcd

│ ├── inst.data

│ ├── out.vvp

│ ├── sim_default_nowave.py

│ ├── sim_new_nowave.py

│ ├── test_all_isa.py

│ ├── test_jtag.py

│ └── tinyriscv_soc_tb.vcd

├── tb

│ ├── README.md

│ ├── compliance_test

│ │ └── tinyriscv_soc_tb.v

│ ├── jtag_tb.v

│ └── tinyriscv_soc_tb.v

├── tests

│ ├── README.md

│ ├── isa

│ │ ├── Makefile

│ │ ├── README.md

│ │ ├── generated

│ │ │ ├── rv32ui-p-add

│ │ │ ├── rv32ui-p-add.bin

│ │ │ ├── rv32ui-p-add.dump

│ │ │ ├── rv32ui-p-add.verilog

│ │ │ ├── rv32ui-p-addi

│ │ │ ├── rv32ui-p-addi.bin

│ │ │ ├── rv32ui-p-addi.dump

│ │ │ ├── rv32ui-p-addi.verilog

│ │ │ ├── rv32ui-p-and

│ │ │ ├── rv32ui-p-and.bin

│ │ │ ├── rv32ui-p-and.dump

│ │ │ ├── rv32ui-p-and.verilog

│ │ │ ├── rv32ui-p-andi

│ │ │ ├── rv32ui-p-andi.bin

│ │ │ ├── rv32ui-p-andi.dump

│ │ │ ├── rv32ui-p-andi.verilog

│ │ │ ├── rv32ui-p-auipc

│ │ │ ├── rv32ui-p-auipc.bin

│ │ │ ├── rv32ui-p-auipc.dump

│ │ │ ├── rv32ui-p-auipc.verilog

│ │ │ ├── rv32ui-p-beq

│ │ │ ├── rv32ui-p-beq.bin

│ │ │ ├── rv32ui-p-beq.dump

│ │ │ ├── rv32ui-p-beq.verilog

│ │ │ ├── rv32ui-p-bge

│ │ │ ├── rv32ui-p-bge.bin

│ │ │ ├── rv32ui-p-bge.dump

│ │ │ ├── rv32ui-p-bge.verilog

│ │ │ ├── rv32ui-p-bgeu

│ │ │ ├── rv32ui-p-bgeu.bin

│ │ │ ├── rv32ui-p-bgeu.dump

│ │ │ ├── rv32ui-p-bgeu.verilog

│ │ │ ├── rv32ui-p-blt

│ │ │ ├── rv32ui-p-blt.bin

│ │ │ ├── rv32ui-p-blt.dump

│ │ │ ├── rv32ui-p-blt.verilog

│ │ │ ├── rv32ui-p-bltu

│ │ │ ├── rv32ui-p-bltu.bin

│ │ │ ├── rv32ui-p-bltu.dump

│ │ │ ├── rv32ui-p-bltu.verilog

│ │ │ ├── rv32ui-p-bne

│ │ │ ├── rv32ui-p-bne.bin

│ │ │ ├── rv32ui-p-bne.dump

│ │ │ ├── rv32ui-p-bne.verilog

│ │ │ ├── rv32ui-p-fence_i

│ │ │ ├── rv32ui-p-fence_i.bin

│ │ │ ├── rv32ui-p-fence_i.dump

│ │ │ ├── rv32ui-p-fence_i.verilog

│ │ │ ├── rv32ui-p-jal

│ │ │ ├── rv32ui-p-jal.bin

│ │ │ ├── rv32ui-p-jal.dump

│ │ │ ├── rv32ui-p-jal.verilog

│ │ │ ├── rv32ui-p-jalr

│ │ │ ├── rv32ui-p-jalr.bin

│ │ │ ├── rv32ui-p-jalr.dump

│ │ │ ├── rv32ui-p-jalr.verilog

│ │ │ ├── rv32ui-p-lb

│ │ │ ├── rv32ui-p-lb.bin

│ │ │ ├── rv32ui-p-lb.dump

│ │ │ ├── rv32ui-p-lb.verilog

│ │ │ ├── rv32ui-p-lbu

│ │ │ ├── rv32ui-p-lbu.bin

│ │ │ ├── rv32ui-p-lbu.dump

│ │ │ ├── rv32ui-p-lbu.verilog

│ │ │ ├── rv32ui-p-lh

│ │ │ ├── rv32ui-p-lh.bin

│ │ │ ├── rv32ui-p-lh.dump

│ │ │ ├── rv32ui-p-lh.verilog

│ │ │ ├── rv32ui-p-lhu

│ │ │ ├── rv32ui-p-lhu.bin

│ │ │ ├── rv32ui-p-lhu.dump

│ │ │ ├── rv32ui-p-lhu.verilog

│ │ │ ├── rv32ui-p-lui

│ │ │ ├── rv32ui-p-lui.bin

│ │ │ ├── rv32ui-p-lui.dump

│ │ │ ├── rv32ui-p-lui.verilog

│ │ │ ├── rv32ui-p-lw

│ │ │ ├── rv32ui-p-lw.bin

│ │ │ ├── rv32ui-p-lw.dump

│ │ │ ├── rv32ui-p-lw.verilog

│ │ │ ├── rv32ui-p-or

│ │ │ ├── rv32ui-p-or.bin

│ │ │ ├── rv32ui-p-or.dump

│ │ │ ├── rv32ui-p-or.verilog

│ │ │ ├── rv32ui-p-ori

│ │ │ ├── rv32ui-p-ori.bin

│ │ │ ├── rv32ui-p-ori.dump

│ │ │ ├── rv32ui-p-ori.verilog

│ │ │ ├── rv32ui-p-sb

│ │ │ ├── rv32ui-p-sb.bin

│ │ │ ├── rv32ui-p-sb.dump

│ │ │ ├── rv32ui-p-sb.verilog

│ │ │ ├── rv32ui-p-sh

│ │ │ ├── rv32ui-p-sh.bin

│ │ │ ├── rv32ui-p-sh.dump

│ │ │ ├── rv32ui-p-sh.verilog

│ │ │ ├── rv32ui-p-simple

│ │ │ ├── rv32ui-p-simple.bin

│ │ │ ├── rv32ui-p-simple.dump

│ │ │ ├── rv32ui-p-simple.verilog

│ │ │ ├── rv32ui-p-sll

│ │ │ ├── rv32ui-p-sll.bin

│ │ │ ├── rv32ui-p-sll.dump

│ │ │ ├── rv32ui-p-sll.verilog

│ │ │ ├── rv32ui-p-slli

│ │ │ ├── rv32ui-p-slli.bin

│ │ │ ├── rv32ui-p-slli.dump

│ │ │ ├── rv32ui-p-slli.verilog

│ │ │ ├── rv32ui-p-slt

│ │ │ ├── rv32ui-p-slt.bin

│ │ │ ├── rv32ui-p-slt.dump

│ │ │ ├── rv32ui-p-slt.verilog

│ │ │ ├── rv32ui-p-slti

│ │ │ ├── rv32ui-p-slti.bin

│ │ │ ├── rv32ui-p-slti.dump

│ │ │ ├── rv32ui-p-slti.verilog

│ │ │ ├── rv32ui-p-sltiu

│ │ │ ├── rv32ui-p-sltiu.bin

│ │ │ ├── rv32ui-p-sltiu.dump

│ │ │ ├── rv32ui-p-sltiu.verilog

│ │ │ ├── rv32ui-p-sltu

│ │ │ ├── rv32ui-p-sltu.bin

│ │ │ ├── rv32ui-p-sltu.dump

│ │ │ ├── rv32ui-p-sltu.verilog

│ │ │ ├── rv32ui-p-sra

│ │ │ ├── rv32ui-p-sra.bin

│ │ │ ├── rv32ui-p-sra.dump

│ │ │ ├── rv32ui-p-sra.verilog

│ │ │ ├── rv32ui-p-srai

│ │ │ ├── rv32ui-p-srai.bin

│ │ │ ├── rv32ui-p-srai.dump

│ │ │ ├── rv32ui-p-srai.verilog

│ │ │ ├── rv32ui-p-srl

│ │ │ ├── rv32ui-p-srl.bin

│ │ │ ├── rv32ui-p-srl.dump

│ │ │ ├── rv32ui-p-srl.verilog

│ │ │ ├── rv32ui-p-srli

│ │ │ ├── rv32ui-p-srli.bin

│ │ │ ├── rv32ui-p-srli.dump

│ │ │ ├── rv32ui-p-srli.verilog

│ │ │ ├── rv32ui-p-sub

│ │ │ ├── rv32ui-p-sub.bin

│ │ │ ├── rv32ui-p-sub.dump

│ │ │ ├── rv32ui-p-sub.verilog

│ │ │ ├── rv32ui-p-sw

│ │ │ ├── rv32ui-p-sw.bin

│ │ │ ├── rv32ui-p-sw.dump

│ │ │ ├── rv32ui-p-sw.verilog

│ │ │ ├── rv32ui-p-xor

│ │ │ ├── rv32ui-p-xor.bin

│ │ │ ├── rv32ui-p-xor.dump

│ │ │ ├── rv32ui-p-xor.verilog

│ │ │ ├── rv32ui-p-xori

│ │ │ ├── rv32ui-p-xori.bin

│ │ │ ├── rv32ui-p-xori.dump

│ │ │ ├── rv32ui-p-xori.verilog

│ │ │ ├── rv32um-p-div

│ │ │ ├── rv32um-p-div.bin

│ │ │ ├── rv32um-p-div.dump

│ │ │ ├── rv32um-p-div.verilog

│ │ │ ├── rv32um-p-divu

│ │ │ ├── rv32um-p-divu.bin

│ │ │ ├── rv32um-p-divu.dump

│ │ │ ├── rv32um-p-divu.verilog

│ │ │ ├── rv32um-p-mul

│ │ │ ├── rv32um-p-mul.bin

│ │ │ ├── rv32um-p-mul.dump

│ │ │ ├── rv32um-p-mul.verilog

│ │ │ ├── rv32um-p-mulh

│ │ │ ├── rv32um-p-mulh.bin

│ │ │ ├── rv32um-p-mulh.dump

│ │ │ ├── rv32um-p-mulh.verilog

│ │ │ ├── rv32um-p-mulhsu

│ │ │ ├── rv32um-p-mulhsu.bin

│ │ │ ├── rv32um-p-mulhsu.dump

│ │ │ ├── rv32um-p-mulhsu.verilog

│ │ │ ├── rv32um-p-mulhu

│ │ │ ├── rv32um-p-mulhu.bin

│ │ │ ├── rv32um-p-mulhu.dump

│ │ │ ├── rv32um-p-mulhu.verilog

│ │ │ ├── rv32um-p-rem

│ │ │ ├── rv32um-p-rem.bin

│ │ │ ├── rv32um-p-rem.dump

│ │ │ ├── rv32um-p-rem.verilog

│ │ │ ├── rv32um-p-remu

│ │ │ ├── rv32um-p-remu.bin

│ │ │ ├── rv32um-p-remu.dump

│ │ │ └── rv32um-p-remu.verilog

│ │ ├── link.ld

│ │ ├── riscv_test.h

│ │ ├── rv32ui

│ │ │ ├── Makefrag

│ │ │ ├── add.S

│ │ │ ├── addi.S

│ │ │ ├── and.S

│ │ │ ├── andi.S

│ │ │ ├── auipc.S

│ │ │ ├── beq.S

│ │ │ ├── bge.S

│ │ │ ├── bgeu.S

│ │ │ ├── blt.S

│ │ │ ├── bltu.S

│ │ │ ├── bne.S

│ │ │ ├── fence_i.S

│ │ │ ├── jal.S

│ │ │ ├── jalr.S

│ │ │ ├── lb.S

│ │ │ ├── lbu.S

│ │ │ ├── ld.S

│ │ │ ├── lh.S

│ │ │ ├── lhu.S

│ │ │ ├── lui.S

│ │ │ ├── lw.S

│ │ │ ├── lwu.S

│ │ │ ├── or.S

│ │ │ ├── ori.S

│ │ │ ├── sb.S

│ │ │ ├── sd.S

│ │ │ ├── sh.S

│ │ │ ├── simple.S

│ │ │ ├── sll.S

│ │ │ ├── slli.S

│ │ │ ├── slt.S

│ │ │ ├── slti.S

│ │ │ ├── sltiu.S

│ │ │ ├── sltu.S

│ │ │ ├── sra.S

│ │ │ ├── srai.S

│ │ │ ├── srl.S

│ │ │ ├── srli.S

│ │ │ ├── sub.S

│ │ │ ├── sw.S

│ │ │ ├── xor.S

│ │ │ └── xori.S

│ │ ├── rv32um

│ │ │ ├── Makefrag

│ │ │ ├── div.S

│ │ │ ├── divu.S

│ │ │ ├── mul.S

│ │ │ ├── mulh.S

│ │ │ ├── mulhsu.S

│ │ │ ├── mulhu.S

│ │ │ ├── rem.S

│ │ │ └── remu.S

│ │ └── test_macros.h

│ └── riscv-compliance

│ ├── COPYING.BSD

│ ├── COPYING.CC

│ ├── ChangeLog

│ ├── Makefile

│ ├── README.md

│ ├── build_generated

│ │ ├── rv32Zicsr

│ │ │ ├── I-CSRRC-01.elf

│ │ │ ├── I-CSRRC-01.elf.bin

│ │ │ ├── I-CSRRC-01.elf.objdump

│ │ │ ├── I-CSRRCI-01.elf

│ │ │ ├── I-CSRRCI-01.elf.bin

│ │ │ ├── I-CSRRCI-01.elf.objdump

│ │ │ ├── I-CSRRS-01.elf

│ │ │ ├── I-CSRRS-01.elf.bin

│ │ │ ├── I-CSRRS-01.elf.objdump

│ │ │ ├── I-CSRRSI-01.elf

│ │ │ ├── I-CSRRSI-01.elf.bin

│ │ │ ├── I-CSRRSI-01.elf.objdump

│ │ │ ├── I-CSRRW-01.elf

│ │ │ ├── I-CSRRW-01.elf.bin

│ │ │ ├── I-CSRRW-01.elf.objdump

│ │ │ ├── I-CSRRWI-01.elf

│ │ │ ├── I-CSRRWI-01.elf.bin

│ │ │ └── I-CSRRWI-01.elf.objdump

│ │ ├── rv32Zifencei

│ │ │ ├── I-FENCE.I-01.elf

│ │ │ ├── I-FENCE.I-01.elf.bin

│ │ │ └── I-FENCE.I-01.elf.objdump

│ │ ├── rv32i

│ │ │ ├── I-ADD-01.elf

│ │ │ ├── I-ADD-01.elf.bin

│ │ │ ├── I-ADD-01.elf.objdump

│ │ │ ├── I-ADDI-01.elf

│ │ │ ├── I-ADDI-01.elf.bin

│ │ │ ├── I-ADDI-01.elf.objdump

│ │ │ ├── I-AND-01.elf

│ │ │ ├── I-AND-01.elf.bin

│ │ │ ├── I-AND-01.elf.objdump

│ │ │ ├── I-ANDI-01.elf

│ │ │ ├── I-ANDI-01.elf.bin

│ │ │ ├── I-ANDI-01.elf.objdump

│ │ │ ├── I-AUIPC-01.elf

│ │ │ ├── I-AUIPC-01.elf.bin

│ │ │ ├── I-AUIPC-01.elf.objdump

│ │ │ ├── I-BEQ-01.elf

│ │ │ ├── I-BEQ-01.elf.bin

│ │ │ ├── I-BEQ-01.elf.objdump

│ │ │ ├── I-BGE-01.elf

│ │ │ ├── I-BGE-01.elf.bin

│ │ │ ├── I-BGE-01.elf.objdump

│ │ │ ├── I-BGEU-01.elf

│ │ │ ├── I-BGEU-01.elf.bin

│ │ │ ├── I-BGEU-01.elf.objdump

│ │ │ ├── I-BLT-01.elf

│ │ │ ├── I-BLT-01.elf.bin

│ │ │ ├── I-BLT-01.elf.objdump

│ │ │ ├── I-BLTU-01.elf

│ │ │ ├── I-BLTU-01.elf.bin

│ │ │ ├── I-BLTU-01.elf.objdump

│ │ │ ├── I-BNE-01.elf

│ │ │ ├── I-BNE-01.elf.bin

│ │ │ ├── I-BNE-01.elf.objdump

│ │ │ ├── I-DELAY_SLOTS-01.elf

│ │ │ ├── I-DELAY_SLOTS-01.elf.bin

│ │ │ ├── I-DELAY_SLOTS-01.elf.objdump

│ │ │ ├── I-EBREAK-01.elf

│ │ │ ├── I-EBREAK-01.elf.bin

│ │ │ ├── I-EBREAK-01.elf.objdump

│ │ │ ├── I-ECALL-01.elf

│ │ │ ├── I-ECALL-01.elf.bin

│ │ │ ├── I-ECALL-01.elf.objdump

│ │ │ ├── I-ENDIANESS-01.elf

│ │ │ ├── I-ENDIANESS-01.elf.bin

│ │ │ ├── I-ENDIANESS-01.elf.objdump

│ │ │ ├── I-IO-01.elf

│ │ │ ├── I-IO-01.elf.bin

│ │ │ ├── I-IO-01.elf.objdump

│ │ │ ├── I-JAL-01.elf

│ │ │ ├── I-JAL-01.elf.bin

│ │ │ ├── I-JAL-01.elf.objdump

│ │ │ ├── I-JALR-01.elf

│ │ │ ├── I-JALR-01.elf.bin

│ │ │ ├── I-JALR-01.elf.objdump

│ │ │ ├── I-LB-01.elf

│ │ │ ├── I-LB-01.elf.bin

│ │ │ ├── I-LB-01.elf.objdump

│ │ │ ├── I-LBU-01.elf

│ │ │ ├── I-LBU-01.elf.bin

│ │ │ ├── I-LBU-01.elf.objdump

│ │ │ ├── I-LH-01.elf

│ │ │ ├── I-LH-01.elf.bin

│ │ │ ├── I-LH-01.elf.objdump

│ │ │ ├── I-LHU-01.elf

│ │ │ ├── I-LHU-01.elf.bin

│ │ │ ├── I-LHU-01.elf.objdump

│ │ │ ├── I-LUI-01.elf

│ │ │ ├── I-LUI-01.elf.bin

│ │ │ ├── I-LUI-01.elf.objdump

│ │ │ ├── I-LW-01.elf

│ │ │ ├── I-LW-01.elf.bin

│ │ │ ├── I-LW-01.elf.objdump

│ │ │ ├── I-MISALIGN_JMP-01.elf

│ │ │ ├── I-MISALIGN_JMP-01.elf.bin

│ │ │ ├── I-MISALIGN_JMP-01.elf.objdump

│ │ │ ├── I-MISALIGN_LDST-01.elf

│ │ │ ├── I-MISALIGN_LDST-01.elf.bin

│ │ │ ├── I-MISALIGN_LDST-01.elf.objdump

│ │ │ ├── I-NOP-01.elf

│ │ │ ├── I-NOP-01.elf.bin

│ │ │ ├── I-NOP-01.elf.objdump

│ │ │ ├── I-OR-01.elf

│ │ │ ├── I-OR-01.elf.bin

│ │ │ ├── I-OR-01.elf.objdump

│ │ │ ├── I-ORI-01.elf

│ │ │ ├── I-ORI-01.elf.bin

│ │ │ ├── I-ORI-01.elf.objdump

│ │ │ ├── I-RF_size-01.elf

│ │ │ ├── I-RF_size-01.elf.bin

│ │ │ ├── I-RF_size-01.elf.objdump

│ │ │ ├── I-RF_width-01.elf

│ │ │ ├── I-RF_width-01.elf.bin

│ │ │ ├── I-RF_width-01.elf.objdump

│ │ │ ├── I-RF_x0-01.elf

│ │ │ ├── I-RF_x0-01.elf.bin

│ │ │ ├── I-RF_x0-01.elf.objdump

│ │ │ ├── I-SB-01.elf

│ │ │ ├── I-SB-01.elf.bin

│ │ │ ├── I-SB-01.elf.objdump

│ │ │ ├── I-SH-01.elf

│ │ │ ├── I-SH-01.elf.bin

│ │ │ ├── I-SH-01.elf.objdump

│ │ │ ├── I-SLL-01.elf

│ │ │ ├── I-SLL-01.elf.bin

│ │ │ ├── I-SLL-01.elf.objdump

│ │ │ ├── I-SLLI-01.elf

│ │ │ ├── I-SLLI-01.elf.bin

│ │ │ ├── I-SLLI-01.elf.objdump

│ │ │ ├── I-SLT-01.elf

│ │ │ ├── I-SLT-01.elf.bin

│ │ │ ├── I-SLT-01.elf.objdump

│ │ │ ├── I-SLTI-01.elf

│ │ │ ├── I-SLTI-01.elf.bin

│ │ │ ├── I-SLTI-01.elf.objdump

│ │ │ ├── I-SLTIU-01.elf

│ │ │ ├── I-SLTIU-01.elf.bin

│ │ │ ├── I-SLTIU-01.elf.objdump

│ │ │ ├── I-SLTU-01.elf

│ │ │ ├── I-SLTU-01.elf.bin

│ │ │ ├── I-SLTU-01.elf.objdump

│ │ │ ├── I-SRA-01.elf

│ │ │ ├── I-SRA-01.elf.bin

│ │ │ ├── I-SRA-01.elf.objdump

│ │ │ ├── I-SRAI-01.elf

│ │ │ ├── I-SRAI-01.elf.bin

│ │ │ ├── I-SRAI-01.elf.objdump

│ │ │ ├── I-SRL-01.elf

│ │ │ ├── I-SRL-01.elf.bin

│ │ │ ├── I-SRL-01.elf.objdump

│ │ │ ├── I-SRLI-01.elf

│ │ │ ├── I-SRLI-01.elf.bin

│ │ │ ├── I-SRLI-01.elf.objdump

│ │ │ ├── I-SUB-01.elf

│ │ │ ├── I-SUB-01.elf.bin

│ │ │ ├── I-SUB-01.elf.objdump

│ │ │ ├── I-SW-01.elf

│ │ │ ├── I-SW-01.elf.bin

│ │ │ ├── I-SW-01.elf.objdump

│ │ │ ├── I-XOR-01.elf

│ │ │ ├── I-XOR-01.elf.bin

│ │ │ ├── I-XOR-01.elf.objdump

│ │ │ ├── I-XORI-01.elf

│ │ │ ├── I-XORI-01.elf.bin

│ │ │ └── I-XORI-01.elf.objdump

│ │ └── rv32im

│ │ ├── DIV.elf

│ │ ├── DIV.elf.bin

│ │ ├── DIV.elf.objdump

│ │ ├── DIVU.elf

│ │ ├── DIVU.elf.bin

│ │ ├── DIVU.elf.objdump

│ │ ├── MUL.elf

│ │ ├── MUL.elf.bin

│ │ ├── MUL.elf.objdump

│ │ ├── MULH.elf

│ │ ├── MULH.elf.bin

│ │ ├── MULH.elf.objdump

│ │ ├── MULHSU.elf

│ │ ├── MULHSU.elf.bin

│ │ ├── MULHSU.elf.objdump

│ │ ├── MULHU.elf

│ │ ├── MULHU.elf.bin

│ │ ├── MULHU.elf.objdump

│ │ ├── REM.elf

│ │ ├── REM.elf.bin

│ │ ├── REM.elf.objdump

│ │ ├── REMU.elf

│ │ ├── REMU.elf.bin

│ │ └── REMU.elf.objdump

│ ├── doc

│ │ ├── ChangeLog

│ │ ├── Makefile

│ │ ├── README.adoc

│ │ └── custom.wordlist

│ ├── riscv-target

│ │ └── tinyriscv

│ │ ├── README.md

│ │ ├── compliance_io.h

│ │ ├── compliance_test.h

│ │ └── device

│ ├── riscv-test-env

│ │ ├── LICENSE

│ │ ├── encoding.h

│ │ ├── p

│ │ │ ├── link.ld

│ │ │ └── riscv_test.h

│ │ ├── riscv_test_macros.h

│ │ └── test_macros.h

│ ├── riscv-test-suite

│ │ ├── README.md

│ │ ├── rv32Zicsr

│ │ │ ├── Makefile

│ │ │ ├── Makefrag

│ │ │ ├── references

│ │ │ └── src

│ │ ├── rv32Zifencei

│ │ │ ├── Makefile

│ │ │ ├── Makefrag

│ │ │ ├── references

│ │ │ └── src

│ │ ├── rv32i

│ │ │ ├── Makefile

│ │ │ ├── Makefrag

│ │ │ ├── coverage

│ │ │ ├── references

│ │ │ └── src

│ │ └── rv32im

│ │ ├── Makefile

│ │ ├── Makefrag

│ │ ├── coverage

│ │ ├── references

│ │ └── src

│ └── spec

│ ├── TestFormatSpec.adoc

│ ├── TestFormatSpec.pdf

│ └── testpool.jpg

├── tinyriscv-bram

│ ├── LICENSE

│ ├── README.md

│ ├── doc

│ │ ├── RISC-V-Reader-Chinese-v2p1.pdf

│ │ ├── riscv-debug-release.pdf

│ │ ├── riscv-privileged.pdf

│ │ └── riscv-spec.pdf

│ ├── fpga

│ │ ├── README.md

│ │ ├── constrs

│ │ │ └── tinyriscv.xdc

│ │ └── images

│ │ ├── add_mcs_device.png

│ │ ├── add_sim.png

│ │ ├── add_src_1.png

│ │ ├── add_src_2.png

│ │ ├── add_src_3.png

│ │ ├── add_src_4.png

│ │ ├── add_src_5.png

│ │ ├── add_src_6.png

│ │ ├── add_src_7.png

│ │ ├── add_src_8.png

│ │ ├── config_mcs.png

│ │ ├── create_prj_1.png

│ │ ├── create_prj_2.png

│ │ ├── create_prj_3.png

│ │ ├── create_prj_4.png

│ │ ├── create_prj_5.png

│ │ ├── create_prj_6.png

│ │ ├── create_prj_7.png

│ │ ├── defines.png

│ │ ├── download_1.png

│ │ ├── download_2.png

│ │ ├── download_3.png

│ │ ├── download_4.png

│ │ ├── mcs_ok.png

│ │ ├── mcs_prog.png

│ │ ├── openocd.png

│ │ ├── openocd_cli.png

│ │ ├── select_spi.png

│ │ └── uart_debug.png

│ ├── pic

│ │ ├── addr_alloc.jpg

│ │ ├── arch.jpg

│ │ ├── new_test_output.png

│ │ ├── other_coremark.png

│ │ ├── test_output.png

│ │ └── tinyriscv_coremark.png

│ ├── rtl

│ │ ├── core

│ │ │ ├── clint.v

│ │ │ ├── csr_reg.v

│ │ │ ├── defines.v

│ │ │ ├── divider.v

│ │ │ ├── exu.v

│ │ │ ├── exu_alu_datapath.v

│ │ │ ├── exu_commit.v

│ │ │ ├── exu_dispatch.v

│ │ │ ├── exu_mem.v

│ │ │ ├── exu_muldiv.v

│ │ │ ├── gpr_reg.v

│ │ │ ├── idu.v

│ │ │ ├── idu_exu.v

│ │ │ ├── ifu.v

│ │ │ ├── ifu_idu.v

│ │ │ ├── pipe_ctrl.v

│ │ │ ├── rst_ctrl.v

│ │ │ └── tinyriscv_core.v

│ │ ├── debug

│ │ │ ├── jtag_dm.v

│ │ │ ├── jtag_driver.v

│ │ │ └── jtag_top.v

│ │ ├── perips

│ │ │ ├── gpio.v

│ │ │ ├── ram.v

│ │ │ ├── rom.v

│ │ │ ├── timer.v

│ │ │ └── uart.v

│ │ ├── sys_bus

│ │ │ └── rib.v

│ │ ├── top

│ │ │ └── tinyriscv_soc_top.v

│ │ └── utils

│ │ ├── full_handshake_rx.v

│ │ ├── full_handshake_tx.v

│ │ ├── gen_buf.v

│ │ ├── gen_dff.v

│ │ ├── gen_ram.v

│ │ └── vld_rdy.v

│ ├── sdk

│ │ ├── README.md

│ │ ├── bsp

│ │ │ ├── README.md

│ │ │ ├── common.mk

│ │ │ ├── include

│ │ │ │ ├── gpio.h

│ │ │ │ ├── timer.h

│ │ │ │ ├── trap_code.h

│ │ │ │ ├── uart.h

│ │ │ │ ├── utils.h

│ │ │ │ └── xprintf.h

│ │ │ ├── init.c

│ │ │ ├── lib

│ │ │ │ ├── uart.c

│ │ │ │ ├── utils.c

│ │ │ │ └── xprintf.c

│ │ │ ├── link.lds

│ │ │ ├── start.S

│ │ │ ├── trap_entry.S

│ │ │ └── trap_handler.c

│ │ └── examples

│ │ ├── FreeRTOS

│ │ │ ├── Demo

│ │ │ └── Source

│ │ ├── README.md

│ │ ├── coremark

│ │ │ ├── Makefile

│ │ │ ├── core_list_join.c

│ │ │ ├── core_main.c

│ │ │ ├── core_matrix.c

│ │ │ ├── core_portme.c

│ │ │ ├── core_portme.h

│ │ │ ├── core_state.c

│ │ │ ├── core_util.c

│ │ │ └── coremark.h

│ │ ├── gpio

│ │ │ ├── Makefile

│ │ │ ├── README.md

│ │ │ └── main.c

│ │ ├── simple

│ │ │ ├── Makefile

│ │ │ ├── README.md

│ │ │ └── main.c

│ │ ├── timer_int

│ │ │ ├── Makefile

│ │ │ ├── README.md

│ │ │ └── main.c

│ │ ├── uart_rx

│ │ │ ├── Makefile

│ │ │ ├── README.md

│ │ │ └── main.c

│ │ └── uart_tx

│ │ ├── Makefile

│ │ ├── README.md

│ │ └── main.c

│ ├── sim

│ │ ├── README.md

│ │ ├── compile_rtl.py

│ │ ├── compliance_test

│ │ │ ├── README.md

│ │ │ └── compliance_test.py

│ │ ├── sim_default_nowave.py

│ │ ├── sim_new_nowave.py

│ │ ├── test_all_isa.py

│ │ └── test_jtag.py

│ ├── tb

│ │ ├── README.md

│ │ ├── compliance_test

│ │ │ └── tinyriscv_soc_tb.v

│ │ ├── jtag_tb.v

│ │ └── tinyriscv_soc_tb.v

│ ├── tests

│ │ ├── README.md

│ │ ├── isa

│ │ │ ├── Makefile

│ │ │ ├── README.md

│ │ │ ├── generated

│ │ │ │ ├── rv32ui-p-add

│ │ │ │ ├── rv32ui-p-add.bin

│ │ │ │ ├── rv32ui-p-add.dump

│ │ │ │ ├── rv32ui-p-add.verilog

│ │ │ │ ├── rv32ui-p-addi

│ │ │ │ ├── rv32ui-p-addi.bin

│ │ │ │ ├── rv32ui-p-addi.dump

│ │ │ │ ├── rv32ui-p-addi.verilog

│ │ │ │ ├── rv32ui-p-and

│ │ │ │ ├── rv32ui-p-and.bin

│ │ │ │ ├── rv32ui-p-and.dump

│ │ │ │ ├── rv32ui-p-and.verilog

│ │ │ │ ├── rv32ui-p-andi

│ │ │ │ ├── rv32ui-p-andi.bin

│ │ │ │ ├── rv32ui-p-andi.dump

│ │ │ │ ├── rv32ui-p-andi.verilog

│ │ │ │ ├── rv32ui-p-auipc

│ │ │ │ ├── rv32ui-p-auipc.bin

│ │ │ │ ├── rv32ui-p-auipc.dump

│ │ │ │ ├── rv32ui-p-auipc.verilog

│ │ │ │ ├── rv32ui-p-beq

│ │ │ │ ├── rv32ui-p-beq.bin

│ │ │ │ ├── rv32ui-p-beq.dump

│ │ │ │ ├── rv32ui-p-beq.verilog

│ │ │ │ ├── rv32ui-p-bge

│ │ │ │ ├── rv32ui-p-bge.bin

│ │ │ │ ├── rv32ui-p-bge.dump

│ │ │ │ ├── rv32ui-p-bge.verilog

│ │ │ │ ├── rv32ui-p-bgeu

│ │ │ │ ├── rv32ui-p-bgeu.bin

│ │ │ │ ├── rv32ui-p-bgeu.dump

│ │ │ │ ├── rv32ui-p-bgeu.verilog

│ │ │ │ ├── rv32ui-p-blt

│ │ │ │ ├── rv32ui-p-blt.bin

│ │ │ │ ├── rv32ui-p-blt.dump

│ │ │ │ ├── rv32ui-p-blt.verilog

│ │ │ │ ├── rv32ui-p-bltu

│ │ │ │ ├── rv32ui-p-bltu.bin

│ │ │ │ ├── rv32ui-p-bltu.dump

│ │ │ │ ├── rv32ui-p-bltu.verilog

│ │ │ │ ├── rv32ui-p-bne

│ │ │ │ ├── rv32ui-p-bne.bin

│ │ │ │ ├── rv32ui-p-bne.dump

│ │ │ │ ├── rv32ui-p-bne.verilog

│ │ │ │ ├── rv32ui-p-fence_i

│ │ │ │ ├── rv32ui-p-fence_i.bin

│ │ │ │ ├── rv32ui-p-fence_i.dump

│ │ │ │ ├── rv32ui-p-fence_i.verilog

│ │ │ │ ├── rv32ui-p-jal

│ │ │ │ ├── rv32ui-p-jal.bin

│ │ │ │ ├── rv32ui-p-jal.dump

│ │ │ │ ├── rv32ui-p-jal.verilog

│ │ │ │ ├── rv32ui-p-jalr

│ │ │ │ ├── rv32ui-p-jalr.bin

│ │ │ │ ├── rv32ui-p-jalr.dump

│ │ │ │ ├── rv32ui-p-jalr.verilog

│ │ │ │ ├── rv32ui-p-lb

│ │ │ │ ├── rv32ui-p-lb.bin

│ │ │ │ ├── rv32ui-p-lb.dump

│ │ │ │ ├── rv32ui-p-lb.verilog

│ │ │ │ ├── rv32ui-p-lbu

│ │ │ │ ├── rv32ui-p-lbu.bin

│ │ │ │ ├── rv32ui-p-lbu.dump

│ │ │ │ ├── rv32ui-p-lbu.verilog

│ │ │ │ ├── rv32ui-p-lh

│ │ │ │ ├── rv32ui-p-lh.bin

│ │ │ │ ├── rv32ui-p-lh.dump

│ │ │ │ ├── rv32ui-p-lh.verilog

│ │ │ │ ├── rv32ui-p-lhu

│ │ │ │ ├── rv32ui-p-lhu.bin

│ │ │ │ ├── rv32ui-p-lhu.dump

│ │ │ │ ├── rv32ui-p-lhu.verilog

│ │ │ │ ├── rv32ui-p-lui

│ │ │ │ ├── rv32ui-p-lui.bin

│ │ │ │ ├── rv32ui-p-lui.dump

│ │ │ │ ├── rv32ui-p-lui.verilog

│ │ │ │ ├── rv32ui-p-lw

│ │ │ │ ├── rv32ui-p-lw.bin

│ │ │ │ ├── rv32ui-p-lw.dump

│ │ │ │ ├── rv32ui-p-lw.verilog

│ │ │ │ ├── rv32ui-p-or

│ │ │ │ ├── rv32ui-p-or.bin

│ │ │ │ ├── rv32ui-p-or.dump

│ │ │ │ ├── rv32ui-p-or.verilog

│ │ │ │ ├── rv32ui-p-ori

│ │ │ │ ├── rv32ui-p-ori.bin

│ │ │ │ ├── rv32ui-p-ori.dump

│ │ │ │ ├── rv32ui-p-ori.verilog

│ │ │ │ ├── rv32ui-p-sb

│ │ │ │ ├── rv32ui-p-sb.bin

│ │ │ │ ├── rv32ui-p-sb.dump

│ │ │ │ ├── rv32ui-p-sb.verilog

│ │ │ │ ├── rv32ui-p-sh

│ │ │ │ ├── rv32ui-p-sh.bin

│ │ │ │ ├── rv32ui-p-sh.dump

│ │ │ │ ├── rv32ui-p-sh.verilog

│ │ │ │ ├── rv32ui-p-simple

│ │ │ │ ├── rv32ui-p-simple.bin

│ │ │ │ ├── rv32ui-p-simple.dump

│ │ │ │ ├── rv32ui-p-simple.verilog

│ │ │ │ ├── rv32ui-p-sll

│ │ │ │ ├── rv32ui-p-sll.bin

│ │ │ │ ├── rv32ui-p-sll.dump

│ │ │ │ ├── rv32ui-p-sll.verilog

│ │ │ │ ├── rv32ui-p-slli

│ │ │ │ ├── rv32ui-p-slli.bin

│ │ │ │ ├── rv32ui-p-slli.dump

│ │ │ │ ├── rv32ui-p-slli.verilog

│ │ │ │ ├── rv32ui-p-slt

│ │ │ │ ├── rv32ui-p-slt.bin

│ │ │ │ ├── rv32ui-p-slt.dump

│ │ │ │ ├── rv32ui-p-slt.verilog

│ │ │ │ ├── rv32ui-p-slti

│ │ │ │ ├── rv32ui-p-slti.bin

│ │ │ │ ├── rv32ui-p-slti.dump

│ │ │ │ ├── rv32ui-p-slti.verilog

│ │ │ │ ├── rv32ui-p-sltiu

│ │ │ │ ├── rv32ui-p-sltiu.bin

│ │ │ │ ├── rv32ui-p-sltiu.dump

│ │ │ │ ├── rv32ui-p-sltiu.verilog

│ │ │ │ ├── rv32ui-p-sltu

│ │ │ │ ├── rv32ui-p-sltu.bin

│ │ │ │ ├── rv32ui-p-sltu.dump

│ │ │ │ ├── rv32ui-p-sltu.verilog

│ │ │ │ ├── rv32ui-p-sra

│ │ │ │ ├── rv32ui-p-sra.bin

│ │ │ │ ├── rv32ui-p-sra.dump

│ │ │ │ ├── rv32ui-p-sra.verilog

│ │ │ │ ├── rv32ui-p-srai

│ │ │ │ ├── rv32ui-p-srai.bin

│ │ │ │ ├── rv32ui-p-srai.dump

│ │ │ │ ├── rv32ui-p-srai.verilog

│ │ │ │ ├── rv32ui-p-srl

│ │ │ │ ├── rv32ui-p-srl.bin

│ │ │ │ ├── rv32ui-p-srl.dump

│ │ │ │ ├── rv32ui-p-srl.verilog

│ │ │ │ ├── rv32ui-p-srli

│ │ │ │ ├── rv32ui-p-srli.bin

│ │ │ │ ├── rv32ui-p-srli.dump

│ │ │ │ ├── rv32ui-p-srli.verilog

│ │ │ │ ├── rv32ui-p-sub

│ │ │ │ ├── rv32ui-p-sub.bin

│ │ │ │ ├── rv32ui-p-sub.dump

│ │ │ │ ├── rv32ui-p-sub.verilog

│ │ │ │ ├── rv32ui-p-sw

│ │ │ │ ├── rv32ui-p-sw.bin

│ │ │ │ ├── rv32ui-p-sw.dump

│ │ │ │ ├── rv32ui-p-sw.verilog

│ │ │ │ ├── rv32ui-p-xor

│ │ │ │ ├── rv32ui-p-xor.bin

│ │ │ │ ├── rv32ui-p-xor.dump

│ │ │ │ ├── rv32ui-p-xor.verilog

│ │ │ │ ├── rv32ui-p-xori

│ │ │ │ ├── rv32ui-p-xori.bin

│ │ │ │ ├── rv32ui-p-xori.dump

│ │ │ │ ├── rv32ui-p-xori.verilog

│ │ │ │ ├── rv32um-p-div

│ │ │ │ ├── rv32um-p-div.bin

│ │ │ │ ├── rv32um-p-div.dump

│ │ │ │ ├── rv32um-p-div.verilog

│ │ │ │ ├── rv32um-p-divu

│ │ │ │ ├── rv32um-p-divu.bin

│ │ │ │ ├── rv32um-p-divu.dump

│ │ │ │ ├── rv32um-p-divu.verilog

│ │ │ │ ├── rv32um-p-mul

│ │ │ │ ├── rv32um-p-mul.bin

│ │ │ │ ├── rv32um-p-mul.dump

│ │ │ │ ├── rv32um-p-mul.verilog

│ │ │ │ ├── rv32um-p-mulh

│ │ │ │ ├── rv32um-p-mulh.bin

│ │ │ │ ├── rv32um-p-mulh.dump

│ │ │ │ ├── rv32um-p-mulh.verilog

│ │ │ │ ├── rv32um-p-mulhsu

│ │ │ │ ├── rv32um-p-mulhsu.bin

│ │ │ │ ├── rv32um-p-mulhsu.dump

│ │ │ │ ├── rv32um-p-mulhsu.verilog

│ │ │ │ ├── rv32um-p-mulhu

│ │ │ │ ├── rv32um-p-mulhu.bin

│ │ │ │ ├── rv32um-p-mulhu.dump

│ │ │ │ ├── rv32um-p-mulhu.verilog

│ │ │ │ ├── rv32um-p-rem

│ │ │ │ ├── rv32um-p-rem.bin

│ │ │ │ ├── rv32um-p-rem.dump

│ │ │ │ ├── rv32um-p-rem.verilog

│ │ │ │ ├── rv32um-p-remu

│ │ │ │ ├── rv32um-p-remu.bin

│ │ │ │ ├── rv32um-p-remu.dump

│ │ │ │ └── rv32um-p-remu.verilog

│ │ │ ├── link.ld

│ │ │ ├── riscv_test.h

│ │ │ ├── rv32ui

│ │ │ │ ├── Makefrag

│ │ │ │ ├── add.S

│ │ │ │ ├── addi.S

│ │ │ │ ├── and.S

│ │ │ │ ├── andi.S

│ │ │ │ ├── auipc.S

│ │ │ │ ├── beq.S

│ │ │ │ ├── bge.S

│ │ │ │ ├── bgeu.S

│ │ │ │ ├── blt.S

│ │ │ │ ├── bltu.S

│ │ │ │ ├── bne.S

│ │ │ │ ├── fence_i.S

│ │ │ │ ├── jal.S

│ │ │ │ ├── jalr.S

│ │ │ │ ├── lb.S

│ │ │ │ ├── lbu.S

│ │ │ │ ├── ld.S

│ │ │ │ ├── lh.S

│ │ │ │ ├── lhu.S

│ │ │ │ ├── lui.S

│ │ │ │ ├── lw.S

│ │ │ │ ├── lwu.S

│ │ │ │ ├── or.S

│ │ │ │ ├── ori.S

│ │ │ │ ├── sb.S

│ │ │ │ ├── sd.S

│ │ │ │ ├── sh.S

│ │ │ │ ├── simple.S

│ │ │ │ ├── sll.S

│ │ │ │ ├── slli.S

│ │ │ │ ├── slt.S

│ │ │ │ ├── slti.S

│ │ │ │ ├── sltiu.S

│ │ │ │ ├── sltu.S

│ │ │ │ ├── sra.S

│ │ │ │ ├── srai.S

│ │ │ │ ├── srl.S

│ │ │ │ ├── srli.S

│ │ │ │ ├── sub.S

│ │ │ │ ├── sw.S

│ │ │ │ ├── xor.S

│ │ │ │ └── xori.S

│ │ │ ├── rv32um

│ │ │ │ ├── Makefrag

│ │ │ │ ├── div.S

│ │ │ │ ├── divu.S

│ │ │ │ ├── mul.S

│ │ │ │ ├── mulh.S

│ │ │ │ ├── mulhsu.S

│ │ │ │ ├── mulhu.S

│ │ │ │ ├── rem.S

│ │ │ │ └── remu.S

│ │ │ └── test_macros.h

│ │ └── riscv-compliance

│ │ ├── COPYING.BSD

│ │ ├── COPYING.CC

│ │ ├── ChangeLog

│ │ ├── Makefile

│ │ ├── README.md

│ │ ├── build_generated

│ │ │ ├── rv32Zicsr

│ │ │ ├── rv32Zifencei

│ │ │ ├── rv32i

│ │ │ └── rv32im

│ │ ├── doc

│ │ │ ├── ChangeLog

│ │ │ ├── Makefile

│ │ │ ├── README.adoc

│ │ │ └── custom.wordlist

│ │ ├── riscv-target

│ │ │ └── tinyriscv

│ │ ├── riscv-test-env

│ │ │ ├── LICENSE

│ │ │ ├── encoding.h

│ │ │ ├── p

│ │ │ ├── riscv_test_macros.h

│ │ │ └── test_macros.h

│ │ ├── riscv-test-suite

│ │ │ ├── README.md

│ │ │ ├── rv32Zicsr

│ │ │ ├── rv32Zifencei

│ │ │ ├── rv32i

│ │ │ └── rv32im

│ │ └── spec

│ │ ├── TestFormatSpec.adoc

│ │ ├── TestFormatSpec.pdf

│ │ └── testpool.jpg

│ └── tools

│ ├── BinToMem_CLI.py

│ └── openocd

│ ├── openocd.exe

│ └── tinyriscv_cmsisdap.cfg

└── tools

├── BinToMem_CLI.py

├── gnu-mcu-eclipse-build-tools-2.11-20180428-1604-win64

│ └── GNU MCU Eclipse

│ └── Build Tools

│ └── 2.11-20180428-1604

├── gnu-mcu-eclipse-riscv-none-gcc-8.2.0-2.2-20190521-0004-win64

│ ├── README.md

│ ├── bin

│ │ ├── libiconv-2.dll

│ │ ├── libwinpthread-1.dll

│ │ ├── python27.dll

│ │ ├── riscv-none-embed-addr2line.exe

│ │ ├── riscv-none-embed-ar.exe

│ │ ├── riscv-none-embed-as.exe

│ │ ├── riscv-none-embed-c .exe

│ │ ├── riscv-none-embed-c filt.exe

│ │ ├── riscv-none-embed-cpp.exe

│ │ ├── riscv-none-embed-elfedit.exe

│ │ ├── riscv-none-embed-g .exe

│ │ ├── riscv-none-embed-gcc-8.2.0.exe

│ │ ├── riscv-none-embed-gcc-ar.exe

│ │ ├── riscv-none-embed-gcc-nm.exe

│ │ ├── riscv-none-embed-gcc-ranlib.exe

│ │ ├── riscv-none-embed-gcc.exe

│ │ ├── riscv-none-embed-gcov-dump.exe

│ │ ├── riscv-none-embed-gcov-tool.exe

│ │ ├── riscv-none-embed-gcov.exe

│ │ ├── riscv-none-embed-gdb-add-index

│ │ ├── riscv-none-embed-gdb-add-index-py

│ │ ├── riscv-none-embed-gdb-py.exe

│ │ ├── riscv-none-embed-gdb.exe

│ │ ├── riscv-none-embed-gprof.exe

│ │ ├── riscv-none-embed-ld.bfd.exe

│ │ ├── riscv-none-embed-ld.exe

│ │ ├── riscv-none-embed-nm.exe

│ │ ├── riscv-none-embed-objcopy.exe

│ │ ├── riscv-none-embed-objdump.exe

│ │ ├── riscv-none-embed-ranlib.exe

│ │ ├── riscv-none-embed-readelf.exe

│ │ ├── riscv-none-embed-size.exe

│ │ ├── riscv-none-embed-strings.exe

│ │ └── riscv-none-embed-strip.exe

│ ├── doc

│ │ ├── info

│ │ │ ├── annotate.info

│ │ │ ├── as.info

│ │ │ ├── bfd.info

│ │ │ ├── binutils.info

│ │ │ ├── cpp.info

│ │ │ ├── cppinternals.info

│ │ │ ├── dir

│ │ │ ├── gcc.info

│ │ │ ├── gccinstall.info

│ │ │ ├── gccint.info

│ │ │ ├── gdb.info

│ │ │ ├── gprof.info

│ │ │ ├── ld.info

│ │ │ └── stabs.info

│ │ ├── man

│ │ │ ├── man1

│ │ │ ├── man5

│ │ │ └── man7

│ │ └── pdf

│ │ ├── annotate.pdf

│ │ ├── as.pdf

│ │ ├── bfd.pdf

│ │ ├── binutils.pdf

│ │ ├── gcc

│ │ ├── gdb.pdf

│ │ ├── gprof.pdf

│ │ ├── ld.pdf

│ │ ├── libiberty.pdf

│ │ ├── refcard.pdf

│ │ └── stabs.pdf

│ ├── gnu-mcu-eclipse

│ │ ├── CHANGELOG.txt

│ │ ├── licenses

│ │ │ ├── binutils-2.32

│ │ │ ├── expat-2.2.5

│ │ │ ├── gcc-8.2.0

│ │ │ ├── gdb-8.2

│ │ │ ├── gmp-6.1.2

│ │ │ ├── isl-0.18

│ │ │ ├── libelf-0.8.13

│ │ │ ├── libiconv-1.15

│ │ │ ├── mpc-1.0.3

│ │ │ ├── mpfr-3.1.6

│ │ │ ├── newlib-3.0.0

│ │ │ ├── xz-5.2.3

│ │ │ └── zlib-1.2.8

│ │ ├── patches

│ │ │ ├── binutils-gdb-2.30.patch

│ │ │ ├── binutils-gdb-2.32.patch

│ │ │ ├── python-2.7.13.amd64.patch

│ │ │ └── python-2.7.13.patch

│ │ └── scripts

│ │ ├── VERSION

│ │ ├── build.sh

│ │ ├── container-apps-functions-source.sh

│ │ ├── container-build.sh

│ │ ├── container-libs-functions-source.sh

│ │ ├── defs-source.sh

│ │ ├── git-clone.sh

│ │ ├── helper

│ │ ├── host-defs-source.sh

│ │ └── python-win-config.sh

│ ├── include

│ │ └── gdb

│ │ └── jit-reader.h

│ ├── lib

│ │ ├── bfd-plugins

│ │ │ └── liblto_plugin-0.dll

│ │ └── gcc

│ │ └── riscv-none-embed

│ ├── libexec

│ │ └── gcc

│ │ └── riscv-none-embed

│ ├── riscv-none-embed

│ │ ├── bin

│ │ │ ├── ar.exe

│ │ │ ├── as.exe

│ │ │ ├── ld.bfd.exe

│ │ │ ├── ld.exe

│ │ │ ├── nm.exe

│ │ │ ├── objcopy.exe

│ │ │ ├── objdump.exe

│ │ │ ├── ranlib.exe

│ │ │ ├── readelf.exe

│ │ │ └── strip.exe

│ │ ├── include

│ │ │ ├── _ansi.h

│ │ │ ├── _newlib_version.h

│ │ │ ├── _syslist.h

│ │ │ ├── alloca.h

│ │ │ ├── ar.h

│ │ │ ├── argz.h

│ │ │ ├── assert.h

│ │ │ ├── bits

│ │ │ ├── c

│ │ │ ├── complex.h

│ │ │ ├── cpio.h

│ │ │ ├── ctype.h

│ │ │ ├── devctl.h

│ │ │ ├── dirent.h

│ │ │ ├── elf.h

│ │ │ ├── envlock.h

│ │ │ ├── envz.h

│ │ │ ├── errno.h

│ │ │ ├── fastmath.h

│ │ │ ├── fcntl.h

│ │ │ ├── fenv.h

│ │ │ ├── fnmatch.h

│ │ │ ├── getopt.h

│ │ │ ├── glob.h

│ │ │ ├── grp.h

│ │ │ ├── iconv.h

│ │ │ ├── ieeefp.h

│ │ │ ├── inttypes.h

│ │ │ ├── langinfo.h

│ │ │ ├── libgen.h

│ │ │ ├── limits.h

│ │ │ ├── locale.h

│ │ │ ├── machine

│ │ │ ├── malloc.h

│ │ │ ├── math.h

│ │ │ ├── memory.h

│ │ │ ├── newlib-nano

│ │ │ ├── newlib.h

│ │ │ ├── paths.h

│ │ │ ├── pthread.h

│ │ │ ├── pwd.h

│ │ │ ├── reent.h

│ │ │ ├── regdef.h

│ │ │ ├── regex.h

│ │ │ ├── rpc

│ │ │ ├── sched.h

│ │ │ ├── search.h

│ │ │ ├── setjmp.h

│ │ │ ├── signal.h

│ │ │ ├── spawn.h

│ │ │ ├── ssp

│ │ │ ├── stdatomic.h

│ │ │ ├── stdint.h

│ │ │ ├── stdio.h

│ │ │ ├── stdio_ext.h

│ │ │ ├── stdlib.h

│ │ │ ├── string.h

│ │ │ ├── strings.h

│ │ │ ├── sys

│ │ │ ├── tar.h

│ │ │ ├── termios.h

│ │ │ ├── tgmath.h

│ │ │ ├── threads.h

│ │ │ ├── time.h

│ │ │ ├── unctrl.h

│ │ │ ├── unistd.h

│ │ │ ├── utime.h

│ │ │ ├── utmp.h

│ │ │ ├── wchar.h

│ │ │ ├── wctype.h

│ │ │ ├── wordexp.h

│ │ │ └── xlocale.h

│ │ ├── lib

│ │ │ ├── crt0.o

│ │ │ ├── ldscripts

│ │ │ ├── libc.a

│ │ │ ├── libc_nano.a

│ │ │ ├── libg.a

│ │ │ ├── libg_nano.a

│ │ │ ├── libgloss.a

│ │ │ ├── libm.a

│ │ │ ├── libnosys.a

│ │ │ ├── libsim.a

│ │ │ ├── nano.specs

│ │ │ ├── nosys.specs

│ │ │ ├── rv32e

│ │ │ ├── rv32eac

│ │ │ ├── rv32em

│ │ │ ├── rv32emac

│ │ │ ├── rv32i

│ │ │ ├── rv32iac

│ │ │ ├── rv32im

│ │ │ ├── rv32imac

│ │ │ ├── rv32imaf

│ │ │ ├── rv32imafc

│ │ │ ├── rv32imafdc

│ │ │ ├── rv64imac

│ │ │ ├── rv64imafc

│ │ │ ├── rv64imafdc

│ │ │ └── sim.specs

│ │ └── share

│ │ └── gdb

│ └── share

│ ├── doc

│ │ ├── info

│ │ ├── man

│ │ └── pdf

│ └── gcc-riscv-none-embed

│ └── libstdcxx

└── openocd

├── openocd.exe

├── tinyriscv.cfg

└── tinyriscv_cmsisdap.cfg

200 directories, 1202 files

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论