实例介绍

【实例简介】Vivado调用DDS IP核实现扫频信号

Vivado调用DDS IP核实现扫频信号

一、实验目的

1、熟悉 FPGA 硬件开发平台。

2、学习 DDS IP 核的调用和配置。

3、熟悉 Vivado 的操作流程。

4、掌握 Verilog HDL 的基本语言逻辑。

二、实验仪器

FPGA 数模混合口袋实验平台——EGO1,计算机,示波器,20KΩ电阻和1nF 电容。

三、方案设计基本原理

方案总体设计

扫频信号源是其输出的正弦波信号的频率随时间在一定范围内反复扫描,可以使用数字DDS进行合成,在通过DA模块,将DDS生成的数字信号转换成模拟信号,然后将生成的信号经过一个低通滤波器,可以滤除信号的高频分量用于验证信号的频率是变化的,最后通过示波器可以观测出相应的信号。系统的整体框图如图所示。

DDS基本原理

根据傅立叶变换定理可知,任何周期信号都可以分解为一系列正弦或余弦信号之和,不失一般性,以正弦信号的产生为例详细说明直接数字频率合成技术的原理。比如一个频率为fc的正弦信号,其时域表达式为:

其相位表达式为:

从两式可以看出,正弦信号是关于相位的一个周期函数,下图更加直观的描述相位与幅度的关系,16个相位与16个幅度值相对应,即每一个相位值对应一个幅度值,比如1100对应的相位为3π/2,对应的幅度值为-1。

相位和幅值的一一对应关系就好比存储器中地址和存储内容的关系,如果把一个周期内每个相位对应的幅度值存入存储器当中,那么对于任意频率的正弦信号,在任意时刻,只要已知相位Φ(t),也就知道地址,就可通过查表得到s(t)。图3是DDS的基本结构框图:

相位累加器在每个时钟脉冲输入时,把频率控制字累加一次,相位累加器的输出数据就是信号的相位,用输出的数据作为波形存储器(ROM)的相位取样地址,这样就可以把存取在波形存储器内的波形抽样值经查找表查处,完成相位到幅值的转换。频率控制字相当于 中的 ,相位控制字相当于 中的 。

由于相位累加器字长的限制,相位累加器累加到一定值后,其输出将会溢出,这样波形存储器的地址就会循环一次,即意味着输出波形循环一周。故改变频率控制字即相位增量,就可以改变相位累加器的溢出时间,在时钟频率不变的条件下就可以改变输出频率。改变查表寻址的时钟频率,同样也可以改变输出波形的频率。

为了获得较高的频率分辨率,则只有增加相位累加器的字长N,故一般N都取值较大。但是受存储器容量的限制,存储器地址线的位数W不可能很大,一般都要小于N。这样存储器的地址线一般都只能接在相位累加器输出的高W位,而相位累加器输出余下的(N-W)个低位则只能被舍弃,这就是相位截断误差的来源。

DDS模块的输出频率 是系统工作频率 、相位累加器位数N及频率控制字K满足如下关系

频率分辨率,即频率的变化间隔

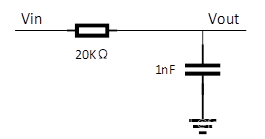

低通滤波器

在本实验中,采用的是一阶RC低通滤波器来进行滤波,电路图如图所示。

根据参数可以计算出3dB带宽截止频率为

四、实验方案

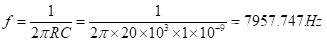

创建工程

按照图5中的芯片选型,创建一个新的工程

图5 芯片选型界面

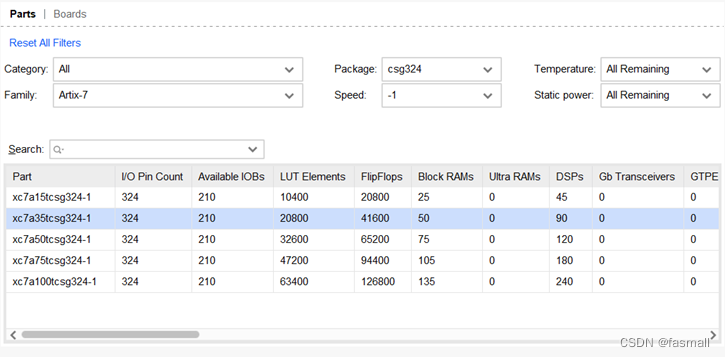

配置DDS IP核

图6 参数1设置界面

在参数1界面主要需要配置输入时钟为100M,与板载时钟保持一致,在这里我们将频率分辨率设置为1,由于我们需要输出一个8位的数据,所以通过公式SFDR=data_Width * 6,可以计算出SFDR为48。

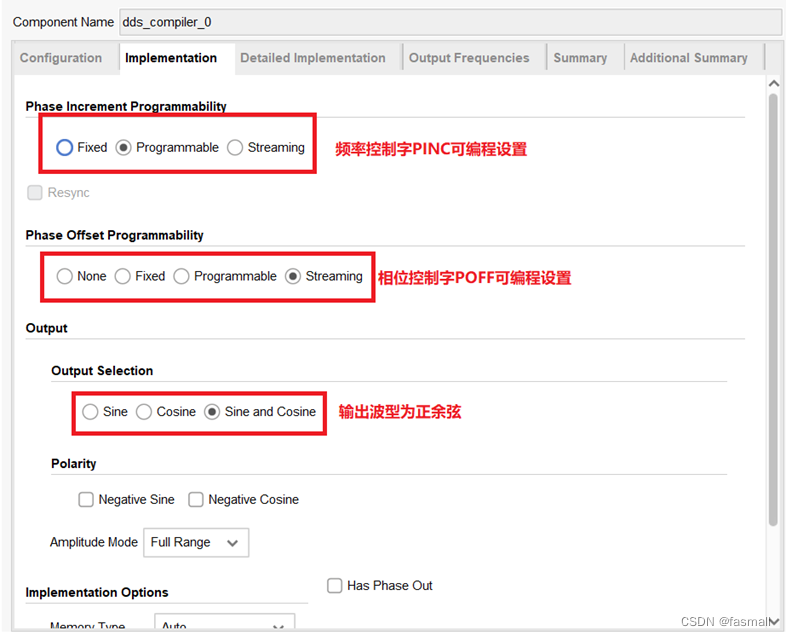

图7 参数2界面

由于在我们本次实验中需要连续输出不同频率的信号,所以在这里我们将频率控制字和相位控制字都设置为可编程模式,输出为正余弦波。其它详细配置如图7所示。

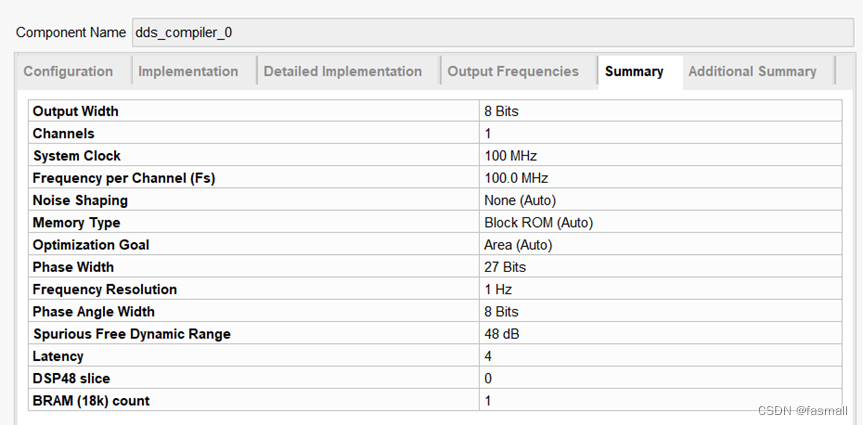

最后我们可以得到一个参数的汇总表如图8所示。

图8 参数总结表

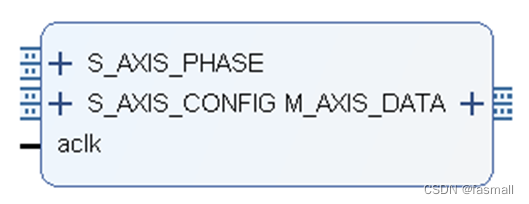

最后DDS集成模块如图9所示。

图9 DDS模块集成

编写各个模块程序

频率控制字改变代码如下,实现原理主要是不断来改变频率控制字的大小,让其在1K和20K之间不断的变化。

always @(posedge clk_1M) begin

if(temp >= F_word_20K) begin

temp <= F_word_1K;

end

else begin

temp <= temp delta;

end

end

最后编写DAC模块,其例化代码如下所示。

dac0832 dac0832_u( .clk (clk_1M ), .rst_n (sys_rst ), .dds_data (dds_data ), .dac_ile (dac_ile ), .dac_cs_n (dac_cs_n ), .dac_wr1_n (dac_wr1_n ), .dac_wr2_n (dac_wr2_n ), .dac_xfer_n (dac_xfer_n), .dac_data (dac_data) );

五、调试与仿真

编写TestBench文件

在本系统中只需要输入时钟和复位信号便可以工作,关键代码如下。

initial begin

sys_clk = 1'b0;//时钟初值

sys_rst = 1'b1;//复位初值

#20 sys_rst = 1'b0;//执行复位

#40 sys_rst = 1'b1;//停止复位

end

always #5 sys_clk = ~sys_clk; //产生100M时钟信号

仿真

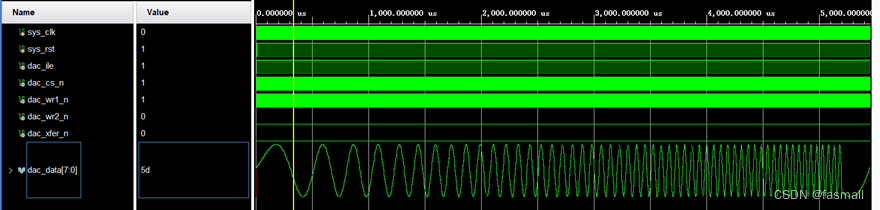

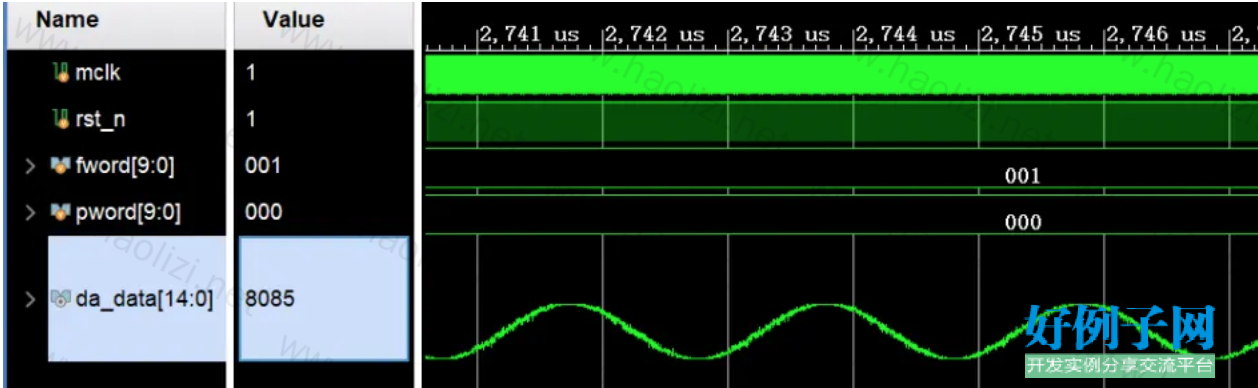

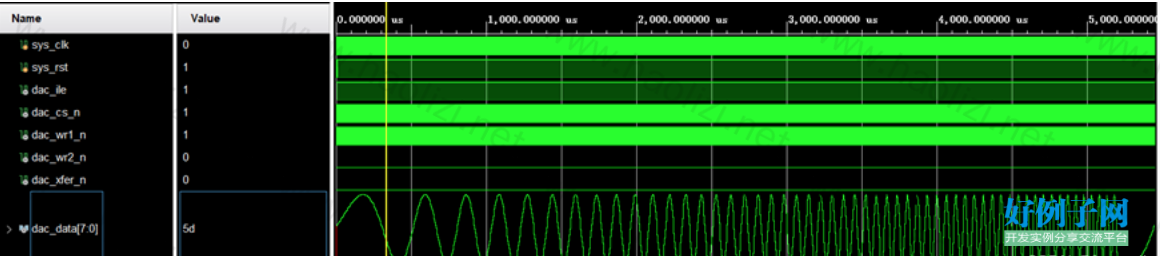

执行Run Simulation,生成仿真结果如下。

图10 仿真结果

通过上面的仿真图可以看出可以生成一个频率连续变化的正弦波,成周期性变化,满足设计要求。

约束输入

在本实验中主要用到复位和时钟以及DAC相关的引脚,所以我们只需配置这些引脚即可,约束配置如下。

set_property -dict {PACKAGE_PIN P17 IOSTANDARD LVCMOS33} [get_ports sys_clk ]

set_property -dict {PACKAGE_PIN P15 IOSTANDARD LVCMOS33} [get_ports sys_rst ]

set_property -dict {PACKAGE_PIN R5 IOSTANDARD LVCMOS33} [get_ports dac_ile]

set_property -dict {PACKAGE_PIN N6 IOSTANDARD LVCMOS33} [get_ports dac_cs_n]

set_property -dict {PACKAGE_PIN V6 IOSTANDARD LVCMOS33} [get_ports dac_wr1_n]

set_property -dict {PACKAGE_PIN R6 IOSTANDARD LVCMOS33} [get_ports dac_wr2_n]

set_property -dict {PACKAGE_PIN V7 IOSTANDARD LVCMOS33} [get_ports dac_xfer_n]

set_property -dict {PACKAGE_PIN T8 IOSTANDARD LVCMOS33} [get_ports {dac_data[0]}]

set_property -dict {PACKAGE_PIN R8 IOSTANDARD LVCMOS33} [get_ports {dac_data[1]}]

set_property -dict {PACKAGE_PIN T6 IOSTANDARD LVCMOS33} [get_ports {dac_data[2]}]

set_property -dict {PACKAGE_PIN R7 IOSTANDARD LVCMOS33} [get_ports {dac_data[3]}]

set_property -dict {PACKAGE_PIN U6 IOSTANDARD LVCMOS33} [get_ports {dac_data[4]}]

set_property -dict {PACKAGE_PIN U7 IOSTANDARD LVCMOS33} [get_ports {dac_data[5]}]

set_property -dict {PACKAGE_PIN V9 IOSTANDARD LVCMOS33} [get_ports {dac_data[6]}]

set_property -dict {PACKAGE_PIN U9 IOSTANDARD LVCMOS33} [get_ports {dac_data[7]}]

连接硬件电路

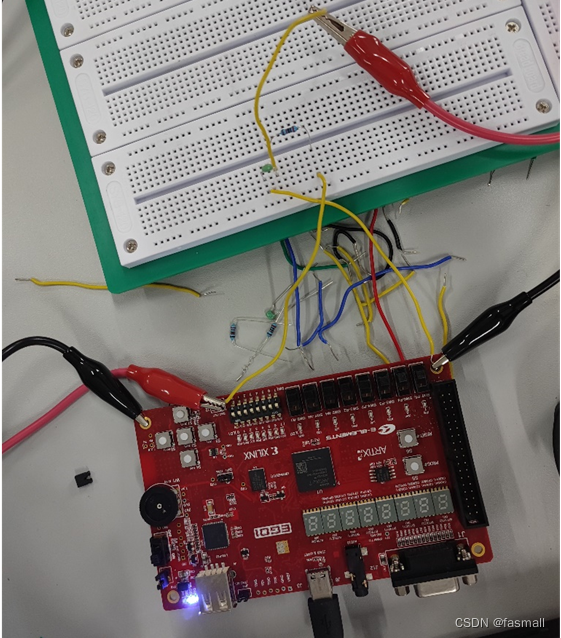

连接硬件电路如图11所示

图11 硬件连接图

生成和下载比特流

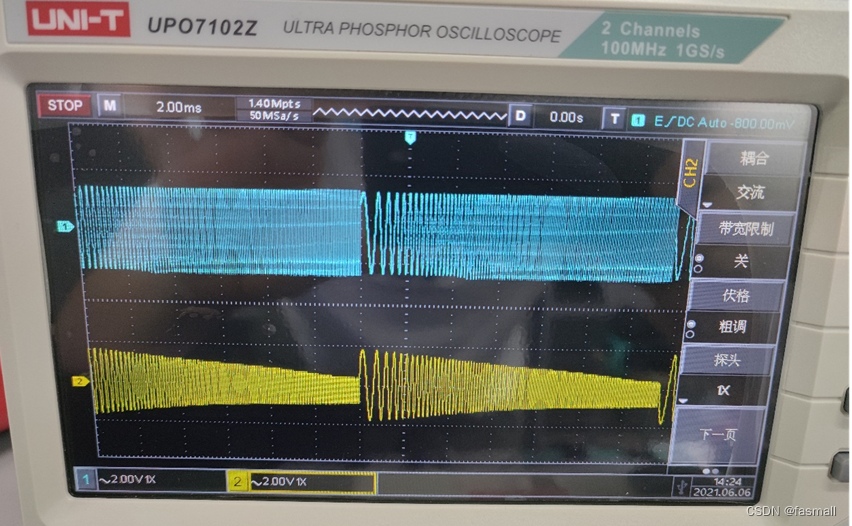

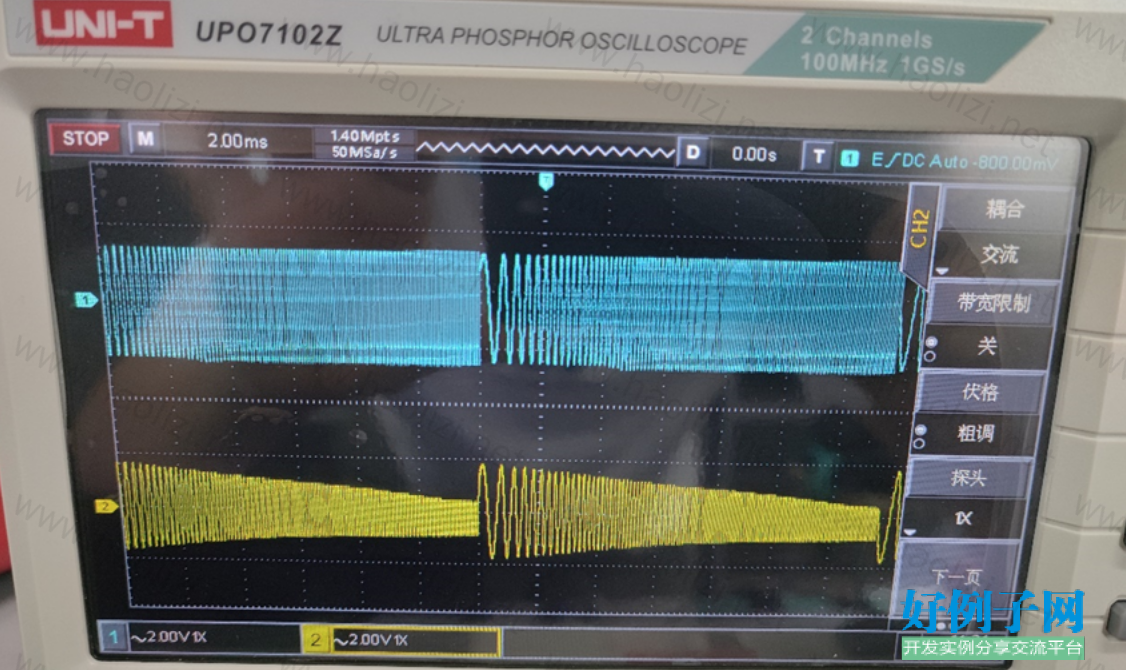

运行程序,生成比特流,将开发板与电脑相连,下载程序。通过低通滤波器进行输出处理,我们可以得到两个不同信号,如图12所示。

图12 滤波前后波形输出

通过示波器可以看出,原始信号与仿真波形一致,信号在通过低通滤波器之后,高频部分分量被滤除了,符合设计要求。

【实例截图】

.

├── Vivado调用DDS IP核实现扫频信号.rar

└── dds_dac

├── dds_dac.cache

│ ├── compile_simlib

│ │ ├── activehdl

│ │ ├── ies

│ │ ├── modelsim

│ │ ├── questa

│ │ ├── riviera

│ │ ├── vcs

│ │ └── xcelium

│ ├── ip

│ │ └── 2019.2

│ │ ├── 8bec32f749bba73b

│ │ │ ├── 8bec32f749bba73b.xci

│ │ │ ├── dds_compiler_0.dcp

│ │ │ ├── dds_compiler_0_sim_netlist.v

│ │ │ ├── dds_compiler_0_sim_netlist.vhdl

│ │ │ ├── dds_compiler_0_stub.v

│ │ │ └── dds_compiler_0_stub.vhdl

│ │ └── 95d271f88d125171

│ │ ├── 95d271f88d125171.xci

│ │ ├── dds_compiler_0.dcp

│ │ ├── dds_compiler_0_sim_netlist.v

│ │ ├── dds_compiler_0_sim_netlist.vhdl

│ │ ├── dds_compiler_0_stub.v

│ │ └── dds_compiler_0_stub.vhdl

│ └── wt

│ ├── gui_handlers.wdf

│ ├── java_command_handlers.wdf

│ ├── project.wpc

│ ├── synthesis.wdf

│ ├── synthesis_details.wdf

│ ├── webtalk_pa.xml

│ └── xsim.wdf

├── dds_dac.hw

│ ├── dds_dac.lpr

│ └── hw_1

│ ├── hw.xml

│ └── wave

├── dds_dac.ip_user_files

│ ├── README.txt

│ ├── ip

│ │ └── dds_compiler_0

│ │ ├── dds_compiler_0.veo

│ │ ├── dds_compiler_0.vho

│ │ ├── dds_compiler_0_stub.v

│ │ └── dds_compiler_0_stub.vhdl

│ ├── ipstatic

│ │ └── hdl

│ │ ├── axi_utils_v2_0_vh_rfs.vhd

│ │ ├── dds_compiler_v6_0_vh_rfs.vhd

│ │ ├── mult_gen_v12_0_vh_rfs.vhd

│ │ ├── xbip_bram18k_v3_0_vh_rfs.vhd

│ │ ├── xbip_dsp48_addsub_v3_0_vh_rfs.vhd

│ │ ├── xbip_dsp48_multadd_v3_0_vh_rfs.vhd

│ │ ├── xbip_dsp48_wrapper_v3_0_vh_rfs.vhd

│ │ ├── xbip_pipe_v3_0_vh_rfs.vhd

│ │ └── xbip_utils_v3_0_vh_rfs.vhd

│ └── sim_scripts

│ └── dds_compiler_0

│ ├── README.txt

│ ├── activehdl

│ │ ├── README.txt

│ │ ├── compile.do

│ │ ├── dds_compiler_0.sh

│ │ ├── dds_compiler_0.udo

│ │ ├── file_info.txt

│ │ ├── simulate.do

│ │ └── wave.do

│ ├── ies

│ │ ├── README.txt

│ │ ├── dds_compiler_0.sh

│ │ ├── file_info.txt

│ │ └── run.f

│ ├── modelsim

│ │ ├── README.txt

│ │ ├── compile.do

│ │ ├── dds_compiler_0.sh

│ │ ├── dds_compiler_0.udo

│ │ ├── file_info.txt

│ │ ├── simulate.do

│ │ └── wave.do

│ ├── questa

│ │ ├── README.txt

│ │ ├── compile.do

│ │ ├── dds_compiler_0.sh

│ │ ├── dds_compiler_0.udo

│ │ ├── elaborate.do

│ │ ├── file_info.txt

│ │ ├── simulate.do

│ │ └── wave.do

│ ├── riviera

│ │ ├── README.txt

│ │ ├── compile.do

│ │ ├── dds_compiler_0.sh

│ │ ├── dds_compiler_0.udo

│ │ ├── file_info.txt

│ │ ├── simulate.do

│ │ └── wave.do

│ ├── vcs

│ │ ├── README.txt

│ │ ├── dds_compiler_0.sh

│ │ ├── file_info.txt

│ │ └── simulate.do

│ ├── xcelium

│ │ ├── README.txt

│ │ ├── dds_compiler_0.sh

│ │ ├── file_info.txt

│ │ └── run.f

│ └── xsim

│ ├── README.txt

│ ├── cmd.tcl

│ ├── dds_compiler_0.sh

│ ├── elab.opt

│ ├── file_info.txt

│ ├── vhdl.prj

│ └── xsim.ini

├── dds_dac.runs

│ ├── dds_compiler_0_synth_1

│ │ ├── ISEWrap.js

│ │ ├── ISEWrap.sh

│ │ ├── __synthesis_is_complete__

│ │ ├── dds_compiler_0.dcp

│ │ ├── dds_compiler_0.tcl

│ │ ├── dds_compiler_0.vds

│ │ ├── dds_compiler_0_utilization_synth.pb

│ │ ├── dds_compiler_0_utilization_synth.rpt

│ │ ├── dont_touch.xdc

│ │ ├── gen_run.xml

│ │ ├── htr.txt

│ │ ├── project.wdf

│ │ ├── rundef.js

│ │ ├── runme.bat

│ │ ├── runme.log

│ │ ├── runme.sh

│ │ ├── vivado.jou

│ │ └── vivado.pb

│ └── synth_1

│ ├── ISEWrap.js

│ ├── ISEWrap.sh

│ ├── __synthesis_is_complete__

│ ├── dds_dac_top.dcp

│ ├── dds_dac_top.tcl

│ ├── dds_dac_top.vds

│ ├── dds_dac_top_utilization_synth.pb

│ ├── dds_dac_top_utilization_synth.rpt

│ ├── gen_run.xml

│ ├── htr.txt

│ ├── project.wdf

│ ├── rundef.js

│ ├── runme.bat

│ ├── runme.log

│ ├── runme.sh

│ ├── vivado.jou

│ └── vivado.pb

├── dds_dac.sim

│ └── sim_1

│ └── behav

│ └── xsim

│ ├── compile.bat

│ ├── compile.log

│ ├── elaborate.bat

│ ├── elaborate.log

│ ├── glbl.v

│ ├── simulate.bat

│ ├── simulate.log

│ ├── tb_dds_adc.tcl

│ ├── tb_dds_adc_behav.wdb

│ ├── tb_dds_adc_vhdl.prj

│ ├── tb_dds_adc_vlog.prj

│ ├── webtalk.jou

│ ├── webtalk.log

│ ├── webtalk_12168.backup.jou

│ ├── webtalk_12168.backup.log

│ ├── webtalk_14104.backup.jou

│ ├── webtalk_14104.backup.log

│ ├── webtalk_14404.backup.jou

│ ├── webtalk_14404.backup.log

│ ├── webtalk_4644.backup.jou

│ ├── webtalk_4644.backup.log

│ ├── webtalk_7612.backup.jou

│ ├── webtalk_7612.backup.log

│ ├── xelab.pb

│ ├── xsim.dir

│ │ ├── tb_dds_adc_behav

│ │ │ ├── Compile_Options.txt

│ │ │ ├── TempBreakPointFile.txt

│ │ │ ├── obj

│ │ │ │ ├── xsim_0.win64.obj

│ │ │ │ ├── xsim_1.c

│ │ │ │ └── xsim_1.win64.obj

│ │ │ ├── webtalk

│ │ │ │ ├── usage_statistics_ext_xsim.html

│ │ │ │ └── usage_statistics_ext_xsim.xml

│ │ │ ├── xsim.dbg

│ │ │ ├── xsim.mem

│ │ │ ├── xsim.reloc

│ │ │ ├── xsim.rlx

│ │ │ ├── xsim.rtti

│ │ │ ├── xsim.svtype

│ │ │ ├── xsim.type

│ │ │ ├── xsim.xdbg

│ │ │ ├── xsimSettings.ini

│ │ │ ├── xsimcrash.log

│ │ │ ├── xsimk.exe

│ │ │ └── xsimkernel.log

│ │ └── xil_defaultlib

│ │ ├── clk_1@m.sdb

│ │ ├── dac0832.sdb

│ │ ├── dds_compiler_0.vdb

│ │ ├── dds_dac_top.sdb

│ │ ├── glbl.sdb

│ │ ├── tb_dds_adc.sdb

│ │ └── xil_defaultlib.rlx

│ ├── xsim.ini

│ ├── xsim.ini.bak

│ ├── xvhdl.log

│ ├── xvhdl.pb

│ ├── xvlog.log

│ └── xvlog.pb

├── dds_dac.srcs

│ ├── constrs_1

│ │ └── new

│ │ └── dds_dac.xdc

│ ├── sim_1

│ │ └── new

│ │ └── tb_dds_adc.v

│ └── sources_1

│ ├── ip

│ │ └── dds_compiler_0

│ │ ├── cmodel

│ │ │ ├── dds_compiler_v6_0_bitacc_cmodel_lin64.zip

│ │ │ └── dds_compiler_v6_0_bitacc_cmodel_nt64.zip

│ │ ├── dds_compiler_0.dcp

│ │ ├── dds_compiler_0.veo

│ │ ├── dds_compiler_0.vho

│ │ ├── dds_compiler_0.xci

│ │ ├── dds_compiler_0.xml

│ │ ├── dds_compiler_0_ooc.xdc

│ │ ├── dds_compiler_0_sim_netlist.v

│ │ ├── dds_compiler_0_sim_netlist.vhdl

│ │ ├── dds_compiler_0_stub.v

│ │ ├── dds_compiler_0_stub.vhdl

│ │ ├── demo_tb

│ │ │ └── tb_dds_compiler_0.vhd

│ │ ├── doc

│ │ │ └── dds_compiler_v6_0_changelog.txt

│ │ ├── hdl

│ │ │ ├── axi_utils_v2_0_vh_rfs.vhd

│ │ │ ├── dds_compiler_v6_0_vh_rfs.vhd

│ │ │ ├── mult_gen_v12_0_vh_rfs.vhd

│ │ │ ├── xbip_bram18k_v3_0_vh_rfs.vhd

│ │ │ ├── xbip_dsp48_addsub_v3_0_vh_rfs.vhd

│ │ │ ├── xbip_dsp48_multadd_v3_0_vh_rfs.vhd

│ │ │ ├── xbip_dsp48_wrapper_v3_0_vh_rfs.vhd

│ │ │ ├── xbip_pipe_v3_0_vh_rfs.vhd

│ │ │ └── xbip_utils_v3_0_vh_rfs.vhd

│ │ ├── sim

│ │ │ └── dds_compiler_0.vhd

│ │ └── synth

│ │ └── dds_compiler_0.vhd

│ └── new

│ ├── clk_1M.v

│ ├── dac0832.v

│ └── dds_dac_top.v

├── dds_dac.xpr

└── tb_dds_adc_behav.wcfg

60 directories, 208 files

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论