实例介绍

【实例截图】

【核心代码】

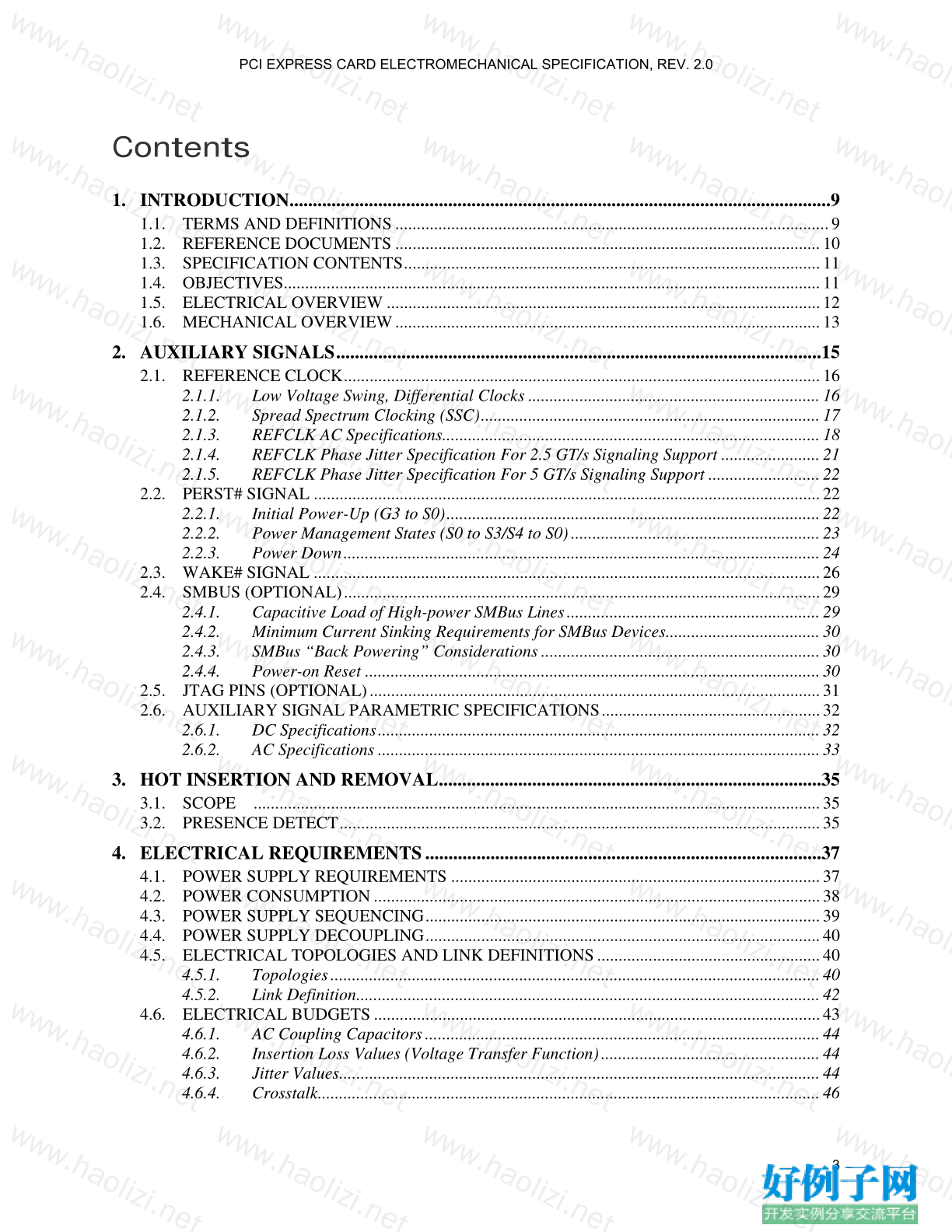

Contents

1. INTRODUCTION....................................................................................................................9

1.1. TERMS AND DEFINITIONS.....................................................................................................9

1.2. REFERENCE DOCUMENTS ...................................................................................................10

1.3. SPECIFICATION CONTENTS.................................................................................................11

1.4. OBJECTIVES.............................................................................................................................11

1.5. ELECTRICAL OVERVIEW .....................................................................................................12

1.6. MECHANICAL OVERVIEW...................................................................................................13

2. AUXILIARY SIGNALS........................................................................................................15

2.1. REFERENCE CLOCK...............................................................................................................16

2.1.1. Low Voltage Swing, Differential Clocks ....................................................................16

2.1.2. Spread Spectrum Clocking (SSC)...............................................................................17

2.1.3. REFCLK AC Specifications........................................................................................18

2.1.4. REFCLK Phase Jitter Specification For 2.5 GT/s Signaling Support .......................21

2.1.5. REFCLK Phase Jitter Specification For 5 GT/s Signaling Support ..........................22

2.2. PERST# SIGNAL ......................................................................................................................22

2.2.1. Initial Power-Up (G3 to S0).......................................................................................22

2.2.2. Power Management States (S0 to S3/S4 to S0)..........................................................23

2.2.3. Power Down...............................................................................................................24

2.3. WAKE# SIGNAL ......................................................................................................................26

2.4. SMBUS (OPTIONAL)...............................................................................................................29

2.4.1. Capacitive Load of High-power SMBus Lines...........................................................29

2.4.2. Minimum Current Sinking Requirements for SMBus Devices....................................30

2.4.3. SMBus “Back Powering” Considerations.................................................................30

2.4.4. Power-on Reset ..........................................................................................................30

2.5. JTAG PINS (OPTIONAL).........................................................................................................31

2.6. AUXILIARY SIGNAL PARAMETRIC SPECIFICATIONS...................................................32

2.6.1. DC Specifications.......................................................................................................32

2.6.2. AC Specifications .......................................................................................................33

3. HOT INSERTION AND REMOVAL..................................................................................35

3.1. SCOPE ....................................................................................................................................35

3.2. PRESENCE DETECT................................................................................................................35

4. ELECTRICAL REQUIREMENTS.....................................................................................37

4.1. POWER SUPPLY REQUIREMENTS ......................................................................................37

4.2. POWER CONSUMPTION........................................................................................................38

4.3. POWER SUPPLY SEQUENCING............................................................................................39

4.4. POWER SUPPLY DECOUPLING............................................................................................40

4.5. ELECTRICAL TOPOLOGIES AND LINK DEFINITIONS....................................................40

4.5.1. Topologies..................................................................................................................40

4.5.2. Link Definition............................................................................................................42

4.6. ELECTRICAL BUDGETS........................................................................................................43

4.6.1. AC Coupling Capacitors............................................................................................44

4.6.2. Insertion Loss Values (Voltage Transfer Function)...................................................44

4.6.3. Jitter Values................................................................................................................44

4.6.4. Crosstalk.....................................................................................................................46

PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV. 2.0

4

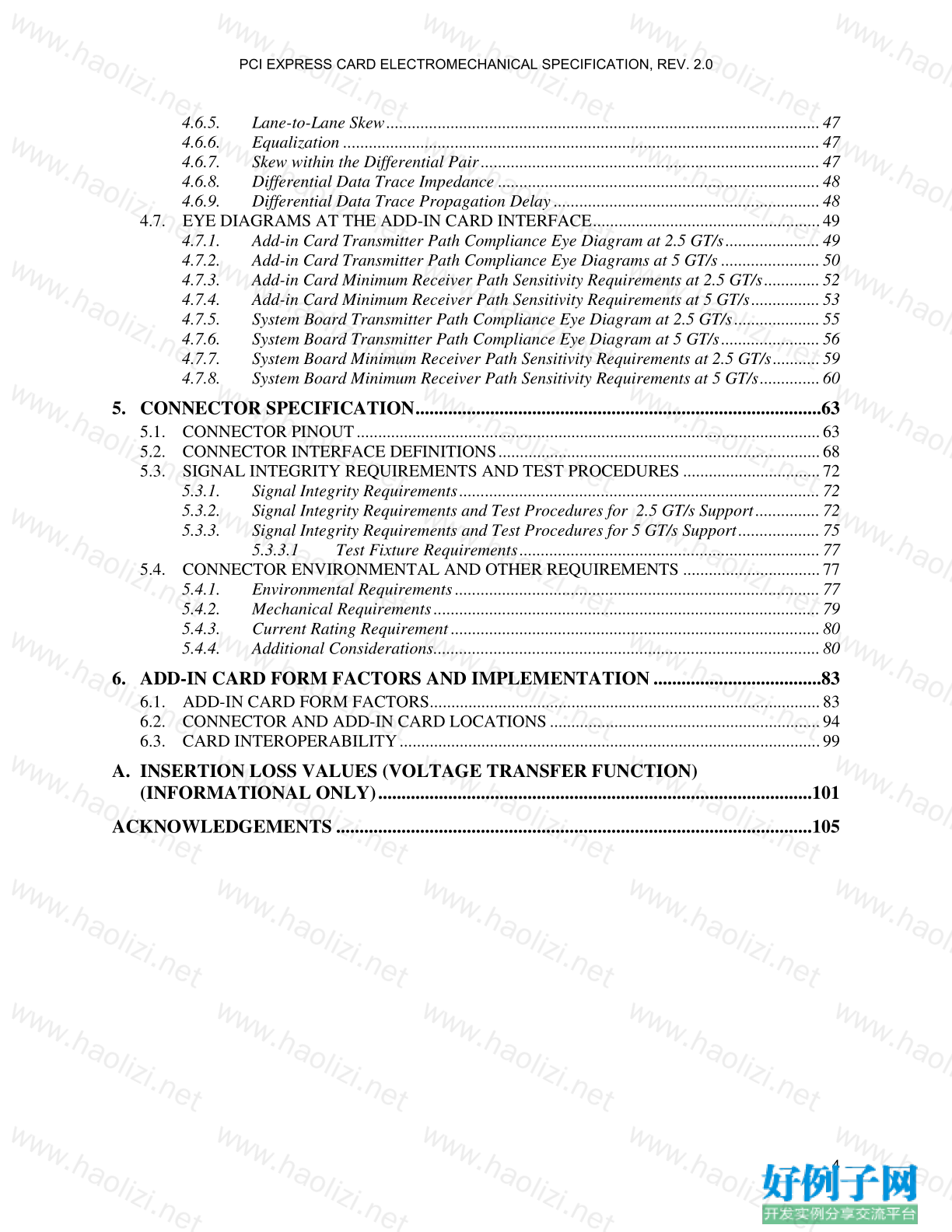

4.6.5. Lane-to-Lane Skew.....................................................................................................47

4.6.6. Equalization ...............................................................................................................47

4.6.7. Skew within the Differential Pair...............................................................................47

4.6.8. Differential Data Trace Impedance ...........................................................................48

4.6.9. Differential Data Trace Propagation Delay ..............................................................48

4.7. EYE DIAGRAMS AT THE ADD-IN CARD INTERFACE.....................................................49

4.7.1. Add-in Card Transmitter Path Compliance Eye Diagram at 2.5 GT/s......................49

4.7.2. Add-in Card Transmitter Path Compliance Eye Diagrams at 5 GT/s .......................50

4.7.3. Add-in Card Minimum Receiver Path Sensitivity Requirements at 2.5 GT/s.............52

4.7.4. Add-in Card Minimum Receiver Path Sensitivity Requirements at 5 GT/s................53

4.7.5. System Board Transmitter Path Compliance Eye Diagram at 2.5 GT/s....................55

4.7.6. System Board Transmitter Path Compliance Eye Diagram at 5 GT/s.......................56

4.7.7. System Board Minimum Receiver Path Sensitivity Requirements at 2.5 GT/s...........59

4.7.8. System Board Minimum Receiver Path Sensitivity Requirements at 5 GT/s..............60

5. CONNECTOR SPECIFICATION.......................................................................................63

5.1. CONNECTOR PINOUT............................................................................................................63

5.2. CONNECTOR INTERFACE DEFINITIONS...........................................................................68

5.3. SIGNAL INTEGRITY REQUIREMENTS AND TEST PROCEDURES ................................72

5.3.1. Signal Integrity Requirements....................................................................................72

5.3.2. Signal Integrity Requirements and Test Procedures for 2.5 GT/s Support...............72

5.3.3. Signal Integrity Requirements and Test Procedures for 5 GT/s Support...................75

5.3.3.1 Test Fixture Requirements......................................................................77

5.4. CONNECTOR ENVIRONMENTAL AND OTHER REQUIREMENTS ................................77

5.4.1. Environmental Requirements.....................................................................................77

5.4.2. Mechanical Requirements..........................................................................................79

5.4.3. Current Rating Requirement......................................................................................80

5.4.4. Additional Considerations..........................................................................................80

6. ADD-IN CARD FORM FACTORS AND IMPLEMENTATION....................................83

6.1. ADD-IN CARD FORM FACTORS...........................................................................................83

6.2. CONNECTOR AND ADD-IN CARD LOCATIONS...............................................................94

6.3. CARD INTEROPERABILITY..................................................................................................99

A. INSERTION LOSS VALUES (VOLTAGE TRANSFER FUNCTION)

(INFORMATIONAL ONLY).............................................................................................101

ACKNOWLEDGEMENTS ......................................................................................................105

PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV. 2.0

5

Figures

FIGURE 1-1: VERTICAL EDGE-CARD CONNECTOR.................................................................13

FIGURE 1-2: EXAMPLE SERVER I/O BOARD WITH PCI EXPRESS SLOTS ON A RISER.....13

FIGURE 2-1: DIFFERENTIAL REFCLK WAVEFORM .................................................................16

FIGURE 2-2: EXAMPLE CURRENT MODE REFERENCE CLOCK SOURCE TERMINATION17

FIGURE 2-3: SINGLE-ENDED MEASUREMENT POINTS FOR ABSOLUTE CROSS POINT

AND SWING .............................................................................................................................19

FIGURE 2-4: SINGLE-ENDED MEASUREMENT POINTS FOR DELTA CROSS POINT..........19

FIGURE 2-5: SINGLE-ENDED MEASUREMENT POINTS FOR RISE AND FALL TIME

MATCHING...............................................................................................................................20

FIGURE 2-6: DIFFERENTIAL MEASUREMENT POINTS FOR DUTY CYCLE AND PERIOD 20

FIGURE 2-7: DIFFERENTIAL MEASUREMENT POINTS FOR RISE AND FALL TIME..........20

FIGURE 2-8: DIFFERENTIAL MEASUREMENT POINTS FOR RINGBACK.............................20

FIGURE 2-9: REFERENCE CLOCK SYSTEM MEASUREMENT POINT AND LOADING.......21

FIGURE 2-10: POWER UP................................................................................................................23

FIGURE 2-11: POWER MANAGEMENT STATES.........................................................................24

FIGURE 2-12: OUT-OF-TOLERANCE THRESHOLD WINDOWS...............................................25

FIGURE 2-13: POWER DOWN.........................................................................................................25

FIGURE 2-14: WAKE# RISE AND FALL TIME MEASUREMENT POINTS...............................33

FIGURE 3-1: PRESENCE DETECT IN A HOT-PLUG ENVIRONMENT......................................36

FIGURE 4-1: PCI EXPRESS ON THE SYSTEM BOARD...............................................................41

FIGURE 4-2: PCI EXPRESS CONNECTOR ON SYSTEM BOARD WITH AN ADD-IN CARD.41

FIGURE 4-3: PCI EXPRESS CONNECTOR ON A RISER CARD WITH AN ADD-IN CARD....42

FIGURE 4-4: LINK DEFINITION FOR TWO COMPONENTS......................................................43

FIGURE 4-5: JITTER BUDGET........................................................................................................44

FIGURE 4-6: ADD-IN CARD TRANSMITTER PATH COMPLIANCE EYE DIAGRAM............50

FIGURE 4-7: ADD-IN CARD TRANSMITTER PATH COMPLIANCE EYE DIAGRAM............52

FIGURE 4-8: REPRESENTATIVE COMPOSITE EYE DIAGRAM FOR ADD-IN CARD

RECEIVER PATH COMPLIANCE..........................................................................................53

FIGURE 4-9: REPRESENTATIVE COMPOSITE EYE DIAGRAM FOR ADD-IN CARD

RECEIVER PATH COMPLIANCE..........................................................................................54

FIGURE 4-10: SYSTEM BOARD TRANSMITTER PATH COMPOSITE COMPLIANCE EYE

DIAGRAM.................................................................................................................................55

FIGURE 4-11: TWO PORT MEASUREMENT FUNCTIONAL BLOCK DIAGRAM....................56

FIGURE 4-12: SYSTEM BOARD TRANSMITTER PATH COMPOSITE COMPLIANCE EYE

DIAGRAM.................................................................................................................................58

FIGURE 4-13: REPRESENTATIVE COMPOSITE EYE DIAGRAM FOR SYSTEM BOARD

RECEIVER PATH COMPLIANCE..........................................................................................61

FIGURE 5-1: CONNECTOR FORM FACTOR.................................................................................68

FIGURE 5-2: RECOMMENDED FOOTPRINT................................................................................69

FIGURE 5-3: ADD-IN CARD EDGE-FINGER DIMENSIONS.......................................................70

FIGURE 5-4: ILLUSTRATION OF ADJACENT PAIRS .................................................................75

FIGURE 5-5: CONTACT RESISTANCE MEASUREMENT POINTS............................................78

FIGURE 6-1: STANDARD HEIGHT PCI EXPRESS ADD-IN CARD WITHOUT THE I/O

BRACKET .................................................................................................................................84

FIGURE 6-2: STANDARD HEIGHT PCI EXPRESS ADD-IN CARD WITH THE I/O BRACKET

AND CARD RETAINER...........................................................................................................85

FIGURE 6-3: ADDITIONAL FEATURE AND KEEPOUTS ON THE X16 GRAPHICS CARD...86

FIGURE 6-4: STANDARD ADD-IN CARD I/O BRACKET...........................................................87

PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV. 2.0

6

FIGURE 6-5: BRACKET DESIGN WITH THE MOUNTING TABS MOUNTED ON THE

PRIMARY SIDE OF THE ADD-IN CARD..............................................................................88

FIGURE 6-6: ADD-IN CARD RETAINER.......................................................................................89

FIGURE 6-7: LOW PROFILE PCI EXPRESS ADD-IN CARD WITHOUT THE I/O BRACKET.90

FIGURE 6-8: LOW PROFILE PCI EXPRESS ADD-IN CARD WITH THE I/O BRACKET .........91

FIGURE 6-9: LOW PROFILE I/O BRACKET..................................................................................92

FIGURE 6-10: FULL HEIGHT I/O BRACKET FOR LOW PROFILE CARDS..............................93

FIGURE 6-11: EXAMPLE OF A PC SYSTEM IN MICROATX FORM FACTOR........................94

FIGURE 6-12: INTRODUCTION OF A PCI EXPRESS CONNECTOR IN A MICROATX

SYSTEM....................................................................................................................................95

FIGURE 6-13: MORE PCI EXPRESS CONNECTORS ARE INTRODUCED ON A MICROATX

SYSTEM BOARD .....................................................................................................................96

FIGURE 6-14: PCI EXPRESS CONNECTOR LOCATION IN A MICROATX SYSTEM WITH

ONE PCI EXPRESS CONNECTOR.........................................................................................97

FIGURE 6-15: PCI EXPRESS CONNECTOR LOCATION IN A MICROATX SYSTEM WITH

TWO PCI EXPRESS CONNECTORS......................................................................................98

FIGURE 6-16: CARD ASSEMBLED IN CONNECTOR..................................................................99

FIGURE A-1: EXAMPLE INTERCONNECT TERMINATED AT THE CONNECTOR

INTERFACE............................................................................................................................101

FIGURE A-2: INSERTION LOSS BUDGETS................................................................................102

PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV. 2.0

7

Tables

TABLE 2-1: REFCLK DC SPECIFICATIONS AND AC TIMING REQUIREMENTS..................18

TABLE 2-2: MAXIMUM ALLOWED PHASE JITTER WHEN APPLIED TO FIXED FILTER

CHARACTERISTIC..................................................................................................................22

TABLE 2-3: AUXILIARY SIGNAL DC SPECIFICATIONS - PERST#, WAKE#, AND SMBUS 32

TABLE 2-4: POWER SEQUENCING AND RESET SIGNAL TIMINGS.......................................33

TABLE 4-1: POWER SUPPLY RAIL REQUIREMENTS................................................................37

TABLE 4-2: ADD-IN CARD POWER DISSIPATION.....................................................................38

TABLE 4-3: TOTAL SYSTEM JITTER BUDGET FOR 2.5 GT/S SIGNALING............................45

TABLE 4-4: ALLOCATION OF INTERCONNECT JITTER BUDGET FOR 2.5 GT/S

SIGNALING ..............................................................................................................................45

TABLE 4-5: TOTAL SYSTEM JITTER BUDGET FOR 5 GT/S SIGNALING...............................46

TABLE 4-6: ALLOWABLE INTERCONNECT LANE-TO-LANE SKEW.....................................47

TABLE 4-7: ADD-IN CARD TRANSMITTER PATH COMPLIANCE EYE REQUIREMENTS AT

2.5 GT/S .....................................................................................................................................49

TABLE 4-8: ADD-IN CARD TRANSMITTER PATH COMPLIANCE EYE REQUIREMENTS AT

5 GT/S AND 3.5 DB DE-EMPHASIS.......................................................................................50

TABLE 4-9: ADD-IN CARD JITTER REQUIREMENTS FOR 5 GT/S SIGNALING AT 3.5 DB

DE-EMPHASIS..........................................................................................................................51

TABLE 4-10: ADD-IN CARD TRANSMITTER PATH COMPLIANCE EYE REQUIREMENTS

AT 5 GT/S AT 6.0 DB DE-EMPHASIS....................................................................................51

TABLE 4-11: ADD-IN CARD JITTER REQUIREMENTS FOR 5 GT/S SIGNALING AT 6.0 DB

DE-EMPHASIS..........................................................................................................................52

TABLE 4-12: ADD-IN CARD MINIMUM RECEIVER PATH SENSITIVITY REQUIREMENTS

AT 2.5 GT/S...............................................................................................................................52

TABLE 4-13: ADD-IN CARD MINIMUM RECEIVER PATH SENSITIVITY REQUIREMENTS

AT 5 GT/S..................................................................................................................................53

TABLE 4-14: SYSTEM BOARD TRANSMITTER PATH COMPLIANCE EYE REQUIREMENTS

AT 2.5 GT/S...............................................................................................................................55

TABLE 4-15: SYSTEM BOARD TRANSMITTER PATH COMPLIANCE EYE REQUIREMENTS

AT 5 GT/S..................................................................................................................................58

TABLE 4-16: SYSTEM BOARD JITTER REQUIREMENTS FOR 5 GT/S SIGNALING .............59

TABLE 4-17: SYSTEM BOARD MINIMUM RECEIVER PATH SENSITIVITY

REQUIREMENTS AT 2.5 GT/S...............................................................................................59

TABLE 4-18: SYSTEM BOARD MINIMUM RECEIVER PATH SENSITIVITY

REQUIREMENTS AT 5 GT/S FOR A LINK THAT OPERATES WITH 3.5 DB DE-

EMPHASIS................................................................................................................................60

TABLE 4-19: SYSTEM BOARD MINIMUM RECEIVER PATH SENSITIVITY

REQUIREMENTS AT 5 GT/S FOR A LINK THAT OPERATES WITH 6.0 DB DE-

EMPHASIS................................................................................................................................60

TABLE 5-1: PCI EXPRESS CONNECTORS PINOUT....................................................................63

TABLE 5-2: SIGNAL INTEGRITY REQUIREMENTS AND TEST PROCEDURES FOR 2.5 GT/S

SUPPORT ..................................................................................................................................73

TABLE 5-3: SIGNAL INTEGRITY REQUIREMENTS AND TEST PROCEDURES FOR 5 GT/S

SUPPORT ..................................................................................................................................76

TABLE 5-4: TEST DURATIONS......................................................................................................78

TABLE 5-5: MECHANICAL TEST PROCEDURES AND REQUIREMENTS..............................79

TABLE 5-6: END OF LIFE CURRENT RATING TEST SEQUENCE............................................80

PCI EXPRESS CARD ELECTROMECHANICAL SPECIFICATION, REV. 2.0

8

TABLE 5-7: ADDITIONAL REQUIREMENTS...............................................................................80

TABLE 6-1: ADD-IN CARD SIZES..................................................................................................83

TABLE 6-2: CARD INTEROPERABILITY......................................................................................99

TABLE A-1: ALLOCATION OF INTERCONNECT PATH INSERTION LOSS BUDGET FOR 2.5

GT/S SIGNALING...................................................................................................................102

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论