实例介绍

【实例简介】H8S-2472_ H8S-2463_ H8S-2462 Haredware Manual

芯片手册

【实例截图】

【核心代码】

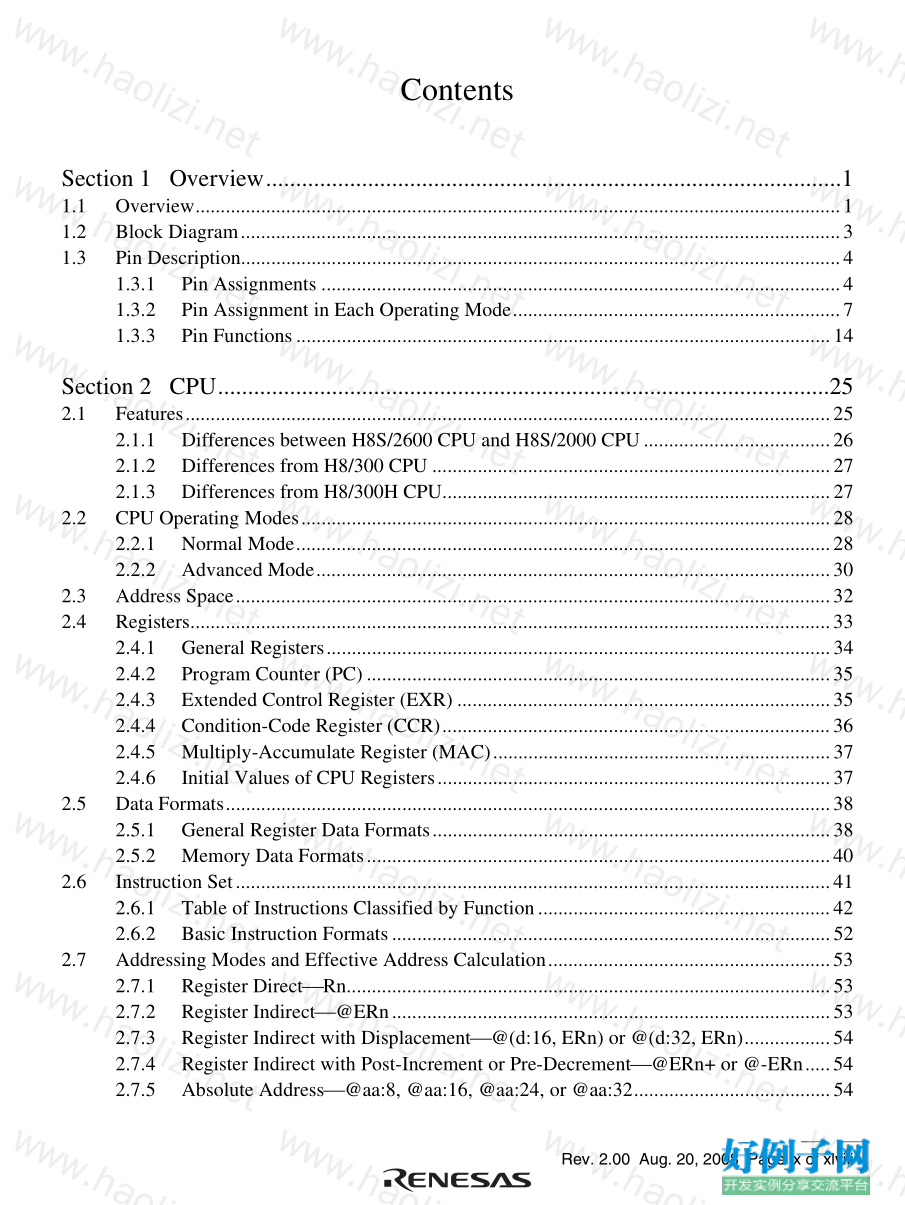

Contents

Section 1 Overview................................................................................................1

1.1 Overview................................................................................................................................1

1.2 Block Diagram.......................................................................................................................3

1.3 Pin Description.......................................................................................................................4

1.3.1 Pin Assignments .......................................................................................................4

1.3.2 Pin Assignment in Each Operating Mode.................................................................7

1.3.3 Pin Functions..........................................................................................................14

Section 2 CPU......................................................................................................25

2.1 Features................................................................................................................................25

2.1.1 Differences between H8S/2600 CPU and H8S/2000 CPU.....................................26

2.1.2 Differences from H8/300 CPU ...............................................................................27

2.1.3 Differences from H8/300H CPU.............................................................................27

2.2 CPU Operating Modes.........................................................................................................28

2.2.1 Normal Mode..........................................................................................................28

2.2.2 Advanced Mode......................................................................................................30

2.3 Address Space......................................................................................................................32

2.4 Registers...............................................................................................................................33

2.4.1 General Registers....................................................................................................34

2.4.2 Program Counter (PC)............................................................................................35

2.4.3 Extended Control Register (EXR) ..........................................................................35

2.4.4 Condition-Code Register (CCR).............................................................................36

2.4.5 Multiply-Accumulate Register (MAC)...................................................................37

2.4.6 Initial Values of CPU Registers..............................................................................37

2.5 Data Formats........................................................................................................................38

2.5.1 General Register Data Formats...............................................................................38

2.5.2 Memory Data Formats............................................................................................40

2.6 Instruction Set......................................................................................................................41

2.6.1 Table of Instructions Classified by Function..........................................................42

2.6.2 Basic Instruction Formats.......................................................................................52

2.7 Addressing Modes and Effective Address Calculation........................................................53

2.7.1 Register DirectRn................................................................................................53

2.7.2 Register Indirect@ERn.......................................................................................53

2.7.3 Register Indirect with Displacement@(d:16, ERn) or @(d:32, ERn).................54

2.7.4 Register Indirect with Post-Increment or Pre-Decrement@ERn or @-ERn.....54

2.7.5 Absolute Address@aa:8, @aa:16, @aa:24, or @aa:32.......................................54

Rev. 2.00 Aug. 20, 2008 Page x of xlviii

2.7.6 Immediate#xx:8, #xx:16, or #xx:32....................................................................55

2.7.7 Program-Counter Relative@(d:8, PC) or @(d:16, PC).......................................55

2.7.8 Memory Indirect@@aa:8...................................................................................56

2.7.9 Effective Address Calculation................................................................................57

2.8 Processing States..................................................................................................................59

2.9 Usage Note...........................................................................................................................61

2.9.1 Notes on Using the Bit Operation Instruction.........................................................61

Section 3 MCU Operating Modes.......................................................................63

3.1 Operating Mode Selection ...................................................................................................63

3.2 Register Descriptions...........................................................................................................64

3.2.1 Mode Control Register (MDCR)............................................................................64

3.2.2 System Control Register (SYSCR).........................................................................65

3.2.3 Serial Timer Control Register (STCR) ...................................................................66

3.3 Operating Mode Descriptions..............................................................................................68

3.3.1 Mode 2....................................................................................................................68

3.4 Address Map........................................................................................................................69

Section 4 Exception Handling.............................................................................71

4.1 Exception Handling Types and Priority...............................................................................71

4.2 Exception Sources and Exception Vector Table..................................................................72

4.3 Reset ....................................................................................................................................74

4.3.1 Reset Exception Handling ......................................................................................74

4.3.2 Interrupts after Reset...............................................................................................75

4.3.3 On-Chip Peripheral Modules after Reset is Cancelled............................................75

4.4 Interrupt Exception Handling...............................................................................................76

4.5 Trap Instruction Exception Handling...................................................................................76

4.6 Stack Status after Exception Handling.................................................................................77

4.7 Usage Note...........................................................................................................................78

Section 5 Interrupt Controller..............................................................................79

5.1 Features................................................................................................................................79

5.2 Input/Output Pins.................................................................................................................80

5.3 Register Descriptions...........................................................................................................81

5.3.1 Interrupt Control Registers A to D (ICRA to ICRD)..............................................81

5.3.2 Address Break Control Register (ABRKCR) .........................................................82

5.3.3 Break Address Registers A to C (BARA to BARC)...............................................83

5.3.4 IRQ Sense Control Registers (ISCR16H, ISCR16L, ISCRH, ISCRL)...................84

5.3.5 IRQ Enable Registers (IER16, IER).......................................................................86

5.3.6 IRQ Status Registers (ISR16, ISR).........................................................................87

Rev. 2.00 Aug. 20, 2008 Page xi of xlviii

5.4 Interrupt Sources..................................................................................................................88

5.4.1 External Interrupts ..................................................................................................88

5.4.2 Internal Interrupts ...................................................................................................89

5.5 Interrupt Exception Handling Vector Table.........................................................................90

5.6 Interrupt Control Modes and Interrupt Operation................................................................93

5.6.1 Interrupt Control Mode 0........................................................................................95

5.6.2 Interrupt Control Mode 1........................................................................................97

5.6.3 Interrupt Exception Handling Sequence...............................................................100

5.6.4 Interrupt Response Times.....................................................................................101

5.6.5 DTC Activation by Interrupt.................................................................................102

5.7 Usage Notes.......................................................................................................................104

5.7.1 Conflict between Interrupt Generation and Disabling ..........................................104

5.7.2 Instructions that Disable Interrupts.......................................................................105

5.7.3 Interrupts during Execution of EEPMOV Instruction...........................................105

5.7.4 IRQ Status Registers (ISR16, ISR).......................................................................105

Section 6 Bus Controller (BSC).........................................................................107

6.1 Features..............................................................................................................................107

6.2 Input/Output Pins...............................................................................................................110

6.3 Register Descriptions.........................................................................................................111

6.3.1 Bus Control Register (BCR).................................................................................111

6.3.2 Bus Control Register 2 (BCR2)............................................................................113

6.3.3 Wait State Control Register (WSCR) ...................................................................114

6.3.4 Wait State Control Register 2 (WSCR2) ..............................................................116

6.3.5 System Control Register 2 (SYSCR2)..................................................................117

6.4 Bus Control........................................................................................................................118

6.4.1 Bus Specifications.................................................................................................118

6.4.2 Advanced Mode....................................................................................................125

6.4.3 I/O Select Signals..................................................................................................126

6.5 Bus Interface......................................................................................................................127

6.5.1 Data Size and Data Alignment..............................................................................127

6.5.2 Valid Strobes.........................................................................................................129

6.5.3 Valid Strobes (in Glueless Extension)..................................................................130

6.5.4 Basic Operation Timing in Normal Extended Mode ............................................131

6.5.5 Basic Operation Timing in Address-Data Multiplex Extended Mode..................142

6.5.6 Wait Control .........................................................................................................150

6.6 Burst ROM Interface..........................................................................................................154

6.6.1 Basic Operation Timing........................................................................................154

6.6.2 Wait Control .........................................................................................................155

6.7 Idle Cycle...........................................................................................................................156

Rev. 2.00 Aug. 20, 2008 Page xii of xlviii

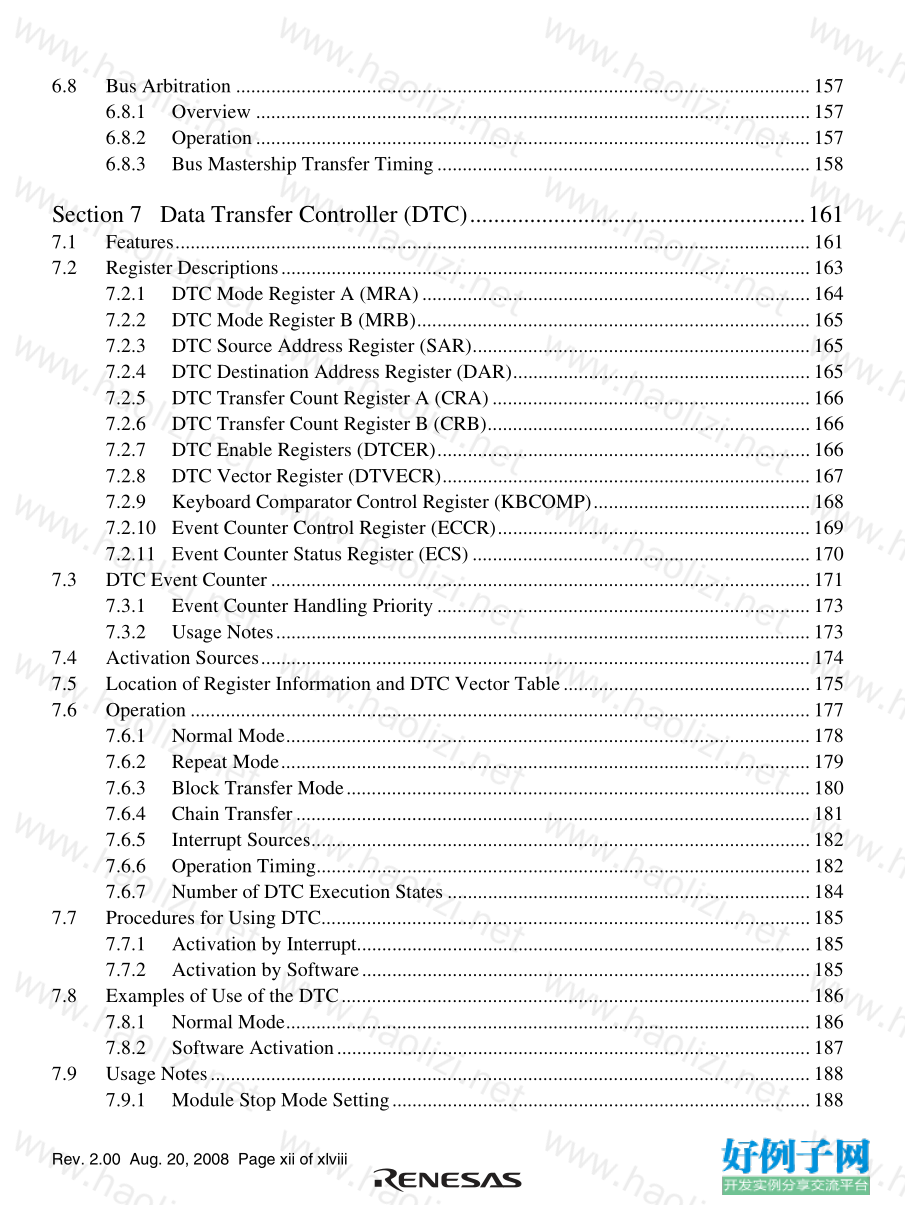

6.8 Bus Arbitration ..................................................................................................................157

6.8.1 Overview ..............................................................................................................157

6.8.2 Operation..............................................................................................................157

6.8.3 Bus Mastership Transfer Timing..........................................................................158

Section 7 Data Transfer Controller (DTC)........................................................161

7.1 Features..............................................................................................................................161

7.2 Register Descriptions.........................................................................................................163

7.2.1 DTC Mode Register A (MRA).............................................................................164

7.2.2 DTC Mode Register B (MRB)..............................................................................165

7.2.3 DTC Source Address Register (SAR)...................................................................165

7.2.4 DTC Destination Address Register (DAR)...........................................................165

7.2.5 DTC Transfer Count Register A (CRA)...............................................................166

7.2.6 DTC Transfer Count Register B (CRB)................................................................166

7.2.7 DTC Enable Registers (DTCER)..........................................................................166

7.2.8 DTC Vector Register (DTVECR).........................................................................167

7.2.9 Keyboard Comparator Control Register (KBCOMP)...........................................168

7.2.10 Event Counter Control Register (ECCR)..............................................................169

7.2.11 Event Counter Status Register (ECS)...................................................................170

7.3 DTC Event Counter...........................................................................................................171

7.3.1 Event Counter Handling Priority..........................................................................173

7.3.2 Usage Notes..........................................................................................................173

7.4 Activation Sources.............................................................................................................174

7.5 Location of Register Information and DTC Vector Table.................................................175

7.6 Operation ...........................................................................................................................177

7.6.1 Normal Mode........................................................................................................178

7.6.2 Repeat Mode.........................................................................................................179

7.6.3 Block Transfer Mode............................................................................................180

7.6.4 Chain Transfer......................................................................................................181

7.6.5 Interrupt Sources...................................................................................................182

7.6.6 Operation Timing..................................................................................................182

7.6.7 Number of DTC Execution States ........................................................................184

7.7 Procedures for Using DTC.................................................................................................185

7.7.1 Activation by Interrupt..........................................................................................185

7.7.2 Activation by Software.........................................................................................185

7.8 Examples of Use of the DTC.............................................................................................186

7.8.1 Normal Mode........................................................................................................186

7.8.2 Software Activation..............................................................................................187

7.9 Usage Notes.......................................................................................................................188

7.9.1 Module Stop Mode Setting...................................................................................188

Rev. 2.00 Aug. 20, 2008 Page xiii of xlviii

7.9.2 On-Chip RAM ......................................................................................................188

7.9.3 DTCE Bit Setting..................................................................................................188

7.9.4 DTC Activation by Interrupt Sources of SCI, IIC, or A/D Converter ..................188

Section 8 I/O Ports.............................................................................................189

8.1 I/O Ports for the H8S/2472 Group.....................................................................................189

8.1.1 Port 1.....................................................................................................................194

8.1.2 Port 2.....................................................................................................................197

8.1.3 Port 3.....................................................................................................................202

8.1.4 Port 4.....................................................................................................................208

8.1.5 Port 5.....................................................................................................................216

8.1.6 Port 6.....................................................................................................................221

8.1.7 Port 7.....................................................................................................................227

8.1.8 Port 8.....................................................................................................................231

8.1.9 Port 9.....................................................................................................................236

8.1.10 Port A....................................................................................................................240

8.1.11 Port B....................................................................................................................248

8.1.12 Port C....................................................................................................................254

8.1.13 Port D....................................................................................................................259

8.1.14 Port E....................................................................................................................264

8.1.15 Port F ....................................................................................................................268

8.2 I/O Ports for the H8S/2463 Group and the H8S/2462 Group ............................................272

8.2.1 Port 1.....................................................................................................................277

8.2.2 Port 2.....................................................................................................................280

8.2.3 Port 3.....................................................................................................................285

8.2.4 Port 4.....................................................................................................................291

8.2.5 Port 5.....................................................................................................................299

8.2.6 Port 6.....................................................................................................................304

8.2.7 Port 7.....................................................................................................................311

8.2.8 Port 8.....................................................................................................................315

8.2.9 Port 9.....................................................................................................................320

8.2.10 Port A....................................................................................................................324

8.2.11 Port B....................................................................................................................332

8.2.12 Port C....................................................................................................................338

8.2.13 Port D....................................................................................................................343

8.2.14 Port E....................................................................................................................348

8.2.15 Port F ....................................................................................................................353

8.3 Change of Peripheral Function Pins...................................................................................356

8.3.1 IRQ Sense Port Select Register 16 (ISSR16), IRQ Sense Port

Select Register (ISSR) ..........................................................................................356

Rev. 2.00 Aug. 20, 2008 Page xiv of xlviii

8.3.2 Port Control Register 0 (PTCNT0).......................................................................358

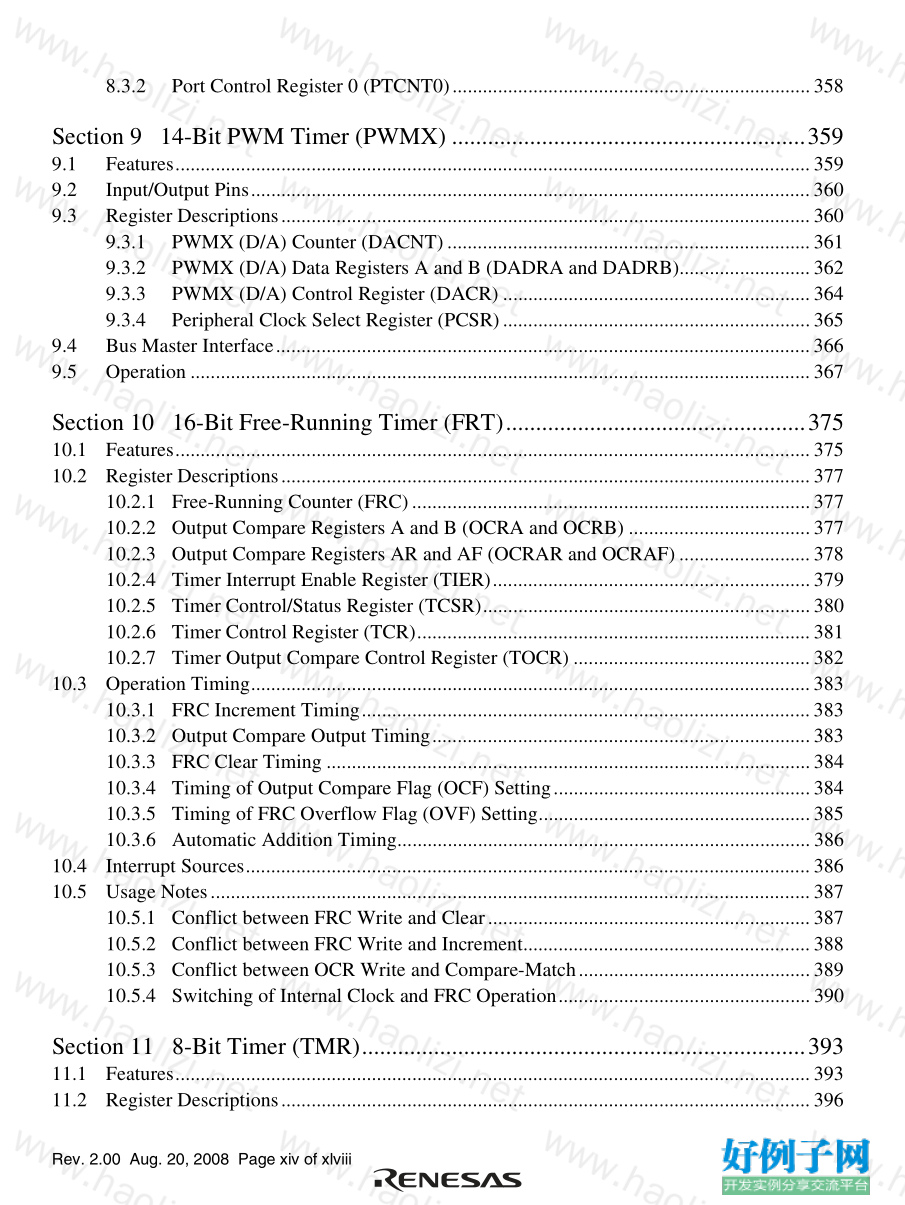

Section 9 14-Bit PWM Timer (PWMX) ...........................................................359

9.1 Features..............................................................................................................................359

9.2 Input/Output Pins...............................................................................................................360

9.3 Register Descriptions.........................................................................................................360

9.3.1 PWMX (D/A) Counter (DACNT)........................................................................361

9.3.2 PWMX (D/A) Data Registers A and B (DADRA and DADRB)..........................362

9.3.3 PWMX (D/A) Control Register (DACR) .............................................................364

9.3.4 Peripheral Clock Select Register (PCSR).............................................................365

9.4 Bus Master Interface..........................................................................................................366

9.5 Operation ...........................................................................................................................367

Section 10 16-Bit Free-Running Timer (FRT)..................................................375

10.1 Features..............................................................................................................................375

10.2 Register Descriptions.........................................................................................................377

10.2.1 Free-Running Counter (FRC)...............................................................................377

10.2.2 Output Compare Registers A and B (OCRA and OCRB) ....................................377

10.2.3 Output Compare Registers AR and AF (OCRAR and OCRAF)..........................378

10.2.4 Timer Interrupt Enable Register (TIER)...............................................................379

10.2.5 Timer Control/Status Register (TCSR).................................................................380

10.2.6 Timer Control Register (TCR)..............................................................................381

10.2.7 Timer Output Compare Control Register (TOCR) ...............................................382

10.3 Operation Timing...............................................................................................................383

10.3.1 FRC Increment Timing.........................................................................................383

10.3.2 Output Compare Output Timing...........................................................................383

10.3.3 FRC Clear Timing ................................................................................................384

10.3.4 Timing of Output Compare Flag (OCF) Setting...................................................384

10.3.5 Timing of FRC Overflow Flag (OVF) Setting......................................................385

10.3.6 Automatic Addition Timing..................................................................................386

10.4 Interrupt Sources................................................................................................................386

10.5 Usage Notes.......................................................................................................................387

10.5.1 Conflict between FRC Write and Clear................................................................387

10.5.2 Conflict between FRC Write and Increment.........................................................388

10.5.3 Conflict between OCR Write and Compare-Match..............................................389

10.5.4 Switching of Internal Clock and FRC Operation..................................................390

Section 11 8-Bit Timer (TMR)..........................................................................393

11.1 Features..............................................................................................................................393

11.2 Register Descriptions.........................................................................................................396

Rev. 2.00 Aug. 20, 2008 Page xv of xlviii

11.2.1 Timer Counter (TCNT).........................................................................................396

11.2.2 Time Constant Register A (TCORA)....................................................................397

11.2.3 Time Constant Register B (TCORB)....................................................................397

11.2.4 Timer Control Register (TCR)..............................................................................398

11.2.5 Timer Control/Status Register (TCSR).................................................................401

11.2.6 Timer Connection Register S (TCONRS).............................................................405

11.3 Operation Timing...............................................................................................................406

11.3.1 TCNT Count Timing.............................................................................................406

11.3.2 Timing of CMFA and CMFB Setting at Compare-Match....................................406

11.3.3 Timing of Counter Clear at Compare-Match........................................................407

11.3.4 Timing of Overflow Flag (OVF) Setting..............................................................407

11.4 TMR_0 and TMR_1 Cascaded Connection.......................................................................408

11.4.1 16-Bit Count Mode...............................................................................................408

11.4.2 Compare-Match Count Mode...............................................................................408

11.5 Interrupt Sources................................................................................................................409

11.6 Usage Notes.......................................................................................................................410

11.6.1 Conflict between TCNT Write and Counter Clear................................................410

11.6.2 Conflict between TCNT Write and Increment......................................................411

11.6.3 Conflict between TCOR Write and Compare-Match............................................412

11.6.4 Switching of Internal Clocks and TCNT Operation..............................................413

11.6.5 Mode Setting with Cascaded Connection.............................................................414

Section 12 Watchdog Timer (WDT)..................................................................415

12.1 Features..............................................................................................................................415

12.2 Input/Output Pins...............................................................................................................417

12.3 Register Descriptions.........................................................................................................417

12.3.1 Timer Counter (TCNT).........................................................................................417

12.3.2 Timer Control/Status Register (TCSR).................................................................418

12.4 Operation ...........................................................................................................................422

12.4.1 Watchdog Timer Mode.........................................................................................422

12.4.2 Interval Timer Mode.............................................................................................424

12.4.3 RESO Signal Output Timing................................................................................425

12.5 Interrupt Sources................................................................................................................426

12.6 Usage Notes.......................................................................................................................427

12.6.1 Notes on Register Access......................................................................................427

12.6.2 Conflict between Timer Counter (TCNT) Write and Increment...........................428

12.6.3 Changing Values of CKS2 to CKS0 Bits..............................................................428

12.6.4 Changing Value of PSS Bit...................................................................................428

12.6.5 Switching between Watchdog Timer Mode and Interval Timer Mode.................429

12.6.6 System Reset by RESO Signal..............................................................................429

Rev. 2.00 Aug. 20, 2008 Page xvi of xlviii

Section 13 Serial Communication Interface (SCI)............................................431

13.1 Features..............................................................................................................................431

13.2 Input/Output Pins...............................................................................................................434

13.3 Register Descriptions.........................................................................................................434

13.3.1 Receive Shift Register (RSR) ...............................................................................435

13.3.2 Receive Data Register (RDR)...............................................................................435

13.3.3 Transmit Data Register (TDR)..............................................................................435

13.3.4 Transmit Shift Register (TSR)..............................................................................435

13.3.5 Serial Mode Register (SMR) ................................................................................436

13.3.6 Serial Control Register (SCR) ..............................................................................439

13.3.7 Serial Status Register (SSR) .................................................................................442

13.3.8 Smart Card Mode Register (SCMR).....................................................................446

13.3.9 Bit Rate Register (BRR).......................................................................................447

13.4 Operation in Asynchronous Mode.....................................................................................451

13.4.1 Data Transfer Format............................................................................................452

13.4.2 Receive Data Sampling Timing and Reception Margin in

Asynchronous Mode.............................................................................................453

13.4.3 Clock.....................................................................................................................454

13.4.4 SCI Initialization (Asynchronous Mode)..............................................................455

13.4.5 Serial Data Transmission (Asynchronous Mode).................................................456

13.4.6 Serial Data Reception (Asynchronous Mode) ......................................................458

13.5 Multiprocessor Communication Function..........................................................................462

13.5.1 Multiprocessor Serial Data Transmission.............................................................464

13.5.2 Multiprocessor Serial Data Reception..................................................................465

13.6 Operation in Clock Synchronous Mode.............................................................................468

13.6.1 Clock.....................................................................................................................468

13.6.2 SCI Initialization (Clock Synchronous Mode)......................................................469

13.6.3 Serial Data Transmission (Clock Synchronous Mode).........................................470

13.6.4 Serial Data Reception (Clock Synchronous Mode)..............................................473

13.6.5 Simultaneous Serial Data Transmission and Reception

(Clock Synchronous Mode)..................................................................................475

13.7 Smart Card Interface Description ......................................................................................477

13.7.1 Sample Connection...............................................................................................477

13.7.2 Data Format (Except in Block Transfer Mode)....................................................477

13.7.3 Block Transfer Mode............................................................................................479

13.7.4 Receive Data Sampling Timing and Reception Margin .......................................480

13.7.5 Initialization..........................................................................................................481

13.7.6 Serial Data Transmission (Except in Block Transfer Mode)................................482

13.7.7 Serial Data Reception (Except in Block Transfer Mode) .....................................485

13.7.8 Clock Output Control............................................................................................487

Rev. 2.00 Aug. 20, 2008 Page xvii of xlviii

13.8 Interrupt Sources................................................................................................................489

13.8.1 Interrupts in Normal Serial Communication Interface Mode ...............................489

13.8.2 Interrupts in Smart Card Interface Mode..............................................................490

13.9 Usage Notes.......................................................................................................................491

13.9.1 Module Stop Mode Setting...................................................................................491

13.9.2 Break Detection and Processing ...........................................................................491

13.9.3 Mark State and Break Sending..............................................................................491

13.9.4 Receive Error Flags and Transmit Operations

(Clock Synchronous Mode Only).........................................................................491

13.9.5 Relation between Writing to TDR and TDRE Flag..............................................491

13.9.6 Restrictions on Using DTC...................................................................................492

13.9.7 SCI Operations during Mode Transitions.............................................................493

13.9.8 Notes on Switching from SCK Pins to Port Pins..................................................497

Section 14 CRC Operation Circuit (CRC).........................................................499

14.1 Features..............................................................................................................................499

14.2 Register Descriptions.........................................................................................................500

14.2.1 CRC Control Register (CRCCR)..........................................................................500

14.2.2 CRC Data Input Register (CRCDIR)....................................................................501

14.2.3 CRC Data Output Register (CRCDOR)................................................................501

14.3 CRC Operation Circuit Operation......................................................................................501

14.4 Note on CRC Operation Circuit.........................................................................................505

Section 15 Serial Communication Interface with FIFO (SCIF)........................507

15.1 Features..............................................................................................................................507

15.2 Input/Output Pins...............................................................................................................509

15.3 Register Descriptions.........................................................................................................510

15.3.1 Receive Shift Register (FRSR).............................................................................511

15.3.2 Receive Buffer Register (FRBR)..........................................................................511

15.3.3 Transmitter Shift Register (FTSR)........................................................................511

15.3.4 Transmitter Holding Register (FTHR)..................................................................512

15.3.5 Divisor Latch H, L (FDLH, FDLL)......................................................................512

15.3.6 Interrupt Enable Register (FIER)..........................................................................513

15.3.7 Interrupt Identification Register (FIIR).................................................................514

15.3.8 FIFO Control Register (FFCR).............................................................................516

15.3.9 Line Control Register (FLCR)..............................................................................517

15.3.10 Modem Control Register (FMCR)........................................................................518

15.3.11 Line Status Register (FLSR).................................................................................520

15.3.12 Modem Status Register (FMSR)...........................................................................524

15.3.13 Scratch Pad Register (FSCR)................................................................................525

Rev. 2.00 Aug. 20, 2008 Page xviii of xlviii

15.3.14 SCIF Control Register (SCIFCR).........................................................................526

15.4 Operation ...........................................................................................................................528

15.4.1 Baud Rate .............................................................................................................528

15.4.2 Operation in Asynchronous Communication........................................................529

15.4.3 Initialization of the SCIF ......................................................................................530

15.4.4 Data Transmission/Reception with Flow Control.................................................533

15.4.5 Data Transmission/Reception Through the LPC Interface...................................539

15.5 Interrupt Sources................................................................................................................541

15.6 Usage Note.........................................................................................................................541

15.6.1 Power-Down Mode When LCLK is Selected for SCLK......................................541

Section 16 Serial Pin Multiplexed Modes.........................................................543

16.1 Features..............................................................................................................................543

16.2 Input/Output Pins...............................................................................................................544

16.3 Register Descriptions.........................................................................................................545

16.3.1 Serial Multiplexed Mode Register 0 (SMR0).......................................................545

16.3.2 Serial Multiplexed Mode Register 1 (SMR1).......................................................546

16.4 Operation of Serial Pin Multiplexed Modes......................................................................547

16.4.1 Serial Pin Multiplexed Mode 0

(Default; SMR0 Register [bits SM2, SM1, SM0] = [0 0 0]).................................547

16.4.2 Serial Pin Multiplexed Mode 1

(SMR0 Register [bits SM2, SM1, SM0] = [0 0 1])...............................................548

16.4.3 Serial Pin Multiplexed Mode 2

(SMR0 Register [bits SM2, SM1, SM0] = [0 1 0])...............................................549

16.4.4 Serial Pin Multiplexed Mode 3

(SMR0 Register [bits SM2, SM1, SM0] = [0 1 1])...............................................550

16.4.5 Serial Pin Multiplexed Mode 4

(SMR0 Register [bits SM2, SM1, SM0] = [1 0 0])...............................................551

16.5 Serial Port Pin Configuration.............................................................................................552

Section 17 Synchronous Serial Communication Unit (SSU)............................553

17.1 Features..............................................................................................................................553

17.2 Input/Output Pins...............................................................................................................555

17.3 Register Descriptions.........................................................................................................555

17.3.1 SS Control Register H (SSCRH) ..........................................................................556

17.3.2 SS Control Register L (SSCRL)...........................................................................558

17.3.3 SS Mode Register (SSMR)...................................................................................559

17.3.4 SS Enable Register (SSER) ..................................................................................560

17.3.5 SS Status Register (SSSR)....................................................................................561

17.3.6 SS Control Register 2 (SSCR2)............................................................................563

Rev. 2.00 Aug. 20, 2008 Page xix of xlviii

17.3.7 SS Transmit Data Registers 0 to 3 (SSTDR0 to SSTDR3)...................................564

17.3.8 SS Receive Data Registers 0 to 3 (SSRDR0 to SSRDR3)....................................565

17.3.9 SS Shift Register (SSTRSR).................................................................................565

17.4 Operation ...........................................................................................................................566

17.4.1 Transfer Clock......................................................................................................566

17.4.2 Relationship of Clock Phase, Polarity, and Data ..................................................566

17.4.3 Relationship between Data Input/Output Pins and Shift Register ........................567

17.4.4 Communication Modes and Pin Functions...........................................................568

17.4.5 SSU Mode.............................................................................................................570

17.4.6 SCS Pin Control and Conflict Error......................................................................578

17.4.7 Clock Synchronous Communication Mode..........................................................579

17.5 Interrupt Requests..............................................................................................................585

17.6 Usage Note.........................................................................................................................585

17.6.1 Setting of Module Stop Mode...............................................................................585

Section 18 I

2 C Bus Interface (IIC).....................................................................587

18.1 Features..............................................................................................................................587

18.2 Input/Output Pins...............................................................................................................590

18.3 Register Descriptions.........................................................................................................591

18.3.1 I

2 C Bus Data Register (ICDR) ..............................................................................591

18.3.2 Slave Address Register (SAR)..............................................................................592

18.3.3 Second Slave Address Register (SARX) ..............................................................593

18.3.4 I

2 C Bus Mode Register (ICMR)............................................................................595

18.3.5 I

2 C Bus Transfer Rate Select Register (IICX3).....................................................597

18.3.6 I

2 C Bus Control Register (ICCR)..........................................................................600

18.3.7 I

2 C Bus Status Register (ICSR).............................................................................609

18.3.8 I

2 C Bus Extended Control Register (ICXR)..........................................................613

18.3.9 I

2 C SMBus Control Register (ICSMBCR)............................................................617

18.4 Operation ...........................................................................................................................619

18.4.1 I

2 C Bus Data Format.............................................................................................619

18.4.2 Initialization..........................................................................................................621

18.4.3 Master Transmit Operation...................................................................................621

18.4.4 Master Receive Operation.....................................................................................625

18.4.5 Slave Receive Operation.......................................................................................634

18.4.6 Slave Transmit Operation.....................................................................................642

18.4.7 IRIC Setting Timing and SCL Control.................................................................645

18.4.8 Operation Using the DTC.....................................................................................648

18.4.9 Noise Canceler......................................................................................................650

18.4.10 Initialization of Internal State ...............................................................................650

18.5 Interrupt Source .................................................................................................................652

Rev. 2.00 Aug. 20, 2008 Page xx of xlviii

18.6 Usage Notes.......................................................................................................................653

Section 19 LPC Interface (LPC)........................................................................665

19.1 Features..............................................................................................................................665

19.2 Input/Output Pins...............................................................................................................668

19.3 Register Descriptions.........................................................................................................669

19.3.1 Host Interface Control Registers 0 and 1 (HICR0 and HICR1)............................671

19.3.2 Host Interface Control Registers 2 and 3 (HICR2 and HICR3)............................679

19.3.3 Host Interface Control Register 4 (HICR4)..........................................................682

19.3.4 Host Interface Control Register 5 (HICR5)..........................................................683

19.3.5 Pin Function Control Register (PINFNCR)..........................................................684

19.3.6 LPC Channel 1, 2 Address Register H, L (LADR12H, LADR12L).....................684

19.3.7 LPC Channel 3 Address Register H, L (LADR3H, LADR3L).............................686

19.3.8 Input Data Registers 1 to 3 (IDR1 to IDR3).........................................................689

19.3.9 Output Data Registers 0 to 3 (ODR1 to ODR3) ...................................................689

19.3.10 Bidirectional Data Registers 0 to 15 (TWR0 to TWR15).....................................690

19.3.11 Status Registers 1 to 3 (STR1 to STR3) ...............................................................691

19.3.12 SERIRQ Control Register 0 (SIRQCR0)..............................................................699

19.3.13 SERIRQ Control Register 1 (SIRQCR1)..............................................................703

19.3.14 SERIRQ Control Register 2 (SIRQCR2)..............................................................707

19.3.15 SERIRQ Control Register 3 (SIRQCR3)..............................................................708

19.3.16 SERIRQ Control Register 4 (SIRQCR4)..............................................................709

19.3.17 SERIRQ Control Register 5 (SIRQCR5)..............................................................710

19.3.18 Host Interface Select Register (HISEL)................................................................711

19.3.19 SCIF Address Register (SCIFADRH, SCIFADRL).............................................712

19.3.20 SMIC Flag Register (SMICFLG) .........................................................................713

19.3.21 SMIC Control Status Register (SMICCSR)..........................................................714

19.3.22 SMIC Data Register (SMICDTR) ........................................................................714

19.3.23 SMIC Interrupt Register 0 (SMICIR0).................................................................715

19.3.24 SMIC Interrupt Register 1 (SMICIR1).................................................................717

19.3.25 BT Status Register 0 (BTSR0)..............................................................................718

19.3.26 BT Status Register 1 (BTSR1)..............................................................................721

19.3.27 BT Control Status Register 0 (BTCSR0)..............................................................724

19.3.28 BT Control Status Register 1 (BTCSR1)..............................................................725

19.3.29 BT Control Register (BTCR)................................................................................727

19.3.30 BT Data Buffer (BTDTR).....................................................................................730

19.3.31 BT Interrupt Mask Register (BTIMSR)................................................................730

19.3.32 BT FIFO Valid Size Register 0 (BTFVSR0)........................................................732

19.3.33 BT FIFO Valid Size Register 1 (BTFVSR1)........................................................732

Rev. 2.00 Aug. 20, 2008 Page xxi of xlviii

19.4 Operation ...........................................................................................................................733

19.4.1 LPC interface Activation ......................................................................................733

19.4.2 LPC I/O Cycles.....................................................................................................733

19.4.3 SMIC Mode Transfer Flow...................................................................................735

19.4.4 BT Mode Transfer Flow.......................................................................................738

19.4.5 Gate A20...............................................................................................................740

19.4.6 LPC Interface Shutdown Function (LPCPD)........................................................743

19.4.7 LPC Interface Serialized Interrupt Operation (SERIRQ)......................................747

19.4.8 LPC Interface Clock Start Request.......................................................................749

19.4.9 SCIF Control from LPC Interface.........................................................................749

19.5 Interrupt Sources................................................................................................................750

19.5.1 IBFI1, IBFI2, IBFI3, and ERRI............................................................................750

19.5.2 SMI, HIRQ1, HIRQ3, HIRQ4, HIRQ5, HIRQ6, HIRQ7, HIRQ8, HIRQ9,

HIRQ10, HIRQ11, HIRQ12, HIRQ13, HIRQ14, and HIRQ15............................751

19.6 Usage Note.........................................................................................................................754

19.6.1 Data Conflict.........................................................................................................754

Section 20 Ethernet Controller (EtherC)............................................................757

20.1 Features..............................................................................................................................757

20.2 Input/Output Pins...............................................................................................................759

20.3 Register Description...........................................................................................................760

20.3.1 EtherC Mode Register (ECMR)............................................................................761

20.3.2 EtherC Status Register (ECSR).............................................................................764

20.3.3 EtherC Interrupt Permission Register (ECSIPR)..................................................766

20.3.4 PHY Interface Register (PIR)...............................................................................767

20.3.5 MAC Address High Register (MAHR).................................................................768

20.3.6 MAC Address Low Register (MALR)..................................................................768

20.3.7 Receive Frame Length Register (RFLR) ..............................................................769

20.3.8 PHY Status Register (PSR)...................................................................................770

20.3.9 Transmit Retry Over Counter Register (TROCR) ................................................770

20.3.10 Delayed Collision Detect Counter Register (CDCR)............................................771

20.3.11 Lost Carrier Counter Register (LCCR).................................................................771

20.3.12 Carrier Not Detect Counter Register (CNDCR) ...................................................771

20.3.13 CRC Error Frame Counter Register (CEFCR)......................................................772

20.3.14 Frame Receive Error Counter Register (FRECR).................................................772

20.3.15 Too-Short Frame Receive Counter Register (TSFRCR).......................................772

20.3.16 Too-Long Frame Receive Counter Register (TLFRCR).......................................773

20.3.17 Residual-Bit Frame Counter Register (RFCR).....................................................773

20.3.18 Multicast Address Frame Counter Register (MAFCR).........................................773

20.3.19 IPG Register (IPGR).............................................................................................774

Rev. 2.00 Aug. 20, 2008 Page xxii of xlviii

20.3.20 Automatic PAUSE Frame Set Register (APR).....................................................774

20.3.21 Manual PAUSE Frame Set Register (MPR).........................................................775

20.3.22 Automatic PAUSE Frame Retransmission Count Set Register (TPAUSER).......775

20.4 Operation ...........................................................................................................................776

20.4.1 Transmission.........................................................................................................776

20.4.2 Reception..............................................................................................................779

20.4.3 RMII Frame Timing..............................................................................................780

20.4.4 Accessing MII Registers.......................................................................................782

20.4.5 Magic Packet Detection........................................................................................785

20.4.6 Operation by IPG Setting......................................................................................786

20.4.7 Flow Control.........................................................................................................786

20.5 Usage Notes.......................................................................................................................788

20.5.1 Conditions for Setting LCHNG Bit ......................................................................788

20.5.2 Flow Control Defect 1..........................................................................................788

20.5.3 Flow Control Defect 2..........................................................................................788

20.5.4 Operation Seed......................................................................................................789

Section 21 Ethernet Controller Direct Memory Access Controller

(E-DMAC).......................................................................................791

21.1 Features..............................................................................................................................791

21.2 Register Descriptions.........................................................................................................792

21.2.1 E-DMAC Mode Register (EDMR).......................................................................794

21.2.2 E-DMAC Transmit Request Register (EDTRR)...................................................795

21.2.3 E-DMAC Receive Request Register (EDRRR)....................................................796

21.2.4 Transmit Descriptor List Address Register (TDLAR)..........................................797

21.2.5 Receive Descriptor List Address Register (RDLAR)...........................................797

21.2.6 EtherC/E-DMAC Status Register (EESR)............................................................798

21.2.7 EtherC/E-DMAC Status Interrupt Permission Register (EESIPR).......................803

21.2.8 Transmit/Receive Status Copy Enable Register (TRSCER).................................806

21.2.9 Receive Missed-Frame Counter Register (RMFCR)............................................806

21.2.10 Transmit FIFO Threshold Register (TFTR)..........................................................807

21.2.11 FIFO Depth Register (FDR) .................................................................................809

21.2.12 Receiving method Control Register (RMCR).......................................................810

21.2.13 Receiving-Buffer Write Address Register (RBWAR)..........................................810

21.2.14 Receiving-Descriptor Fetch Address Register (RDFAR).....................................811

21.2.15 Transmission-Buffer Read Address Register (TBRAR).......................................811

21.2.16 Transmission-Descriptor Fetch Address Register (TDFAR)................................811

21.2.17 Flow Control FIFO Threshold Register (FCFTR)................................................812

21.2.18 Bit Rate Setting Register (ECBRR)......................................................................813

21.2.19 Transmit Interrupt Register (TRIMD) ..................................................................814

Rev. 2.00 Aug. 20, 2008 Page xxiii of xlviii

21.3 Operation ...........................................................................................................................815

21.3.1 Descriptor List and Data Buffers..........................................................................815

21.3.2 Transmission.........................................................................................................825

21.3.3 Reception..............................................................................................................827

21.3.4 Multi-Buffer Frame Transmit/Receive Processing...............................................829

Section 22 USB Function Module (USB)..........................................................831

22.1 Features..............................................................................................................................831

22.2 Input/Output Pins...............................................................................................................832

22.3 Register Descriptions.........................................................................................................833

22.3.1 Interrupt Flag Register 0 (IFR0)...........................................................................834

22.3.2 Interrupt Flag Register 1 (IFR1)...........................................................................836

22.3.3 Interrupt Flag Register 2 (IFR2)...........................................................................837

22.3.4 Interrupt Select Register 0 (ISR0).........................................................................838

22.3.5 Interrupt Select Register 1 (ISR1).........................................................................839

22.3.6 Interrupt Select Register 2 (ISR2).........................................................................839

22.3.7 Interrupt Enable Register 0 (IER0).......................................................................840

22.3.8 Interrupt Enable Register 1 (IER1).......................................................................840

22.3.9 Interrupt Enable Register 2 (IER2).......................................................................841

22.3.10 EP0i Data Register (EPDR0i)...............................................................................841

22.3.11 EP0o Data Register (EPDR0o).............................................................................842

22.3.12 EP0s Data Register (EPDR0s)..............................................................................842

22.3.13 EP1 Data Register (EPDR1).................................................................................843

22.3.14 EP2 Data Register (EPDR2).................................................................................843

22.3.15 EP3 Data Register (EPDR3).................................................................................843

22.3.16 EP0o Receive Data Size Register (EPSZ0o) ........................................................844

22.3.17 EP1 Receive Data Size Register (EPSZ1) ............................................................844

22.3.18 Trigger Register (TRG).........................................................................................844

22.3.19 Data Status Register (DASTS)..............................................................................846

22.3.20 FIFO Clear Register (FCLR)................................................................................847

22.3.21 DTC Transfer Setting Register (DMA) ................................................................848

22.3.22 Endpoint Stall Register (EPSTL)..........................................................................851

22.3.23 Configuration Value Register (CVR) ...................................................................852

22.3.24 Control Register (CTLR)......................................................................................852

22.3.25 Endpoint Information Register (EPIR).................................................................854

22.3.26 Transceiver Test Register 0 (TRNTREG0)...........................................................858

22.3.27 Transceiver Test Register 1 (TRNTREG1)...........................................................859

22.4 Interrupt Sources................................................................................................................861

22.5 Operation ...........................................................................................................................863

22.5.1 Operation at Cable Connection.............................................................................863

Rev. 2.00 Aug. 20, 2008 Page xxiv of xlviii

22.5.2 Operation at Cable Disconnection........................................................................864

22.5.3 Suspend and Resume Operations..........................................................................865

22.5.4 Control Transfer....................................................................................................870

22.5.5 EP1 Bulk-Out Transfer (Dual FIFOs)...................................................................876

22.5.6 EP2 Bulk-In Transfer (Dual FIFOs).....................................................................877

22.5.7 EP3 Interrupt-In Transfer......................................................................................879

22.6 Processing of USB Standard Commands and Class/Vendor Commands ..........................880

22.6.1 Processing of Commands Transmitted by Control Transfer.................................880

22.7 Stall Operations..................................................................................................................881

22.7.1 Overview ..............................................................................................................881

22.7.2 Forcible Stall by Application................................................................................881

22.7.3 Automatic Stall by USB Function Module...........................................................883

22.8 DTC Transfer.....................................................................................................................884

22.8.1 Overview ..............................................................................................................884

22.8.2 DTC Transfer for Endpoint 1................................................................................885

22.8.3 DTC Transfer for Endpoint 2................................................................................886

22.8.4 DTC Transfer End Interrupt..................................................................................887

22.9 Example of USB External Circuitry ..................................................................................888

22.10 Usage Notes.......................................................................................................................890

22.10.1 Receiving Setup Data............................................................................................890

22.10.2 Clearing the FIFO.................................................................................................890

22.10.3 Overreading and Overwriting the Data Registers.................................................890

22.10.4 Assigning Interrupt Sources to EP0......................................................................891

22.10.5 Clearing the FIFO When DTC Transfer is Enabled..............................................891

22.10.6 Notes on TR Interrupt...........................................................................................891

22.10.7 Restrictions on Peripheral Module Clock (φ) Operating Frequency.....................892

Section 23 A/D Converter.................................................................................893

23.1 Features..............................................................................................................................893

23.2 Input/Output Pins...............................................................................................................895

23.3 Register Descriptions.........................................................................................................896

23.3.1 A/D Data Registers A to H (ADDRA to ADDRH) ..............................................896

23.3.2 A/D Control/Status Register (ADCSR) ................................................................897

23.3.3 A/D Control Register (ADCR).............................................................................899

23.4 Operation ...........................................................................................................................900

23.4.1 Single Mode..........................................................................................................900

23.4.2 Scan Mode............................................................................................................901

23.4.3 Input Sampling and A/D Conversion Time ..........................................................903

23.4.4 Timing of External Trigger Input .........................................................................906

23.5 Interrupt Source.................................................................................................................907

Rev. 2.00 Aug. 20, 2008 Page xxv of xlviii

23.6 A/D Conversion Accuracy Definitions..............................................................................907

23.7 Usage Notes.......................................................................................................................909

23.7.1 Setting of Module Stop Mode...............................................................................909

23.7.2 Permissible Signal Source Impedance..................................................................909

23.7.3 Influences on Absolute Accuracy.........................................................................910

23.7.4 Setting Range of Analog Power Supply and Other Pins.......................................910

23.7.5 Notes on Board Design.........................................................................................910

23.7.6 Notes on Noise Countermeasures.........................................................................911

23.7.7 Note on the Usage in Software Standby Mode.....................................................912

Section 24 RAM ................................................................................................913

Section 25 Flash Memory..................................................................................915

25.1 Features..............................................................................................................................915

25.1.1 Operating Mode....................................................................................................917

25.1.2 Mode Comparison.................................................................................................918

25.1.3 Flash Memory MAT Configuration......................................................................919

25.1.4 Block Division......................................................................................................919

25.1.5 Programming/Erasing Interface............................................................................921

25.2 Input/Output Pins...............................................................................................................923

25.3 Register Descriptions.........................................................................................................924

25.3.1 Programming/Erasing Interface Register..............................................................926

25.3.2 Programming/Erasing Interface Parameter...........................................................934

25.4 On-Board Programming Mode ..........................................................................................945

25.4.1 Boot Mode............................................................................................................946

25.4.2 USB Boot Mode....................................................................................................950

25.4.3 User Program Mode..............................................................................................954

25.4.4 User Boot Mode....................................................................................................965