实例介绍

【实例简介】SiI9134手册-Lattice-SiI9134

SiI9134 HDMI深彩色发射机是支持HDMI 1.3规范的第三代高清多媒体接口(HDMI)发射机。这种完全符合HDMI的设备提供了一种简单、低成本的发送受保护数字音频和视频的方法,为最终用户提供了真正的全数字体验。AV接收器,以及蓝光和HD DVD播放器/录像机,可以通过简单、低成本的电缆提供高质量的数字音频和视频。内置的与DVI 1.0规范的向后兼容性允许HDMI系统连接到DVI 1.0显示器。SiI9134发射机通过支持30位和36位深彩色,扩展了Silicon Image系列HDMI发射机。它通过增加TMDS时钟频率并将额外的位打包到下一个字节中,对10/12位深彩色视频输入数据执行10/12位到8位的转换。

【实例截图】

【核心代码】

Table of Contents

General Description...................................................................................................................................................... 1

Features ..................................................................................................................................................................... 1

SiI9134 Transmitter Pin Diagram............................................................................................................................... 3

Functional Description................................................................................................................................................. 4

SiI9134 HDMI Deep Color Transmitter Compared with SiI9030/9034 devices.................................................. 4

Video Data Input and Conversion........................................................................................................................... 5

Video Processing Pipeline ...................................................................................................................................... 5

Input Clock Multiplier/Divider............................................................................................................................... 5

Video Data Capture Logic...................................................................................................................................... 5

Configuration to Support Deep-color..................................................................................................................... 5

Common Video Input Formats................................................................................................................................ 6

Embedded Sync Decoding...................................................................................................................................... 6

Data Enable Generator............................................................................................................................................ 6

Re-sampling............................................................................................................................................................ 6

Color Space Converters (CSC)............................................................................................................................... 7

14-to-8/10/12-Dither............................................................................................................................................... 7

Color Range Scaling............................................................................................................................................... 8

Clipping.................................................................................................................................................................. 8

HDCP Encryption Engine/XOR Mask ................................................................................................................... 8

TMDS Digital Core ................................................................................................................................................ 8

Audio Data Capture Logic....................................................................................................................................... 9

S/PDIF.................................................................................................................................................................... 9

I 2 S ........................................................................................................................................................................... 9

One-Bit Audio Input (DSD/SACD)........................................................................................................................ 9

High-Bit Rate Audio on HDMI .............................................................................................................................. 9

Audio DownSampler Limitations.......................................................................................................................... 10

HDCP Key ROM .....................................................................................................................................................11

Interrupt Out...........................................................................................................................................................11

Control and Configuration .................................................................................................................................... 12

Registers/Configuration Logic.............................................................................................................................. 12

Microcontroller Slave I 2 C Interface...................................................................................................................... 12

DDC Master I 2 C Interface .................................................................................................................................... 12

Electrical Specifications ............................................................................................................................................. 13

Absolute Maximum Conditions............................................................................................................................. 13

Normal Operating Conditions............................................................................................................................... 13

DC Specifications.................................................................................................................................................... 14

Digital I/O Specifications 1 .................................................................................................................................... 14

DC Power Supply Pin Specifications................................................................................................................... 15

AC Specifications.................................................................................................................................................... 16

TMDS AC Timing Specifications......................................................................................................................... 16

Audio AC Timing Specifications.......................................................................................................................... 17

Video AC Timing Specifications .......................................................................................................................... 18

Control Timing Specifications.............................................................................................................................. 19

Timing Diagrams.................................................................................................................................................... 20

Input Timing Diagrams......................................................................................................................................... 20

Audio Timing Diagrams....................................................................................................................................... 22

Power Supply Sequencing.................................................................................................................................... 23

Output Timing Diagrams...................................................................................................................................... 23

© 2007 Silicon Image, Inc. CONFIDENTIAL iii SiI-DS-0193-D

Silicon Image

Confidential

for

Radar and Avionics

Institute of AVIC

Internal Use Only

SiI9134 HDMI Deep Color Transmitter

Data Sheet

Silicon Image, Inc.

Pin Descriptions.......................................................................................................................................................... 24

Video and Audio Input Pins................................................................................................................................... 24

Configuration/Programming Pins......................................................................................................................... 25

Control Pins............................................................................................................................................................. 25

Differential Signal Data Pins ................................................................................................................................. 26

Power and Ground Pins......................................................................................................................................... 26

Data Bus Mappings .................................................................................................................................................... 27

RGB and YCbCr 4:4:4 Formats with Separate Syncs .......................................................................................... 28

YC 4:2:2 Formats with Separate Syncs................................................................................................................ 31

YC 4:2:2 Formats with Embedded Sync .............................................................................................................. 32

YC Mux 4:2:2 Formats with Separate Syncs........................................................................................................ 34

YC Mux 4:2:2 Embedded Sync Formats.............................................................................................................. 36

12/15/18-Bit DMO RGB and YCbCr Formats..................................................................................................... 38

Design Guidelines ....................................................................................................................................................... 39

Power Supplies........................................................................................................................................................ 39

Voltage Ripple Regulation.................................................................................................................................... 39

Decoupling............................................................................................................................................................ 39

High-Speed TMDS Signals..................................................................................................................................... 40

ESD Protection..................................................................................................................................................... 40

Transmitter Layout Guidelines............................................................................................................................. 40

Protection for I 2 C Port........................................................................................................................................... 41

Hot Plug Signal Conditioning................................................................................................................................ 41

HDMI Design Considerations................................................................................................................................ 41

HDMI CTS Test ID 7-4: TMDS Differential Rise and Fall Time......................................................................... 41

Recommendation to pass Test ID 7-4................................................................................................................... 41

EMI Considerations ............................................................................................................................................... 41

Typical Circuit ........................................................................................................................................................ 42

Power Supply Decoupling.................................................................................................................................... 42

HDMI Port TMDS Connections........................................................................................................................... 43

Control Signal Connections.................................................................................................................................. 44

Packaging .................................................................................................................................................................... 45

100-pin TQFP Package Dimensions and Marking Specification........................................................................ 45

Ordering Information ................................................................................................................................................ 46

SiI-DS-0193-D iv © 2007 Silicon Image, Inc. CONFIDENTIAL

Silicon Image

Confidential

for

Radar and Avionics

Institute of AVIC

Internal Use Only

SiI9134 HDMI Deep Color Transmitter

Data Sheet

Silicon Image, Inc.

List of Figures

Figure 1. Functional Block Diagram.............................................................................................................................. 1

Figure 2. 100-Pin TQFP Pinout Diagram....................................................................................................................... 3

Figure 3. Simplified Host I 2 C Ports................................................................................................................................ 4

Figure 4. Transmitter Video Data Processing Path......................................................................................................... 5

Figure 5: High Speed Data Transmission..................................................................................................................... 10

Figure 6: High Bitrate Stream Before and after Reassembly and Splitting.................................................................. 10

Figure 7. High Bit Rate Stream After Splitting............................................................................................................. 10

Figure 8. Master I 2 C Supported Transactions............................................................................................................... 12

Figure 9. IDCK Clock Cycle/High/Low Times............................................................................................................ 20

Figure 10. Control and Data Single-Edge Setup/Hold Times to IDCK........................................................................ 20

Figure 11. Dual-Edge Setup/Hold Times to IDCK....................................................................................................... 20

Figure 12. VSYNC and HSYNC Delay Times from/to DE.......................................................................................... 21

Figure 13. DE High/Low Times ................................................................................................................................... 21

Figure 14. RESET# Minimum Timings........................................................................................................................ 21

Figure 15. S/PDIF Input Timings ................................................................................................................................. 22

Figure 16. I 2 S Input Timings ........................................................................................................................................ 22

Figure 17. DSD Input Timings..................................................................................................................................... 22

Figure 18. MCLK Timings .......................................................................................................................................... 22

Figure 19. Power Supply Sequencing........................................................................................................................... 23

Figure 20. Differential Transition Times ...................................................................................................................... 23

Figure 21. I 2 C Data Valid Delay (Driving Read Cycle Data)....................................................................................... 23

Figure 22. INT Output Pin Response to HPD Input Change........................................................................................ 23

Figure 23. 4:4:4 RGB 36-Bit Timing Diagram............................................................................................................. 29

Figure 24. 4:4:4 YCbCr 36-Bit Timing Diagram.......................................................................................................... 29

Figure 25. 4:4:4 RGB 30-Bit Timing Diagram............................................................................................................. 29

Figure 26. 4:4:4 YCbCr 30-Bit Timing Diagram.......................................................................................................... 30

Figure 27. 4:4:4 RGB 24-Bit Timing Diagram............................................................................................................. 30

Figure 28. Figure 24. 4:4:4 RGB 24-Bit Timing Diagram ........................................................................................... 30

Figure 29. YC 4:2:2 12-Bit per Pixel Timing Diagram................................................................................................ 33

Figure 30. YC 4:2:2 10-Bit per Pixel Timing Diagram................................................................................................ 33

Figure 31. YC 4:2:2 8-Bit per Pixel Timing Diagram.................................................................................................. 33

Figure 32. YC Mux 4:2:2 Timing Diagram.................................................................................................................. 35

Figure 33. YC Mux 4:2:2 Embedded Sync Encoding Timing Diagram....................................................................... 37

Figure 34. 12-Bit Input DMO Timing Diagram ........................................................................................................... 38

Figure 35. Decoupling and Bypass Capacitor Placement............................................................................................. 39

Figure 36. Decoupling and Bypass Schematic ............................................................................................................. 39

Figure 37. Transmitter to HDMI Connector Routing – Top View................................................................................ 40

Figure 38. Power Supply Decoupling and PLL Filtering Schematic............................................................................ 42

Figure 39. HDMI Port TMDS Connections Schematic................................................................................................ 43

Figure 40. HDMI Port ESD Protection Schematic....................................................................................................... 43

Figure 41. Controller Connections Schematic.............................................................................................................. 44

Figure 42. 13 mm x 13 mm TQFP Package Diagram................................................................................................... 45

© 2007 Silicon Image, Inc. CONFIDENTIAL v SiI-DS-0193-D

Silicon Image

Confidential

for

Radar and Avionics

Institute of AVIC

Internal Use Only

SiI9134 HDMI Deep Color Transmitter

Data Sheet

Silicon Image, Inc.

SiI-DS-0193-D vi © 2007 Silicon Image, Inc. CONFIDENTIAL

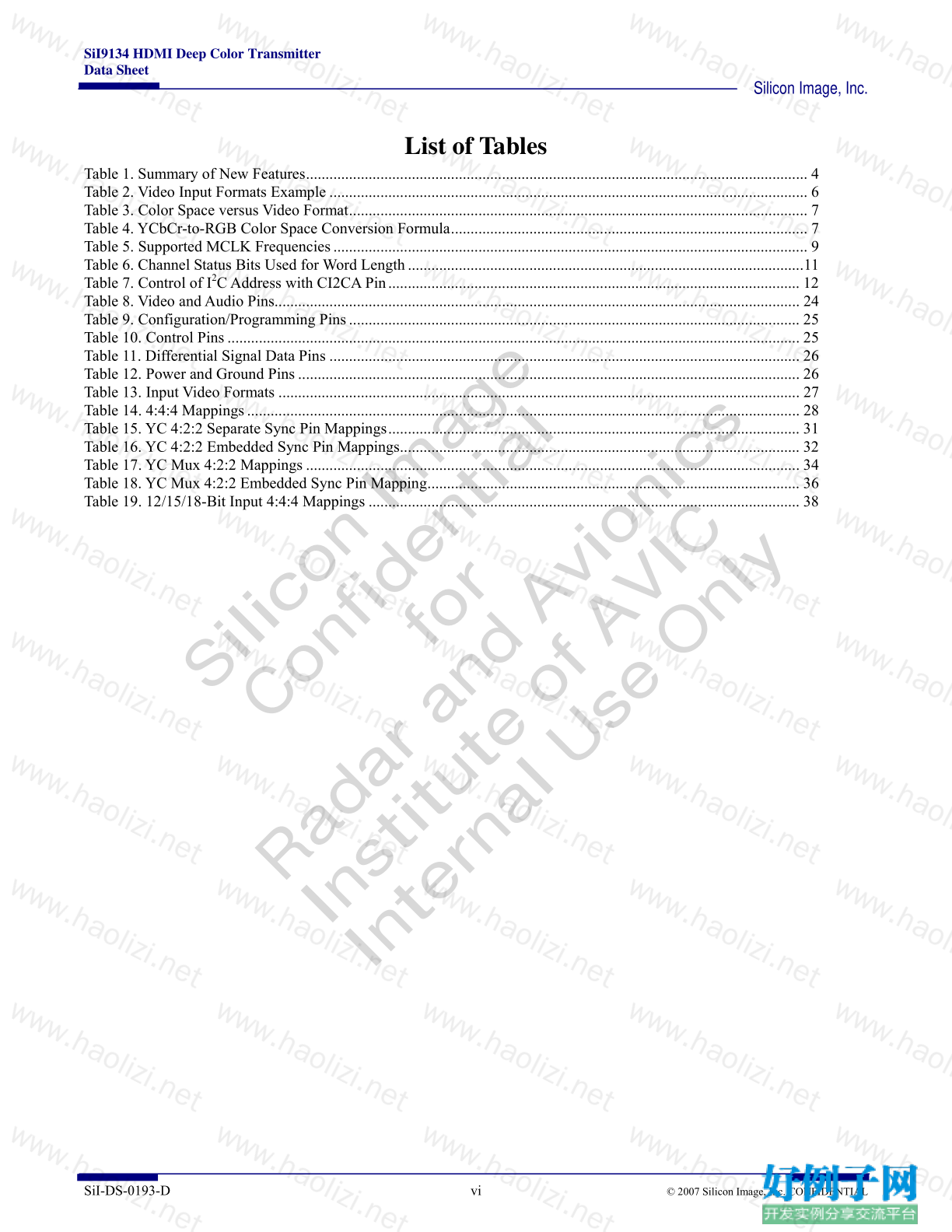

List of Tables

Table 1. Summary of New Features................................................................................................................................ 4

Table 2. Video Input Formats Example .......................................................................................................................... 6

Table 3. Color Space versus Video Format..................................................................................................................... 7

Table 4. YCbCr-to-RGB Color Space Conversion Formula........................................................................................... 7

Table 5. Supported MCLK Frequencies......................................................................................................................... 9

Table 6. Channel Status Bits Used for Word Length.....................................................................................................11

Table 7. Control of I 2 C Address with CI2CA Pin......................................................................................................... 12

Table 8. Video and Audio Pins...................................................................................................................................... 24

Table 9. Configuration/Programming Pins................................................................................................................... 25

Table 10. Control Pins .................................................................................................................................................. 25

Table 11. Differential Signal Data Pins ........................................................................................................................ 26

Table 12. Power and Ground Pins................................................................................................................................ 26

Table 13. Input Video Formats ..................................................................................................................................... 27

Table 14. 4:4:4 Mappings............................................................................................................................................. 28

Table 15. YC 4:2:2 Separate Sync Pin Mappings......................................................................................................... 31

Table 16. YC 4:2:2 Embedded Sync Pin Mappings...................................................................................................... 32

Table 17. YC Mux 4:2:2 Mappings.............................................................................................................................. 34

Table 18. YC Mux 4:2:2 Embedded Sync Pin Mapping............................................................................................... 36

Table 19. 12/15/18-Bit Input 4:4:4 Mappings .............................................................................................................. 38

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论