实例介绍

【实例截图】

【核心代码】

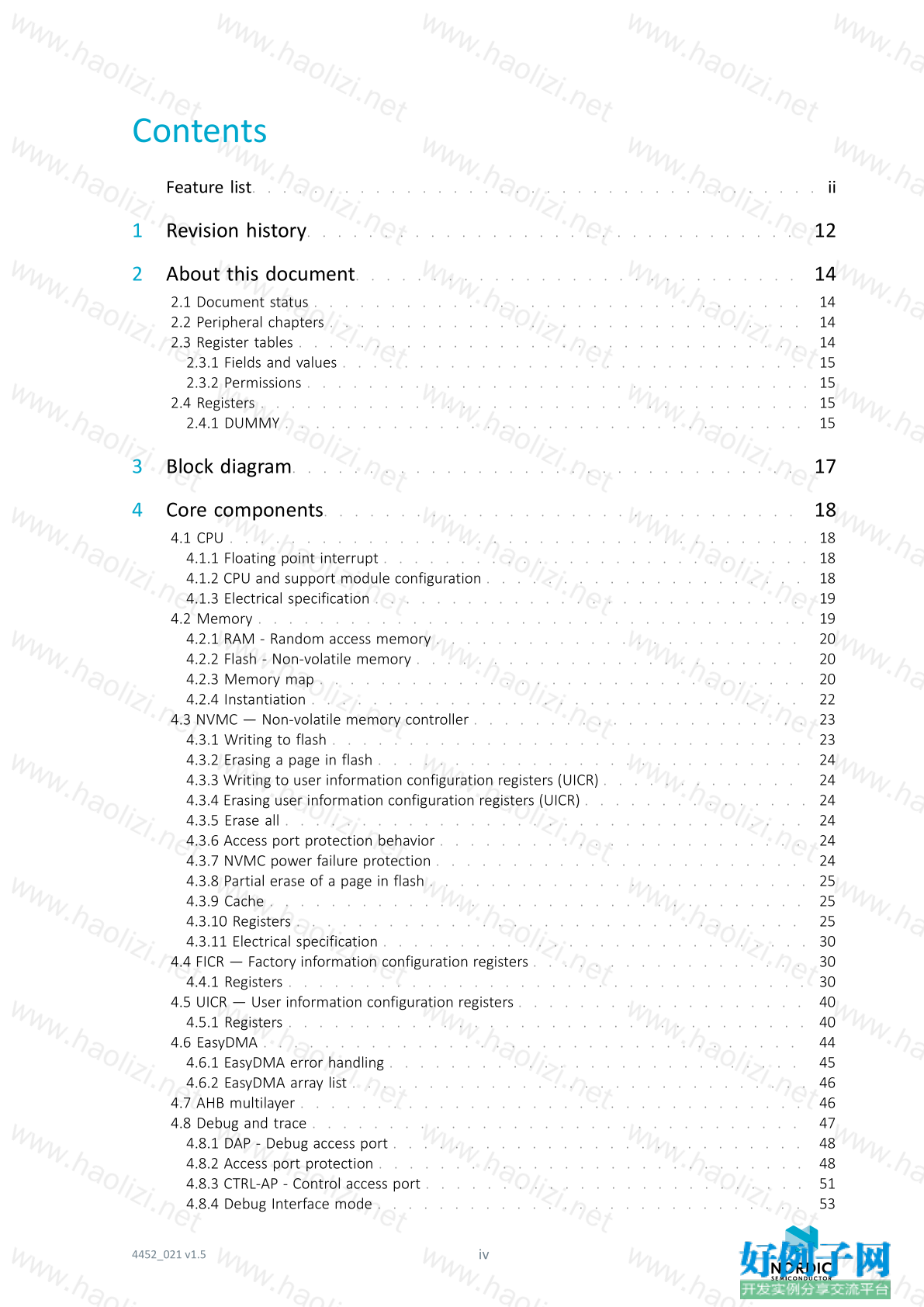

Contents

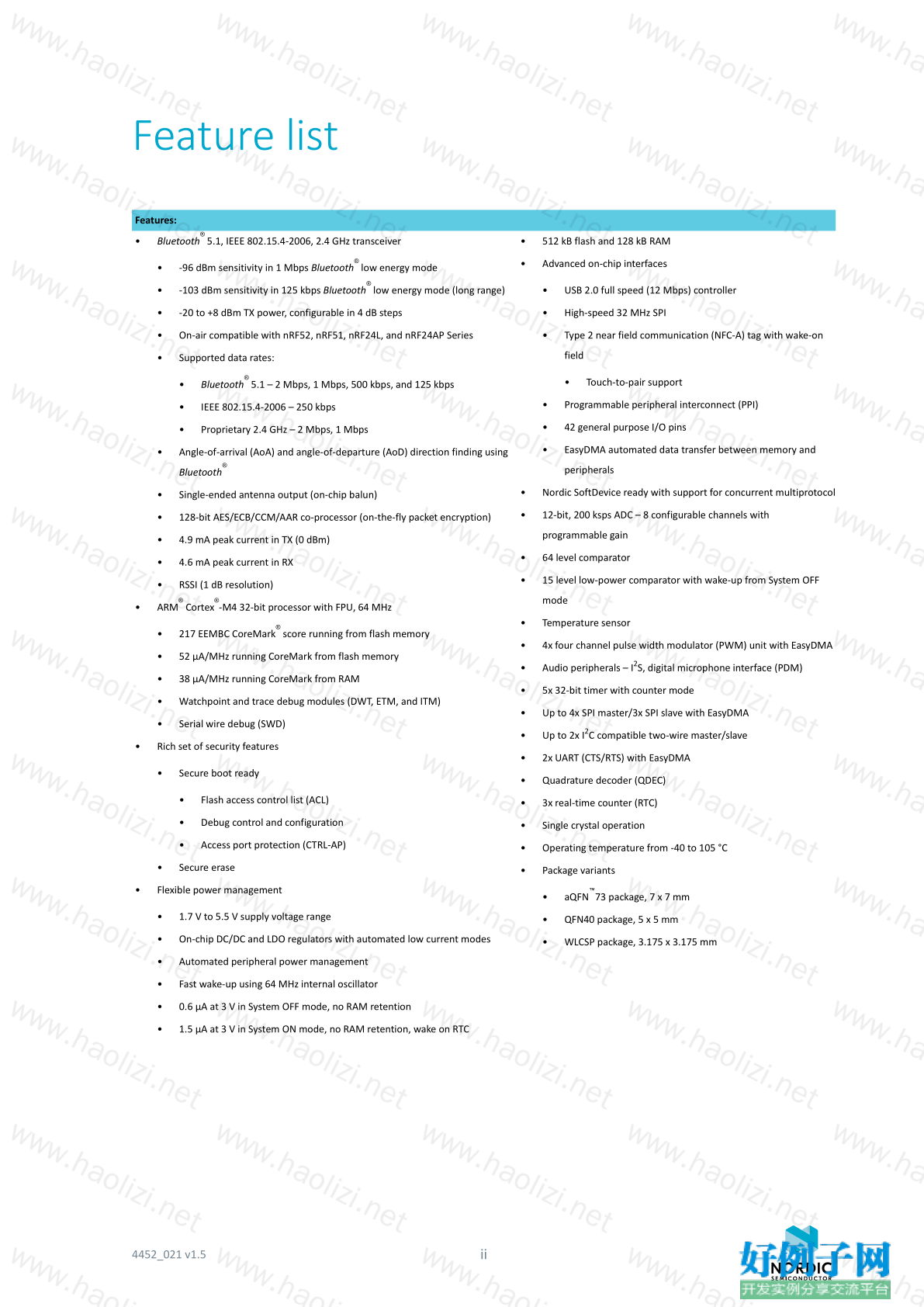

Feature list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ii

1 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2 About this document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.1 Document status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.2 Peripheral chapters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.3 Register tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.3.1 Fields and values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.2 Permissions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.4.1 DUMMY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4 Core components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.1 CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.1.1 Floating point interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.1.2 CPU and support module configuration . . . . . . . . . . . . . . . . . . . . . 18

4.1.3 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.2 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.2.1 RAM - Random access memory . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2.2 Flash - Non-volatile memory . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2.3 Memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2.4 Instantiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.3 NVMC — Non-volatile memory controller . . . . . . . . . . . . . . . . . . . . . . 23

4.3.1 Writing to flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.3.2 Erasing a page in flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.3.3 Writing to user information configuration registers (UICR) . . . . . . . . . . . . . 24

4.3.4 Erasing user information configuration registers (UICR) . . . . . . . . . . . . . . . 24

4.3.5 Erase all . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

4.3.6 Access port protection behavior . . . . . . . . . . . . . . . . . . . . . . . . 24

4.3.7 NVMC power failure protection . . . . . . . . . . . . . . . . . . . . . . . . 24

4.3.8 Partial erase of a page in flash . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.3.9 Cache . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.3.10 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.3.11 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

4.4 FICR — Factory information configuration registers . . . . . . . . . . . . . . . . . . 30

4.4.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

4.5 UICR — User information configuration registers . . . . . . . . . . . . . . . . . . . 40

4.5.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

4.6 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

4.6.1 EasyDMA error handling . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.6.2 EasyDMA array list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

4.7 AHB multilayer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

4.8 Debug and trace . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.8.1 DAP - Debug access port . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4.8.2 Access port protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4.8.3 CTRL-AP - Control access port . . . . . . . . . . . . . . . . . . . . . . . . . 51

4.8.4 Debug Interface mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4452_021 v1.5 iv

4.8.5 Real-time debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.8.6 Trace . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

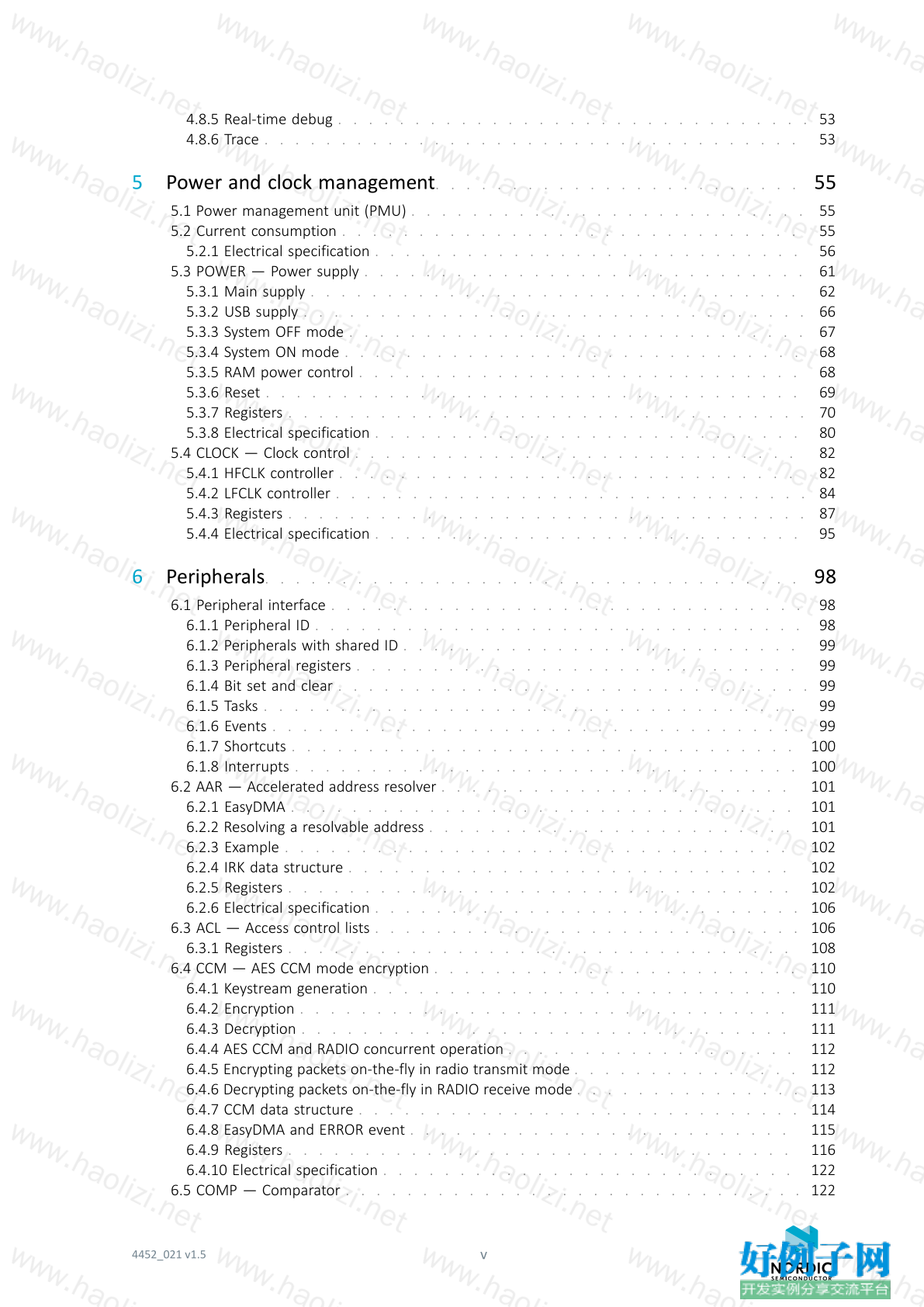

5 Power and clock management . . . . . . . . . . . . . . . . . . . . . . . . 55

5.1 Power management unit (PMU) . . . . . . . . . . . . . . . . . . . . . . . . . . 55

5.2 Current consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

5.2.1 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

5.3 POWER — Power supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5.3.1 Main supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

5.3.2 USB supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

5.3.3 System OFF mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

5.3.4 System ON mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

5.3.5 RAM power control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

5.3.6 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

5.3.7 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.3.8 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

5.4 CLOCK — Clock control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.4.1 HFCLK controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.4.2 LFCLK controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.4.3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.4.4 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

6 Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.1 Peripheral interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.1.1 Peripheral ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

6.1.2 Peripherals with shared ID . . . . . . . . . . . . . . . . . . . . . . . . . . 99

6.1.3 Peripheral registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

6.1.4 Bit set and clear . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

6.1.5 Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

6.1.6 Events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

6.1.7 Shortcuts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

6.1.8 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

6.2 AAR — Accelerated address resolver . . . . . . . . . . . . . . . . . . . . . . . 101

6.2.1 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

6.2.2 Resolving a resolvable address . . . . . . . . . . . . . . . . . . . . . . . . 101

6.2.3 Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

6.2.4 IRK data structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

6.2.5 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

6.2.6 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

6.3 ACL — Access control lists . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

6.3.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

6.4 CCM — AES CCM mode encryption . . . . . . . . . . . . . . . . . . . . . . . . 110

6.4.1 Keystream generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

6.4.2 Encryption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

6.4.3 Decryption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

6.4.4 AES CCM and RADIO concurrent operation . . . . . . . . . . . . . . . . . . . 112

6.4.5 Encrypting packets on-the-fly in radio transmit mode . . . . . . . . . . . . . . . 112

6.4.6 Decrypting packets on-the-fly in RADIO receive mode . . . . . . . . . . . . . . . 113

6.4.7 CCM data structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

6.4.8 EasyDMA and ERROR event . . . . . . . . . . . . . . . . . . . . . . . . . 115

6.4.9 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

6.4.10 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

6.5 COMP — Comparator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

4452_021 v1.5 v

6.5.1 Shared resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

6.5.2 Differential mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

6.5.3 Single-ended mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

6.5.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

6.5.5 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

6.6 ECB — AES electronic codebook mode encryption . . . . . . . . . . . . . . . . . . 134

6.6.1 Shared resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

6.6.2 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

6.6.3 ECB data structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

6.6.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

6.6.5 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

6.7 EGU — Event generator unit . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

6.7.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

6.7.2 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

6.8 GPIO — General purpose input/output . . . . . . . . . . . . . . . . . . . . . . 141

6.8.1 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

6.8.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

6.8.3 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6.9 GPIOTE — GPIO tasks and events . . . . . . . . . . . . . . . . . . . . . . . . . 149

6.9.1 Pin events and tasks . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

6.9.2 Port event . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

6.9.3 Tasks and events pin configuration . . . . . . . . . . . . . . . . . . . . . . 151

6.9.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

6.9.5 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

6.10 I 2 S — Inter-IC sound interface . . . . . . . . . . . . . . . . . . . . . . . . . . 155

6.10.1 Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

6.10.2 Transmitting and receiving . . . . . . . . . . . . . . . . . . . . . . . . . 156

6.10.3 Left right clock (LRCK) . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

6.10.4 Serial clock (SCK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

6.10.5 Master clock (MCK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

6.10.6 Width, alignment and format . . . . . . . . . . . . . . . . . . . . . . . . 158

6.10.7 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

6.10.8 Module operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

6.10.9 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

6.10.10 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

6.10.11 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

6.11 LPCOMP — Low-power comparator . . . . . . . . . . . . . . . . . . . . . . . 175

6.11.1 Shared resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

6.11.2 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

6.11.3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

6.11.4 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

6.12 MWU — Memory watch unit . . . . . . . . . . . . . . . . . . . . . . . . . . 183

6.12.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

6.13 NFCT — Near field communication tag . . . . . . . . . . . . . . . . . . . . . . 197

6.13.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

6.13.2 Operating states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

6.13.3 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

6.13.4 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

6.13.5 Frame assembler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

6.13.6 Frame disassembler . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

6.13.7 Frame timing controller . . . . . . . . . . . . . . . . . . . . . . . . . . 204

6.13.8 Collision resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

6.13.9 Antenna interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

6.13.10 NFCT antenna recommendations . . . . . . . . . . . . . . . . . . . . . . 206

4452_021 v1.5 vi

6.13.11 Battery protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

6.13.12 Digital Modulation Signal . . . . . . . . . . . . . . . . . . . . . . . . . 207

6.13.13 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

6.13.14 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

6.13.15 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

6.14 PDM — Pulse density modulation interface . . . . . . . . . . . . . . . . . . . . 227

6.14.1 Master clock generator . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

6.14.2 Module operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

6.14.3 Decimation filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

6.14.4 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

6.14.5 Hardware example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

6.14.6 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

6.14.7 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

6.14.8 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

6.15 PPI — Programmable peripheral interconnect . . . . . . . . . . . . . . . . . . . 238

6.15.1 Pre-programmed channels . . . . . . . . . . . . . . . . . . . . . . . . . 240

6.15.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

6.16 PWM — Pulse width modulation . . . . . . . . . . . . . . . . . . . . . . . . 245

6.16.1 Wave counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

6.16.2 Decoder with EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

6.16.3 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

6.16.4 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

6.16.5 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

6.17 QDEC — Quadrature decoder . . . . . . . . . . . . . . . . . . . . . . . . . . 265

6.17.1 Sampling and decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

6.17.2 LED output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

6.17.3 Debounce filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 267

6.17.4 Accumulators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

6.17.5 Output/input pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

6.17.6 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

6.17.7 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

6.17.8 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

6.18 RADIO — 2.4 GHz radio . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

6.18.1 Packet configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

6.18.2 Address configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

6.18.3 Data whitening . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

6.18.4 CRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

6.18.5 Radio states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

6.18.6 Transmit sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

6.18.7 Receive sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

6.18.8 Received signal strength indicator (RSSI) . . . . . . . . . . . . . . . . . . . . 287

6.18.9 Interframe spacing (IFS) . . . . . . . . . . . . . . . . . . . . . . . . . . 287

6.18.10 Device address match . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

6.18.11 Bit counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

6.18.12 Direction finding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

6.18.13 IEEE 802.15.4 operation . . . . . . . . . . . . . . . . . . . . . . . . . . 294

6.18.14 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

6.18.15 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

6.18.16 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 339

6.19 RNG — Random number generator . . . . . . . . . . . . . . . . . . . . . . . 345

6.19.1 Bias correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

6.19.2 Speed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

6.19.3 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

6.19.4 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 348

4452_021 v1.5 vii

6.20 RTC — Real-time counter . . . . . . . . . . . . . . . . . . . . . . . . . . . 348

6.20.1 Clock source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 348

6.20.2 Resolution versus overflow and the PRESCALER . . . . . . . . . . . . . . . . . 348

6.20.3 COUNTER register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 349

6.20.4 Overflow features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 350

6.20.5 TICK event . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 350

6.20.6 Event control feature . . . . . . . . . . . . . . . . . . . . . . . . . . . 350

6.20.7 Compare feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

6.20.8 TASK and EVENT jitter/delay . . . . . . . . . . . . . . . . . . . . . . . . . 353

6.20.9 Reading the COUNTER register . . . . . . . . . . . . . . . . . . . . . . . 355

6.20.10 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356

6.20.11 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

6.21 SAADC — Successive approximation analog-to-digital converter . . . . . . . . . . . . 361

6.21.1 Input configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

6.21.2 Reference voltage and gain settings . . . . . . . . . . . . . . . . . . . . . 364

6.21.3 Digital output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 364

6.21.4 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 364

6.21.5 Continuous sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

6.21.6 Oversampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

6.21.7 Event monitoring using limits . . . . . . . . . . . . . . . . . . . . . . . . 366

6.21.8 Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

6.21.9 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

6.21.10 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 382

6.22 SPI — Serial peripheral interface master . . . . . . . . . . . . . . . . . . . . . 383

6.22.1 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

6.22.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 386

6.22.3 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 390

6.23 SPIM — Serial peripheral interface master with EasyDMA . . . . . . . . . . . . . . 391

6.23.1 SPI master transaction sequence . . . . . . . . . . . . . . . . . . . . . . . 392

6.23.2 D/CX functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 393

6.23.3 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

6.23.4 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

6.23.5 Low power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

6.23.6 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 396

6.23.7 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 407

6.24 SPIS — Serial peripheral interface slave with EasyDMA . . . . . . . . . . . . . . . . 408

6.24.1 Shared resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 409

6.24.2 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 409

6.24.3 SPI slave operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 409

6.24.4 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 411

6.24.5 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 412

6.24.6 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 423

6.25 SWI — Software interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

6.25.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

6.26 TEMP — Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . 425

6.26.1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

6.26.2 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 431

6.27 TWI — I 2 C compatible two-wire interface . . . . . . . . . . . . . . . . . . . . . 432

6.27.1 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . 432

6.27.2 Master mode pin configuration . . . . . . . . . . . . . . . . . . . . . . . 432

6.27.3 Shared resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

6.27.4 Master write sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

6.27.5 Master read sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . 434

6.27.6 Master repeated start sequence . . . . . . . . . . . . . . . . . . . . . . . 435

4452_021 v1.5 viii

6.27.7 Low power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

6.27.8 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

6.27.9 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

6.28 TIMER — Timer/counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . 444

6.28.1 Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 446

6.28.2 Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 446

6.28.3 Task delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 446

6.28.4 Task priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 446

6.28.5 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 446

6.28.6 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 451

6.29 TWIM — I 2 C compatible two-wire interface master with EasyDMA . . . . . . . . . . . 451

6.29.1 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 453

6.29.2 Master write sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . 453

6.29.3 Master read sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . 454

6.29.4 Master repeated start sequence . . . . . . . . . . . . . . . . . . . . . . . 455

6.29.5 Low power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 456

6.29.6 Master mode pin configuration . . . . . . . . . . . . . . . . . . . . . . . 456

6.29.7 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 456

6.29.8 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 467

6.29.9 Pullup resistor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 468

6.30 TWIS — I 2 C compatible two-wire interface slave with EasyDMA . . . . . . . . . . . . 468

6.30.1 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 470

6.30.2 TWI slave responding to a read command . . . . . . . . . . . . . . . . . . . 470

6.30.3 TWI slave responding to a write command . . . . . . . . . . . . . . . . . . . 472

6.30.4 Master repeated start sequence . . . . . . . . . . . . . . . . . . . . . . . 473

6.30.5 Terminating an ongoing TWI transaction . . . . . . . . . . . . . . . . . . . . 473

6.30.6 Low power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 474

6.30.7 Slave mode pin configuration . . . . . . . . . . . . . . . . . . . . . . . . 474

6.30.8 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 474

6.30.9 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 484

6.31 UART — Universal asynchronous receiver/transmitter . . . . . . . . . . . . . . . . 485

6.31.1 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . 485

6.31.2 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486

6.31.3 Shared resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486

6.31.4 Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486

6.31.5 Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 487

6.31.6 Suspending the UART . . . . . . . . . . . . . . . . . . . . . . . . . . . 488

6.31.7 Error conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 488

6.31.8 Using the UART without flow control . . . . . . . . . . . . . . . . . . . . . 488

6.31.9 Parity and stop bit configuration . . . . . . . . . . . . . . . . . . . . . . . 488

6.31.10 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 488

6.31.11 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 497

6.32 UARTE — Universal asynchronous receiver/transmitter with EasyDMA . . . . . . . . . 498

6.32.1 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 498

6.32.2 Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 499

6.32.3 Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 499

6.32.4 Error conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 501

6.32.5 Using the UARTE without flow control . . . . . . . . . . . . . . . . . . . . 501

6.32.6 Parity and stop bit configuration . . . . . . . . . . . . . . . . . . . . . . . 501

6.32.7 Low power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 501

6.32.8 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

6.32.9 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

6.32.10 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 515

6.33 USBD — Universal serial bus device . . . . . . . . . . . . . . . . . . . . . . . 515

4452_021 v1.5 ix

6.33.1 USB device states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 516

6.33.2 USB terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 517

6.33.3 USB pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 518

6.33.4 USBD power-up sequence . . . . . . . . . . . . . . . . . . . . . . . . . 518

6.33.5 USB pull-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 519

6.33.6 USB reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 519

6.33.7 USB suspend and resume . . . . . . . . . . . . . . . . . . . . . . . . . . 520

6.33.8 EasyDMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 521

6.33.9 Control transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 522

6.33.10 Bulk and interrupt transactions . . . . . . . . . . . . . . . . . . . . . . . 525

6.33.11 Isochronous transactions . . . . . . . . . . . . . . . . . . . . . . . . . 527

6.33.12 USB register access limitations . . . . . . . . . . . . . . . . . . . . . . . 530

6.33.13 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 530

6.33.14 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 555

6.34 WDT — Watchdog timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . 555

6.34.1 Reload criteria . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 556

6.34.2 Temporarily pausing the watchdog . . . . . . . . . . . . . . . . . . . . . . 556

6.34.3 Watchdog reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 556

6.34.4 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 556

6.34.5 Electrical specification . . . . . . . . . . . . . . . . . . . . . . . . . . . 559

7 Hardware and layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 560

7.1 Pin assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 560

7.1.1 aQFN73 ball assignments . . . . . . . . . . . . . . . . . . . . . . . . . . 560

7.1.2 QFN40 pin assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . 563

7.1.3 WLCSP ball assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . 565

7.2 Mechanical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . 568

7.2.1 aQFN73 7 x 7 mm package . . . . . . . . . . . . . . . . . . . . . . . . . 568

7.2.2 QFN40 5 x 5 mm package . . . . . . . . . . . . . . . . . . . . . . . . . . 569

7.2.3 WLCSP 3.175 x 3.175 mm package . . . . . . . . . . . . . . . . . . . . . . 569

7.3 Reference circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 570

7.3.1 Circuit configuration no. 1 for QIAA aQFN73 . . . . . . . . . . . . . . . . . . 572

7.3.2 Circuit configuration no. 2 for QIAA aQFN73 . . . . . . . . . . . . . . . . . . 573

7.3.3 Circuit configuration no. 3 for QIAA aQFN73 . . . . . . . . . . . . . . . . . . 575

7.3.4 Circuit configuration no. 4 for QIAA aQFN73 . . . . . . . . . . . . . . . . . . 577

7.3.5 Circuit configuration no. 5 for QIAA aQFN73 . . . . . . . . . . . . . . . . . . 579

7.3.6 Circuit configuration no. 6 for QIAA aQFN73 . . . . . . . . . . . . . . . . . . 581

7.3.7 Circuit configuration no. 1 for QDAA QFN40 . . . . . . . . . . . . . . . . . . . 583

7.3.8 Circuit configuration no. 2 for QDAA QFN40 . . . . . . . . . . . . . . . . . . . 585

7.3.9 Circuit configuration no. 3 for QDAA QFN40 . . . . . . . . . . . . . . . . . . . 587

7.3.10 Circuit configuration no. 4 for QDAA QFN40 . . . . . . . . . . . . . . . . . . 589

7.3.11 Circuit configuration no. 5 for QDAA QFN40 . . . . . . . . . . . . . . . . . . 591

7.3.12 Circuit configuration no. 6 for QDAA QFN40 . . . . . . . . . . . . . . . . . . 593

7.3.13 Circuit configuration no. 1 for CJAA WLCSP . . . . . . . . . . . . . . . . . . 595

7.3.14 Circuit configuration no. 2 for CJAA WLCSP . . . . . . . . . . . . . . . . . . 597

7.3.15 Circuit configuration no. 3 for CJAA WLCSP . . . . . . . . . . . . . . . . . . 599

7.3.16 Circuit configuration no. 4 for CJAA WLCSP . . . . . . . . . . . . . . . . . . 601

7.3.17 Circuit configuration no. 5 for CJAA WLCSP . . . . . . . . . . . . . . . . . . 603

7.3.18 Circuit configuration no. 6 for CJAA WLCSP . . . . . . . . . . . . . . . . . . 605

7.3.19 PCB guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 607

7.3.20 PCB layout example . . . . . . . . . . . . . . . . . . . . . . . . . . . . 608

7.4 Package thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . 610

7.5 Package Variation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 610

7.5.1 aQFN73 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 610

4452_021 v1.5 x

8 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . 611

8.1 Extended Operating Temperature . . . . . . . . . . . . . . . . . . . . . . . . . 611

8.2 WLCSP light sensitivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 611

9 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . 612

10 Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . 614

10.1 Device marking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 614

10.2 Box labels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 614

10.3 Order code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 615

10.4 Code ranges and values . . . . . . . . . . . . . . . . . . . . . . . . . . . . 616

10.5 Product options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 617

11 Legal notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 619

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论