实例介绍

【实例简介】IntelCPU使用手册

CPU使用手册英文原版

【实例截图】

【核心代码】

CONTENTS

PAGE

CHAPTER 1

ABOUT THIS MANUAL

1.1 IA-32 PROCESSORS COVERED IN THIS MANUAL . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2 OVERVIEW OF VOLUME 1: BASIC ARCHITECTURE. . . . . . . . . . . . . . . . . . . . . . 1-1

1.3 NOTATIONAL CONVENTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.3.1 Bit and Byte Order. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

1.3.2 Reserved Bits and Software Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

1.3.3 Instruction Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

1.3.4 Hexadecimal and Binary Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

1.3.5 Segmented Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

1.3.6 A New Syntax for CPUID, CR, and MSR Values . . . . . . . . . . . . . . . . . . . . . . . . .1-6

1.3.7 Exceptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-7

1.4 RELATED LITERATURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

CHAPTER 2

IA-32 INTEL® ARCHITECTURE

2.1 BRIEF HISTORY OF THE IA-32 ARCHITECTURE. . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1.1 16-bit Processors and Segmentation (1978). . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.1.2 The Intel® 286 Processor (1982). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

2.1.3 The Intel386™ Processor (1985) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

2.1.4 The Intel486™ Processor (1989) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

2.1.5 The Intel® Pentium® Processor (1993) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.1.6 The P6 Family of Processors (1995-1999) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.1.7 The Intel® Pentium® 4 Processor Family (2000-Current) . . . . . . . . . . . . . . . . . . .2-4

2.1.8 The Intel® Xeon® Processor (2001-Current) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.1.9 The Intel® Pentium® M Processor (2003-Current) . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.1.10 The Intel® Pentium® Processor Extreme Edition (2005-Current) . . . . . . . . . . . . .2-5

2.1.11 The Intel® Core™ Duo and Intel® Core™ Solo

Processors (2006-Current) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.2 MORE ON SPECIFIC ADVANCES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.2.1 P6 Family Microarchitecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.2.2 Intel NetBurst® Microarchitecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.2.2.1 The Front End Pipeline. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.2.2.2 Out-Of-Order Execution Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.2.2.3 Retirement Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.2.3 SIMD Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

2.2.4 Hyper-Threading Technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

2.2.4.1 Some Implementation Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-15

2.2.5 Multi-Core Technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-16

2.2.6 Intel® Extended Memory 64 Technology. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-16

2.2.7 Intel® Virtualization Technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-17

2.3 IA-32 PROCESSOR GENERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

CHAPTER 3

BASIC EXECUTION ENVIRONMENT

3.1 MODES OF OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1.1 IA-32e Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2

3.2 OVERVIEW OF THE BASIC EXECUTION ENVIRONMENT . . . . . . . . . . . . . . . . . 3-3

Vol. 1 iiiCONTENTS

PAGE

3.2.1 64-Bit Mode Execution Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

3.3 MEMORY ORGANIZATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.3.1 Three Memory Models. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-8

3.3.2 Paging and Virtual Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-9

3.3.3 Memory Organization in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.3.4 Modes of Operation vs. Memory Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.3.5 32-Bit and 16-Bit Address and Operand Sizes . . . . . . . . . . . . . . . . . . . . . . . . . .3-11

3.3.6 Extended Physical Addressing in Protected Mode . . . . . . . . . . . . . . . . . . . . . . .3-11

3.3.7 Address Calculations in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.3.7.1 Canonical Addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.4 BASIC PROGRAM EXECUTION REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

3.4.1 General-Purpose Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

3.4.1.1 General-Purpose Registers in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . .3-15

3.4.2 Segment Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-16

3.4.2.1 Segment Registers in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-19

3.4.3 EFLAGS Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-20

3.4.3.1 Status Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-21

3.4.3.2 DF Flag. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-22

3.4.3.3 System Flags and IOPL Field. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-23

3.4.3.4 RFLAGS Register in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-23

3.5 INSTRUCTION POINTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-24

3.5.1 Instruction Pointer in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-24

3.6 OPERAND-SIZE AND ADDRESS-SIZE ATTRIBUTES. . . . . . . . . . . . . . . . . . . . . 3-24

3.6.1 Operand Size and Address Size in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . .3-25

3.7 OPERAND ADDRESSING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-26

3.7.1 Immediate Operands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-26

3.7.2 Register Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-27

3.7.2.1 Register Operands in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-28

3.7.3 Memory Operands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-28

3.7.3.1 Memory Operands in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-29

3.7.4 Specifying a Segment Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-29

3.7.4.1 Segmentation in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-30

3.7.5 Specifying an Offset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-30

3.7.5.1 Specifying an Offset in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-32

3.7.6 Assembler and Compiler Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . .3-33

3.7.7 I/O Port Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-33

CHAPTER 4

DATA TYPES

4.1 FUNDAMENTAL DATA TYPES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.1 Alignment of Words, Doublewords, Quadwords, and Double Quadwords . . . . . .4-2

4.2 NUMERIC DATA TYPES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.2.1 Integers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.2.1.1 Unsigned Integers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.2.1.2 Signed Integers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.2.2 Floating-Point Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

4.3 POINTER DATA TYPES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.3.1 Pointer Data Types in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

4.4 BIT FIELD DATA TYPE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.5 STRING DATA TYPES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.6 PACKED SIMD DATA TYPES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.6.1 64-Bit SIMD Packed Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-9

iv Vol. 1CONTENTS

PAGE

4.6.2 128-Bit Packed SIMD Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

4.7 BCD AND PACKED BCD INTEGERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

4.8 REAL NUMBERS AND FLOATING-POINT FORMATS. . . . . . . . . . . . . . . . . . . . . 4-12

4.8.1 Real Number System. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

4.8.2 Floating-Point Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-13

4.8.2.1 Normalized Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4.8.2.2 Biased Exponent. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4.8.3 Real Number and Non-number Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

4.8.3.1 Signed Zeros. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

4.8.3.2 Normalized and Denormalized Finite Numbers . . . . . . . . . . . . . . . . . . . . . . 4-17

4.8.3.3 Signed Infinities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

4.8.3.4 NaNs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

4.8.3.5 Operating on SNaNs and QNaNs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

4.8.3.6 Using SNaNs and QNaNs in Applications . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

4.8.3.7 QNaN Floating-Point Indefinite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

4.8.4 Rounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

4.8.4.1 Rounding Control (RC) Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-22

4.8.4.2 Truncation with SSE and SSE2 Conversion Instructions . . . . . . . . . . . . . . . 4-22

4.9 OVERVIEW OF FLOATING-POINT EXCEPTIONS. . . . . . . . . . . . . . . . . . . . . . . . 4-22

4.9.1 Floating-Point Exception Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

4.9.1.1 Invalid Operation Exception (#I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

4.9.1.2 Denormal Operand Exception (#D). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

4.9.1.3 Divide-By-Zero Exception (#Z) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

4.9.1.4 Numeric Overflow Exception (#O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

4.9.1.5 Numeric Underflow Exception (#U). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

4.9.1.6 Inexact-Result (Precision) Exception (#P) . . . . . . . . . . . . . . . . . . . . . . . . . . 4-27

4.9.2 Floating-Point Exception Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

4.9.3 Typical Actions of a Floating-Point Exception Handler . . . . . . . . . . . . . . . . . . . 4-29

CHAPTER 5

INSTRUCTION SET SUMMARY

5.1 GENERAL-PURPOSE INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.1.1 Data Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.1.2 Binary Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.1.3 Decimal Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.1.4 Logical Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.1.5 Shift and Rotate Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.1.6 Bit and Byte Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.1.7 Control Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5.1.8 String Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.1.9 I/O Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

5.1.10 Enter and Leave Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

5.1.11 Flag Control (EFLAG) Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

5.1.12 Segment Register Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5.1.13 Miscellaneous Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5.2 X87 FPU INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5.2.1 x87 FPU Data Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

5.2.2 x87 FPU Basic Arithmetic Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

5.2.3 x87 FPU Comparison Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

5.2.4 x87 FPU Transcendental Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5.2.5 x87 FPU Load Constants Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5.2.6 x87 FPU Control Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

Vol. 1 vCONTENTS

PAGE

5.3 X87 FPU AND SIMD STATE MANAGEMENT INSTRUCTIONS. . . . . . . . . . . . . . 5-13

5.4 MMX™ INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

5.4.1 MMX Data Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.4.2 MMX Conversion Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.4.3 MMX Packed Arithmetic Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-15

5.4.4 MMX Comparison Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-15

5.4.5 MMX Logical Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.4.6 MMX Shift and Rotate Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.4.7 MMX State Management Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.5 SSE INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

5.5.1 SSE SIMD Single-Precision Floating-Point Instructions . . . . . . . . . . . . . . . . . . .5-17

5.5.1.1 SSE Data Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-17

5.5.1.2 SSE Packed Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-18

5.5.1.3 SSE Comparison Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19

5.5.1.4 SSE Logical Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19

5.5.1.5 SSE Shuffle and Unpack Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19

5.5.1.6 SSE Conversion Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19

5.5.2 SSE MXCSR State Management Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . .5-20

5.5.3 SSE 64-Bit SIMD Integer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-20

5.5.4 SSE Cacheability Control, Prefetch, and Instruction Ordering Instructions. . . . .5-21

5.6 SSE2 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

5.6.1 SSE2 Packed and Scalar Double-Precision Floating-Point Instructions . . . . . . .5-22

5.6.1.1 SSE2 Data Movement Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-22

5.6.1.2 SSE2 Packed Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-22

5.6.1.3 SSE2 Logical Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.6.1.4 SSE2 Compare Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.6.1.5 SSE2 Shuffle and Unpack Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

5.6.1.6 SSE2 Conversion Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24

5.6.2 SSE2 Packed Single-Precision Floating-Point Instructions. . . . . . . . . . . . . . . . .5-25

5.6.3 SSE2 128-Bit SIMD Integer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25

5.6.4 SSE2 Cacheability Control and Ordering Instructions. . . . . . . . . . . . . . . . . . . . .5-26

5.7 SSE3 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

5.7.1 SSE3 x87-FP Integer Conversion Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

5.7.2 SSE3 Specialized 128-bit Unaligned Data Load Instruction . . . . . . . . . . . . . . . .5-27

5.7.3 SSE3 SIMD Floating-Point Packed ADD/SUB Instructions. . . . . . . . . . . . . . . . .5-27

5.7.4 SSE3 SIMD Floating-Point Horizontal ADD/SUB Instructions. . . . . . . . . . . . . . .5-27

5.7.5 SSE3 SIMD Floating-Point LOAD/MOVE/DUPLICATE Instructions . . . . . . . . . .5-28

5.7.6 SSE3 Agent Synchronization Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

5.8 SYSTEM INSTRUCTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28

5.9 64-BIT MODE INSTRUCTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-29

5.10 VIRTUAL-MACHINE EXTENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

CHAPTER 6

PROCEDURE CALLS, INTERRUPTS, AND EXCEPTIONS

6.1 PROCEDURE CALL TYPES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.2 STACKS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.2.1 Setting Up a Stack. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-2

6.2.2 Stack Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.2.3 Address-Size Attributes for Stack Accesses . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.2.4 Procedure Linking Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.2.4.1 Stack-Frame Base Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

6.2.4.2 Return Instruction Pointer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

vi Vol. 1CONTENTS

PAGE

6.2.5 Stack Behavior in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.3 CALLING PROCEDURES USING CALL AND RET. . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.3.1 Near CALL and RET Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.3.2 Far CALL and RET Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.3.3 Parameter Passing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3.3.1 Passing Parameters Through the General-Purpose Registers. . . . . . . . . . . . 6-7

6.3.3.2 Passing Parameters on the Stack. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3.3.3 Passing Parameters in an Argument List . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3.4 Saving Procedure State Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3.5 Calls to Other Privilege Levels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6.3.6 CALL and RET Operation Between Privilege Levels. . . . . . . . . . . . . . . . . . . . . . 6-9

6.3.7 Branch Functions in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.4 INTERRUPTS AND EXCEPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-12

6.4.1 Call and Return Operation for Interrupt or Exception Handling Procedures . . . 6-13

6.4.2 Calls to Interrupt or Exception Handler Tasks . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6.4.3 Interrupt and Exception Handling in Real-Address Mode . . . . . . . . . . . . . . . . . 6-17

6.4.4 INT n, INTO, INT 3, and BOUND Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6.4.5 Handling Floating-Point Exceptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-18

6.4.6 Interrupt and Exception Behavior in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . 6-18

6.5 PROCEDURE CALLS FOR BLOCK-STRUCTURED LANGUAGES . . . . . . . . . . . 6-19

6.5.1 ENTER Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

6.5.2 LEAVE Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

CHAPTER 7

PROGRAMMING WITH GENERAL-PURPOSE INSTRUCTIONS

7.1 PROGRAMMING ENVIRONMENT FOR GP INSTRUCTIONS . . . . . . . . . . . . . . . . 7-1

7.2 PROGRAMMING ENVIRONMENT FOR GP INSTRUCTIONS IN 64-BIT MODE . . 7-2

7.3 SUMMARY OF GP INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.3.1 Data Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.3.1.1 General Data Movement Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.3.1.2 Exchange Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7.3.1.3 Exchange Instructions in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.3.1.4 Stack Manipulation Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.3.1.5 Stack Manipulation Instructions in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.3.1.6 Type Conversion Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.3.1.7 Type Conversion Instructions in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7.3.2 Binary Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7.3.2.1 Addition and Subtraction Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7.3.2.2 Increment and Decrement Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7.3.2.3 Increment and Decrement Instructions in 64-Bit Mode. . . . . . . . . . . . . . . . . 7-11

7.3.2.4 Comparison and Sign Change Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7.3.2.5 Multiplication and Divide Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-11

7.3.3 Decimal Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.3.3.1 Packed BCD Adjustment Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.3.3.2 Unpacked BCD Adjustment Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7.3.4 Decimal Arithmetic Instructions in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7.3.5 Logical Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7.3.6 Shift and Rotate Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7.3.6.1 Shift Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

7.3.6.2 Double-Shift Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

7.3.6.3 Rotate Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-17

7.3.7 Bit and Byte Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

Vol. 1 viiCONTENTS

PAGE

7.3.7.1 Bit Test and Modify Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-19

7.3.7.2 Bit Scan Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-19

7.3.7.3 Byte Set on Condition Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-19

7.3.7.4 Test Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-19

7.3.8 Control Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-20

7.3.8.1 Unconditional Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-20

7.3.8.2 Conditional Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-21

7.3.8.3 Control Transfer Instructions in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . .7-24

7.3.8.4 Software Interrupt Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-24

7.3.8.5 Software Interrupt Instructions in 64-bit Mode and Compatibility Mode . . . . .7-25

7.3.9 String Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-25

7.3.9.1 Repeating String Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-26

7.3.10 String Operations in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-27

7.3.10.1 Repeating String Operations in 64-bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . .7-27

7.3.11 I/O Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-27

7.3.12 I/O Instructions in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-27

7.3.13 Enter and Leave Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-28

7.3.14 Flag Control (EFLAG) Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-28

7.3.14.1 Carry and Direction Flag Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-28

7.3.14.2 EFLAGS Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-28

7.3.14.3 Interrupt Flag Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-29

7.3.15 Flag Control (RFLAG) Instructions in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . .7-29

7.3.16 Segment Register Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-30

7.3.16.1 Segment-Register Load and Store Instructions . . . . . . . . . . . . . . . . . . . . . . .7-30

7.3.16.2 Far Control Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-30

7.3.16.3 Software Interrupt Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-31

7.3.16.4 Load Far Pointer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-31

7.3.17 Miscellaneous Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-31

7.3.17.1 Address Computation Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-31

7.3.17.2 Table Lookup Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-31

7.3.17.3 Processor Identification Instruction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-32

7.3.17.4 No-Operation and Undefined Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . .7-32

CHAPTER 8

PROGRAMMING WITH THE X87 FPU

8.1 X87 FPU EXECUTION ENVIRONMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

8.1.1 x87 FPU in 64-Bit Mode and Compatibility Mode . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.1.2 x87 FPU Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.1.2.1 Parameter Passing With the x87 FPU Register Stack . . . . . . . . . . . . . . . . . . .8-5

8.1.3 x87 FPU Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-6

8.1.3.1 Top of Stack (TOP) Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-6

8.1.3.2 Condition Code Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-6

8.1.3.3 x87 FPU Floating-Point Exception Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-7

8.1.3.4 Stack Fault Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-8

8.1.4 Branching and Conditional Moves on Condition Codes . . . . . . . . . . . . . . . . . . . .8-9

8.1.5 x87 FPU Control Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-10

8.1.5.1 x87 FPU Floating-Point Exception Mask Bits . . . . . . . . . . . . . . . . . . . . . . . . .8-11

8.1.5.2 Precision Control Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-11

8.1.5.3 Rounding Control Field. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-11

8.1.6 Infinity Control Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-12

8.1.7 x87 FPU Tag Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-12

8.1.8 x87 FPU Instruction and Data (Operand) Pointers . . . . . . . . . . . . . . . . . . . . . . .8-13

viii Vol. 1CONTENTS

PAGE

8.1.9 Last Instruction Opcode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-13

8.1.9.1 Fopcode Compatibility Sub-mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-14

8.1.10 Saving the x87 FPU’s State with FSTENV/FNSTENV and FSAVE/FNSAVE . . 8-14

8.1.11 Saving the x87 FPU’s State with FXSAVE . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-16

8.2 X87 FPU DATA TYPES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-16

8.2.1 Indefinites . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-18

8.2.2 Unsupported Double Extended-Precision

Floating-Point Encodings and Pseudo-Denormals . . . . . . . . . . . . . . . . . . . . . . 8-18

8.3 X86 FPU INSTRUCTION SET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-20

8.3.1 Escape (ESC) Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-20

8.3.2 x87 FPU Instruction Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-20

8.3.3 Data Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-21

8.3.4 Load Constant Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-22

8.3.5 Basic Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-23

8.3.6 Comparison and Classification Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-24

8.3.6.1 Branching on the x87 FPU Condition Codes . . . . . . . . . . . . . . . . . . . . . . . . 8-26

8.3.7 Trigonometric Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-27

8.3.8 Pi . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-27

8.3.9 Logarithmic, Exponential, and Scale . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-29

8.3.10 Transcendental Instruction Accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-29

8.3.11 x87 FPU Control Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-30

8.3.12 Waiting vs. Non-waiting Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-31

8.3.13 Unsupported x87 FPU Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-31

8.4 X87 FPU FLOATING-POINT EXCEPTION HANDLING. . . . . . . . . . . . . . . . . . . . . 8-31

8.4.1 Arithmetic vs. Non-arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-32

8.5 X87 FPU FLOATING-POINT EXCEPTION CONDITIONS. . . . . . . . . . . . . . . . . . . 8-34

8.5.1 Invalid Operation Exception. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-34

8.5.1.1 Stack Overflow or Underflow Exception (#IS). . . . . . . . . . . . . . . . . . . . . . . . 8-34

8.5.1.2 Invalid Arithmetic Operand Exception (#IA) . . . . . . . . . . . . . . . . . . . . . . . . . 8-35

8.5.2 Denormal Operand Exception (#D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-37

8.5.3 Divide-By-Zero Exception (#Z) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-37

8.5.4 Numeric Overflow Exception (#O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-38

8.5.5 Numeric Underflow Exception (#U) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-39

8.5.6 Inexact-Result (Precision) Exception (#P) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-40

8.6 X87 FPU EXCEPTION SYNCHRONIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-41

8.7 HANDLING X87 FPU EXCEPTIONS IN SOFTWARE . . . . . . . . . . . . . . . . . . . . . . 8-42

8.7.1 Native Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-42

8.7.2 MS-DOS* Compatibility Sub-mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-43

8.7.3 Handling x87 FPU Exceptions in Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-44

CHAPTER 9

PROGRAMMING WITH INTEL® MMX™ TECHNOLOGY

9.1 OVERVIEW OF MMX TECHNOLOGY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.2 THE MMX TECHNOLOGY PROGRAMMING ENVIRONMENT . . . . . . . . . . . . . . . 9-2

9.2.1 MMX Technology in 64-Bit Mode and Compatibility Mode . . . . . . . . . . . . . . . . . 9-2

9.2.2 MMX Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.2.3 MMX Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.2.4 Memory Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.2.5 Single Instruction, Multiple Data (SIMD) Execution Model . . . . . . . . . . . . . . . . . 9-4

9.3 SATURATION AND WRAPAROUND MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

9.4 MMX INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6

9.4.1 Data Transfer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

Vol. 1 ixCONTENTS

PAGE

9.4.2 Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-8

9.4.3 Comparison Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-8

9.4.4 Conversion Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.4.5 Unpack Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.4.6 Logical Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.4.7 Shift Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.4.8 EMMS Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-10

9.5 COMPATIBILITY WITH X87 FPU ARCHITECTURE. . . . . . . . . . . . . . . . . . . . . . . 9-10

9.5.1 MMX Instructions and the x87 FPU Tag Word . . . . . . . . . . . . . . . . . . . . . . . . . .9-10

9.6 WRITING APPLICATIONS WITH MMX CODE . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-10

9.6.1 Checking for MMX Technology Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-10

9.6.2 Transitions Between x87 FPU and MMX Code. . . . . . . . . . . . . . . . . . . . . . . . . .9-11

9.6.3 Using the EMMS Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-12

9.6.4 Mixing MMX and x87 FPU Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-12

9.6.5 Interfacing with MMX Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-13

9.6.6 Using MMX Code in a Multitasking Operating System Environment. . . . . . . . . .9-13

9.6.7 Exception Handling in MMX Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-14

9.6.8 Register Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-14

9.6.9 Effect of Instruction Prefixes on MMX Instructions . . . . . . . . . . . . . . . . . . . . . . .9-14

CHAPTER 10

PROGRAMMING WITH STREAMING SIMD EXTENSIONS (SSE)

10.1 OVERVIEW OF SSE EXTENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

10.2 SSE PROGRAMMING ENVIRONMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

10.2.1 SSE in 64-Bit Mode and Compatibility Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

10.2.2 XMM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

10.2.3 MXCSR Control and Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-5

10.2.3.1 SIMD Floating-Point Mask and Flag Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-6

10.2.3.2 SIMD Floating-Point Rounding Control Field . . . . . . . . . . . . . . . . . . . . . . . . .10-6

10.2.3.3 Flush-To-Zero. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-6

10.2.3.4 Denormals-Are-Zeros . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-7

10.2.4 Compatibility of SSE Extensions with SSE2/SSE3/MMX and the x87 FPU . . . .10-7

10.3 SSE DATA TYPES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

10.4 SSE INSTRUCTION SET. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

10.4.1 SSE Packed and Scalar Floating-Point Instructions . . . . . . . . . . . . . . . . . . . . . .10-9

10.4.1.1 SSE Data Movement Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-10

10.4.1.2 SSE Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-11

10.4.2 SSE Logical Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-12

10.4.2.1 SSE Comparison Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-13

10.4.2.2 SSE Shuffle and Unpack Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-13

10.4.3 SSE Conversion Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-15

10.4.4 SSE 64-Bit SIMD Integer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-16

10.4.5 MXCSR State Management Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-17

10.4.6 Cacheability Control, Prefetch, and Memory Ordering Instructions. . . . . . . . . .10-17

10.4.6.1 Cacheability Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-17

10.4.6.2 Caching of Temporal vs. Non-Temporal Data . . . . . . . . . . . . . . . . . . . . . . .10-18

10.4.6.3 PREFETCHh Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-19

10.4.6.4 SFENCE Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-19

10.5 FXSAVE AND FXRSTOR INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-20

10.6 HANDLING SSE INSTRUCTION EXCEPTIONS. . . . . . . . . . . . . . . . . . . . . . . . . 10-20

10.7 WRITING APPLICATIONS WITH THE SSE EXTENSIONS . . . . . . . . . . . . . . . . 10-20

x Vol. 1CONTENTS

PAGE

CHAPTER 11

PROGRAMMING WITH STREAMING SIMD EXTENSIONS 2 (SSE2)

11.1 OVERVIEW OF SSE2 EXTENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

11.2 SSE2 PROGRAMMING ENVIRONMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

11.2.1 SSE2 in 64-Bit Mode and Compatibility Mode. . . . . . . . . . . . . . . . . . . . . . . . . . 11-4

11.2.2 Compatibility of SSE2 Extensions with SSE, MMX

Technology and x87 FPU Programming Environment. . . . . . . . . . . . . . . . . . . . 11-4

11.2.3 Denormals-Are-Zeros Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-4

11.3 SSE2 DATA TYPES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

11.4 SSE2 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-6

11.4.1 Packed and Scalar Double-Precision Floating-Point Instructions . . . . . . . . . . . 11-6

11.4.1.1 Data Movement Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-8

11.4.1.2 SSE2 Arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-8

11.4.1.3 SSE2 Logical Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-9

11.4.1.4 SSE2 Comparison Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-10

11.4.1.5 SSE2 Shuffle and Unpack Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-10

11.4.1.6 SSE2 Conversion Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-12

11.4.2 SSE2 64-Bit and 128-Bit SIMD Integer Instructions . . . . . . . . . . . . . . . . . . . . 11-15

11.4.3 128-Bit SIMD Integer Instruction Extensions . . . . . . . . . . . . . . . . . . . . . . . . . . 11-16

11.4.4 Cacheability Control and Memory Ordering Instructions . . . . . . . . . . . . . . . . . 11-16

11.4.4.1 FLUSH Cache Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-16

11.4.4.2 Cacheability Control Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-17

11.4.4.3 Memory Ordering Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-17

11.4.4.4 Pause . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-17

11.4.5 Branch Hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-18

11.5 SSE, SSE2, AND SSE3 EXCEPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-18

11.5.1 SIMD Floating-Point Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-18

11.5.2 SIMD Floating-Point Exception Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-19

11.5.2.1 Invalid Operation Exception (#I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-19

11.5.2.2 Denormal-Operand Exception (#D) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-21

11.5.2.3 Divide-By-Zero Exception (#Z) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-21

11.5.2.4 Numeric Overflow Exception (#O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-21

11.5.2.5 Numeric Underflow Exception (#U). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-22

11.5.2.6 Inexact-Result (Precision) Exception (#P) . . . . . . . . . . . . . . . . . . . . . . . . . 11-22

11.5.3 Generating SIMD Floating-Point Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . 11-23

11.5.3.1 Handling Masked Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-23

11.5.3.2 Handling Unmasked Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-24

11.5.3.3 Handling Combinations of Masked and Unmasked Exceptions . . . . . . . . . 11-25

11.5.4 Handling SIMD Floating-Point Exceptions in Software . . . . . . . . . . . . . . . . . . 11-25

11.5.5 Interaction of SIMD and x87 FPU Floating-Point Exceptions . . . . . . . . . . . . . 11-25

11.6 WRITING APPLICATIONS WITH SSE/SSE2 EXTENSIONS . . . . . . . . . . . . . . . 11-26

11.6.1 General Guidelines for Using SSE/SSE2 Extensions . . . . . . . . . . . . . . . . . . . 11-27

11.6.2 Checking for SSE/SSE2 Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-27

11.6.3 Checking for the DAZ Flag in the MXCSR Register . . . . . . . . . . . . . . . . . . . . 11-28

11.6.4 Initialization of SSE/SE2 Extensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-28

11.6.5 Saving and Restoring the SSE/SSE2 State. . . . . . . . . . . . . . . . . . . . . . . . . . . 11-29

11.6.6 Guidelines for Writing to the MXCSR Register . . . . . . . . . . . . . . . . . . . . . . . . 11-30

11.6.7 Interaction of SSE/SSE2 Instructions with x87 FPU and MMX Instructions . . 11-31

11.6.8 Compatibility of SIMD and x87 FPU Floating-Point Data Types . . . . . . . . . . . 11-31

11.6.9 Mixing Packed and Scalar Floating-Point and

128-Bit SIMD Integer Instructions and Data . . . . . . . . . . . . . . . . . . . . . . . . . . 11-32

11.6.10 Interfacing with SSE/SSE2 Procedures and Functions . . . . . . . . . . . . . . . . . . 11-33

Vol. 1 xiCONTENTS

PAGE

11.6.10.1 Passing Parameters in XMM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-33

11.6.10.2 Saving XMM Register State on a Procedure or Function Call . . . . . . . . . . .11-33

11.6.10.3 Caller-Save Requirement for Procedure and Function Calls . . . . . . . . . . . .11-34

11.6.11 Updating Existing MMX Technology Routines

Using 128-Bit SIMD Integer Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-34

11.6.12 Branching on Arithmetic Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-35

11.6.13 Cacheability Hint Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-35

11.6.14 Effect of Instruction Prefixes on the SSE/SSE2 Instructions. . . . . . . . . . . . . . .11-36

CHAPTER 12

PROGRAMMING WITH STREAMING SIMD EXTENSIONS 3 (SSE3)

12.1 OVERVIEW OF SSE3 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

12.2 SSE3 PROGRAMMING ENVIRONMENT AND DATA TYPES . . . . . . . . . . . . . . . 12-1

12.2.1 SSE3 in 64-Bit Mode and Compatibility Mode. . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

12.2.2 Compatibility of SSE3 Extensions with MMX Technology, the x87

FPU Environment, and SSE/SSE2 Extensions . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

12.2.3 Horizontal and Asymmetric Processing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

12.3 SSE3 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-3

12.3.1 x87 FPU Instruction for Integer Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-3

12.3.2 SIMD Integer Instruction for Specialized 128-bit Unaligned Data Load . . . . . . .12-4

12.3.3 SIMD Floating-Point Instructions That Enhance LOAD/MOVE/DUPLICATE

Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-4

12.3.4 SIMD Floating-Point Instructions Provide Packed Addition/Subtraction . . . . . . .12-5

12.3.5 SIMD Floating-Point Instructions Provide Horizontal Addition/Subtraction . . . . .12-5

12.3.6 Two Thread Synchronization Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-6

12.4 SSE3 EXCEPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-6

12.4.1 Device Not Available (DNA) Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-7

12.4.2 Numeric Error flag and IGNNE# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-7

12.4.3 Emulation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-7

12.5 WRITING APPLICATIONS WITH SSE3 EXTENSIONS . . . . . . . . . . . . . . . . . . . . 12-7

12.5.1 General Guidelines for Using SSE3 Extensions . . . . . . . . . . . . . . . . . . . . . . . . .12-7

12.5.2 Checking for SSE3 Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-8

12.5.3 Enable FTZ and DAZ for SIMD Floating-Point Computation. . . . . . . . . . . . . . . .12-9

12.5.4 Programming SSE3 with SSE/SSE2 Extensions . . . . . . . . . . . . . . . . . . . . . . . .12-9

CHAPTER 13

INPUT/OUTPUT

13.1 I/O PORT ADDRESSING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-1

13.2 I/O PORT HARDWARE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-1

13.3 I/O ADDRESS SPACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-2

13.3.1 Memory-Mapped I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-2

13.4 I/O INSTRUCTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-3

13.5 PROTECTED-MODE I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-4

13.5.1 I/O Privilege Level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-4

13.5.2 I/O Permission Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-5

13.6 ORDERING I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-6

CHAPTER 14

PROCESSOR IDENTIFICATION AND FEATURE DETERMINATION

14.1 USING THE CPUID INSTRUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-1

14.1.1 Notes on Where to Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

xii Vol. 1CONTENTS

PAGE

14.1.2 Identification of Earlier IA-32 Processors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-2

APPENDIX A

EFLAGS CROSS-REFERENCE

A.1 EFLAGS AND INSTRUCTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

APPENDIX B

EFLAGS CONDITION CODES

B.1 CONDITION CODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

APPENDIX C

FLOATING-POINT EXCEPTIONS SUMMARY

C.1 OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-1

C.2 X87 FPU INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-2

C.3 SSE INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-4

C.4 SSE2 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-6

C.5 SSE3 INSTRUCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . C-10

APPENDIX D

GUIDELINES FOR WRITING X87 FPU EXCEPTION HANDLERS

D.1 ORIGIN OF THE MS-DOS COMPATIBILITY SUB-MODE

FOR HANDLING X87 FPU EXCEPTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-2

D.2 IMPLEMENTATION OF THE MS-DOS COMPATIBILITY

SUB-MODE IN THE INTEL486, PENTIUM, AND P6

PROCESSOR FAMILY, AND PENTIUM 4 PROCESSORS. . . . . . . . . . . . . . . . . . . D-3

D.2.1 MS-DOS Compatibility Sub-mode in the Intel486 and Pentium Processors . . . . D-3

D.2.1.1 Basic Rules: When FERR# Is Generated . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-4

D.2.1.2 Recommended External Hardware to Support the

MS-DOS Compatibility Sub-mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-5

D.2.1.3 No-Wait x87 FPU Instructions Can Get x87 FPU Interrupt in Window . . . . . . D-7

D.2.2 MS-DOS Compatibility Sub-mode in the P6 Family

and Pentium 4 Processors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-9

D.3 RECOMMENDED PROTOCOL FOR MS-DOS*

COMPATIBILITY HANDLERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-10

D.3.1 Floating-Point Exceptions and Their Defaults . . . . . . . . . . . . . . . . . . . . . . . . . . D-11

D.3.2 Two Options for Handling Numeric Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . D-11

D.3.2.1 Automatic Exception Handling: Using Masked Exceptions. . . . . . . . . . . . . . D-11

D.3.2.2 Software Exception Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-13

D.3.3 Synchronization Required for Use of x87 FPU Exception Handlers . . . . . . . . . D-14

D.3.3.1 Exception Synchronization: What, Why and When. . . . . . . . . . . . . . . . . . . . D-14

D.3.3.2 Exception Synchronization Examples. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-16

D.3.3.3 Proper Exception Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-16

D.3.4 x87 FPU Exception Handling Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-17

D.3.5 Need for Storing State of IGNNE# Circuit

If Using x87 FPU and SMM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-22

D.3.6 Considerations When x87 FPU Shared Between Tasks . . . . . . . . . . . . . . . . . . D-23

D.3.6.1 Speculatively Deferring x87 FPU Saves, General Overview . . . . . . . . . . . . D-23

D.3.6.2 Tracking x87 FPU Ownership . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-24

D.3.6.3 Interaction of x87 FPU State Saves and Floating-Point Exception

Association . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-25

D.3.6.4 Interrupt Routing From the Kernel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-27

Vol. 1 xiiiCONTENTS

PAGE

D.3.6.5 Special Considerations for Operating Systems that Support

Streaming SIMD Extensions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-28

D.4 DIFFERENCES FOR HANDLERS USING NATIVE MODE. . . . . . . . . . . . . . . . . . D-28

D.4.1 Origin with the Intel 286 and Intel 287, and Intel386 and Intel 387

Processors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-29

D.4.2 Changes with Intel486, Pentium and Pentium Pro Processors with

CR0.NE[bit 5] = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-29

D.4.3 Considerations When x87 FPU Shared Between Tasks Using Native Mode . . D-30

APPENDIX E

GUIDELINES FOR WRITING SIMD FLOATING-POINT EXCEPTION HANDLERS

E.1 TWO OPTIONS FOR HANDLING FLOATING-POINT EXCEPTIONS . . . . . . . . . . E-1

E.2 SOFTWARE EXCEPTION HANDLING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-1

E.3 EXCEPTION SYNCHRONIZATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-3

E.4 SIMD FLOATING-POINT EXCEPTIONS AND THE IEEE STANDARD 754 . . . . . . E-4

E.4.1 Floating-Point Emulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-4

E.4.2 SSE/SSE2/SSE3 Response To Floating-Point Exceptions. . . . . . . . . . . . . . . . . E-6

E.4.2.1 Numeric Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-7

E.4.2.2 Results of Operations with NaN Operands or a NaN Result for

SSE/SSE2/SSE3 Numeric Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-7

E.4.2.3 Condition Codes, Exception Flags, and Response for Masked

and Unmasked Numeric Exceptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . E-12

E.4.3 Example SIMD Floating-Point Emulation Implementation. . . . . . . . . . . . . . . . . E-19

xiv Vol. 1CONTENTS

PAGE

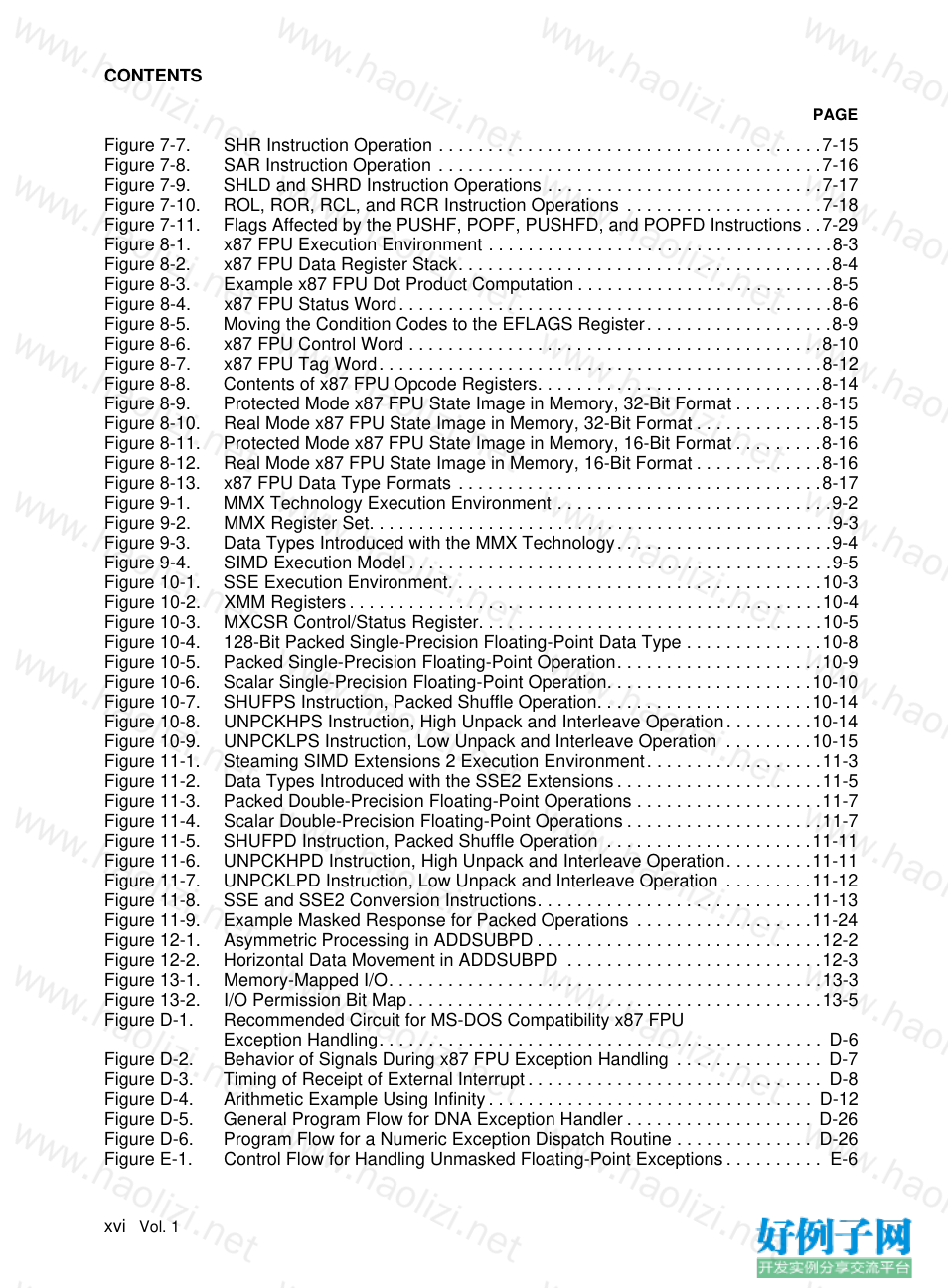

FIGURES

Figure 1-1. Bit and Byte Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Figure 1-2. Syntax for CPUID, CR, and MSR Data Presentation . . . . . . . . . . . . . . . . . . . 1-7

Figure 2-1. The P6 Processor Microarchitecture with Advanced Transfer

Cache Enhancement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Figure 2-2. The Intel NetBurst Microarchitecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Figure 2-3. SIMD Extensions, Register Layouts, and Data Types . . . . . . . . . . . . . . . . . 2-13

Figure 2-4. Comparison of an IA-32 Processor Supporting Hyper-Threading

Technology and a Traditional Dual Processor System . . . . . . . . . . . . . . . . . 2-14

Figure 2-5. IA-32 Processors that Support Dual-Core . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

Figure 3-1. IA-32 Basic Execution Environment for Non-64-bit Modes. . . . . . . . . . . . . . . 3-4

Figure 3-2. 64-Bit Mode Execution Environment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

Figure 3-3. Three Memory Management Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

Figure 3-4. General System and Application Programming Registers . . . . . . . . . . . . . . 3-14

Figure 3-5. Alternate General-Purpose Register Names . . . . . . . . . . . . . . . . . . . . . . . . 3-15

Figure 3-6. Use of Segment Registers for Flat Memory Model . . . . . . . . . . . . . . . . . . . . 3-17

Figure 3-7. Use of Segment Registers in Segmented Memory Model . . . . . . . . . . . . . . 3-18

Figure 3-8. EFLAGS Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-21

Figure 3-9. Memory Operand Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-28

Figure 3-10. Memory Operand Address in 64-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

Figure 3-11. Offset (or Effective Address) Computation . . . . . . . . . . . . . . . . . . . . . . . . . . 3-31

Figure 4-1. Fundamental Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Figure 4-2. Bytes, Words, Doublewords, Quadwords, and Double Quadwords

in Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Figure 4-3. Numeric Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Figure 4-4. Pointer Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Figure 4-5. Pointers in 64-Bit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Figure 4-6. Bit Field Data Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Figure 4-7. 64-Bit Packed SIMD Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Figure 4-8. 128-Bit Packed SIMD Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

Figure 4-9. BCD Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

Figure 4-10. Binary Real Number System. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

Figure 4-11. Binary Floating-Point Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-14

Figure 4-12. Real Numbers and NaNs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

Figure 6-1. Stack Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Figure 6-2. Stack on Near and Far Calls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

Figure 6-3. Protection Rings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

Figure 6-4. Stack Switch on a Call to a Different Privilege Level . . . . . . . . . . . . . . . . . . 6-10

Figure 6-5. Stack Usage on Transfers to Interrupt and Exception Handling Routines . . 6-15

Figure 6-6. Nested Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-21

Figure 6-7. Stack Frame After Entering the MAIN Procedure . . . . . . . . . . . . . . . . . . . . . 6-22

Figure 6-8. Stack Frame After Entering Procedure A . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-23

Figure 6-9. Stack Frame After Entering Procedure B . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24

Figure 6-10. Stack Frame After Entering Procedure C . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25

Figure 7-1. Operation of the PUSH Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

Figure 7-2. Operation of the PUSHA Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

Figure 7-3. Operation of the POP Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

Figure 7-4. Operation of the POPA Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Figure 7-5. Sign Extension . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

Figure 7-6. SHL/SAL Instruction Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

Vol. 1 xvCONTENTS

PAGE

Figure 7-7. SHR Instruction Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-15

Figure 7-8. SAR Instruction Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-16

Figure 7-9. SHLD and SHRD Instruction Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-17

Figure 7-10. ROL, ROR, RCL, and RCR Instruction Operations . . . . . . . . . . . . . . . . . . . .7-18

Figure 7-11. Flags Affected by the PUSHF, POPF, PUSHFD, and POPFD Instructions . .7-29

Figure 8-1. x87 FPU Execution Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-3

Figure 8-2. x87 FPU Data Register Stack. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-4

Figure 8-3. Example x87 FPU Dot Product Computation . . . . . . . . . . . . . . . . . . . . . . . . . .8-5

Figure 8-4. x87 FPU Status Word. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-6

Figure 8-5. Moving the Condition Codes to the EFLAGS Register. . . . . . . . . . . . . . . . . . .8-9

Figure 8-6. x87 FPU Control Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-10

Figure 8-7. x87 FPU Tag Word. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-12

Figure 8-8. Contents of x87 FPU Opcode Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-14

Figure 8-9. Protected Mode x87 FPU State Image in Memory, 32-Bit Format . . . . . . . . .8-15

Figure 8-10. Real Mode x87 FPU State Image in Memory, 32-Bit Format . . . . . . . . . . . . .8-15

Figure 8-11. Protected Mode x87 FPU State Image in Memory, 16-Bit Format . . . . . . . . .8-16

Figure 8-12. Real Mode x87 FPU State Image in Memory, 16-Bit Format . . . . . . . . . . . . .8-16

Figure 8-13. x87 FPU Data Type Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-17

Figure 9-1. MMX Technology Execution Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-2

Figure 9-2. MMX Register Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-3

Figure 9-3. Data Types Introduced with the MMX Technology. . . . . . . . . . . . . . . . . . . . . .9-4

Figure 9-4. SIMD Execution Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-5

Figure 10-1. SSE Execution Environment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-3

Figure 10-2. XMM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-4

Figure 10-3. MXCSR Control/Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-5

Figure 10-4. 128-Bit Packed Single-Precision Floating-Point Data Type . . . . . . . . . . . . . .10-8

Figure 10-5. Packed Single-Precision Floating-Point Operation. . . . . . . . . . . . . . . . . . . . .10-9

Figure 10-6. Scalar Single-Precision Floating-Point Operation. . . . . . . . . . . . . . . . . . . . .10-10

Figure 10-7. SHUFPS Instruction, Packed Shuffle Operation. . . . . . . . . . . . . . . . . . . . . .10-14

Figure 10-8. UNPCKHPS Instruction, High Unpack and Interleave Operation. . . . . . . . .10-14

Figure 10-9. UNPCKLPS Instruction, Low Unpack and Interleave Operation . . . . . . . . .10-15

Figure 11-1. Steaming SIMD Extensions 2 Execution Environment. . . . . . . . . . . . . . . . . .11-3

Figure 11-2. Data Types Introduced with the SSE2 Extensions . . . . . . . . . . . . . . . . . . . . .11-5

Figure 11-3. Packed Double-Precision Floating-Point Operations . . . . . . . . . . . . . . . . . . .11-7

Figure 11-4. Scalar Double-Precision Floating-Point Operations . . . . . . . . . . . . . . . . . . . .11-7

Figure 11-5. SHUFPD Instruction, Packed Shuffle Operation . . . . . . . . . . . . . . . . . . . . .11-11

Figure 11-6. UNPCKHPD Instruction, High Unpack and Interleave Operation. . . . . . . . .11-11

Figure 11-7. UNPCKLPD Instruction, Low Unpack and Interleave Operation . . . . . . . . .11-12

Figure 11-8. SSE and SSE2 Conversion Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . .11-13

Figure 11-9. Example Masked Response for Packed Operations . . . . . . . . . . . . . . . . . .11-24

Figure 12-1. Asymmetric Processing in ADDSUBPD . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

Figure 12-2. Horizontal Data Movement in ADDSUBPD . . . . . . . . . . . . . . . . . . . . . . . . . .12-3

Figure 13-1. Memory-Mapped I/O. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-3

Figure 13-2. I/O Permission Bit Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-5

Figure D-1. Recommended Circuit for MS-DOS Compatibility x87 FPU

Exception Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-6

Figure D-2. Behavior of Signals During x87 FPU Exception Handling . . . . . . . . . . . . . . . D-7

Figure D-3. Timing of Receipt of External Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-8

Figure D-4. Arithmetic Example Using Infinity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . D-12

Figure D-5. General Program Flow for DNA Exception Handler . . . . . . . . . . . . . . . . . . . D-26

Figure D-6. Program Flow for a Numeric Exception Dispatch Routine . . . . . . . . . . . . . . D-26

Figure E-1. Control Flow for Handling Unmasked Floating-Point Exceptions . . . . . . . . . . E-6

xvi Vol. 1CONTENTS

PAGE

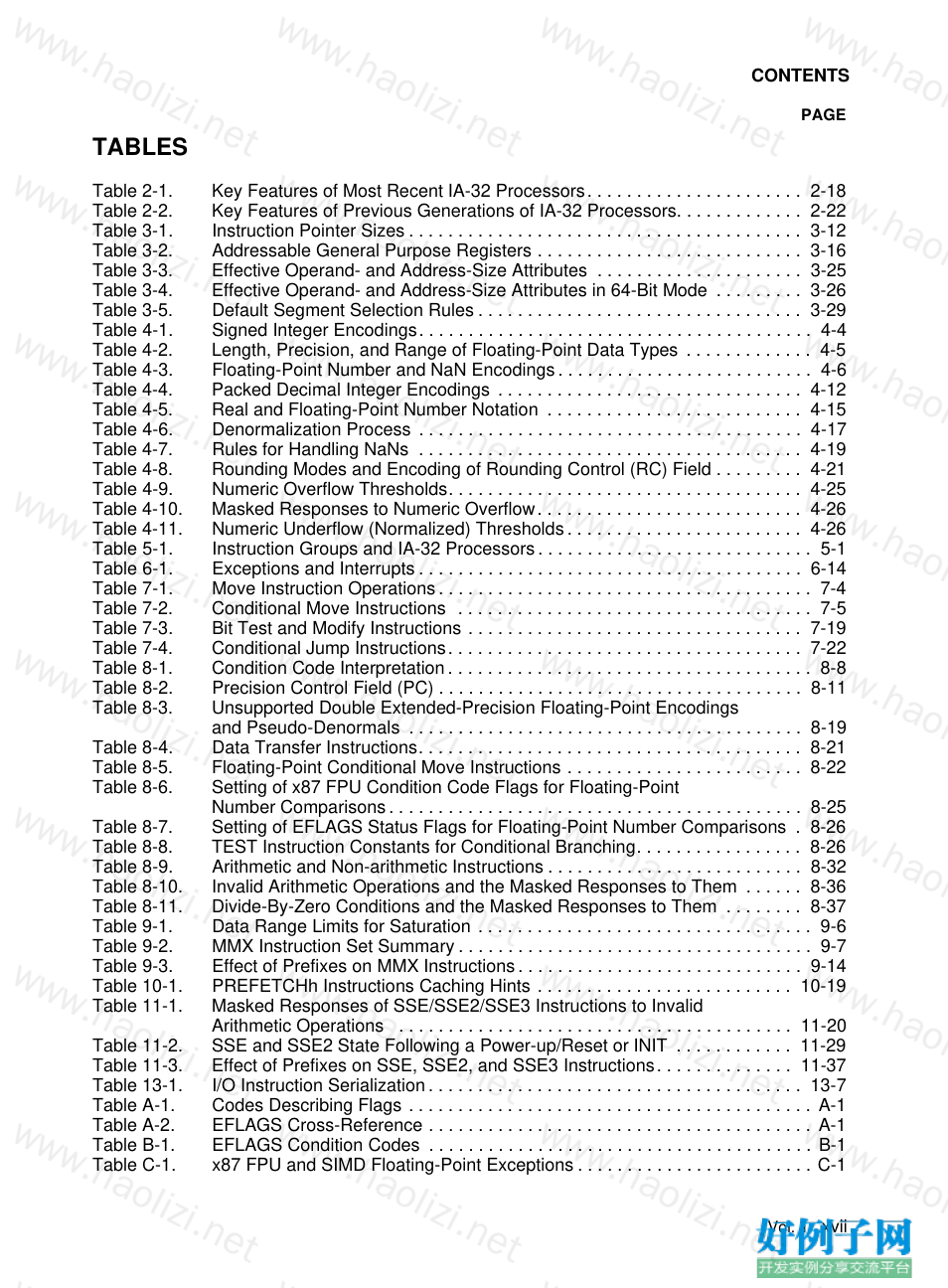

TABLES

Table 2-1. Key Features of Most Recent IA-32 Processors. . . . . . . . . . . . . . . . . . . . . . 2-18

Table 2-2. Key Features of Previous Generations of IA-32 Processors. . . . . . . . . . . . . 2-22

Table 3-1. Instruction Pointer Sizes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

Table 3-2. Addressable General Purpose Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

Table 3-3. Effective Operand- and Address-Size Attributes . . . . . . . . . . . . . . . . . . . . . 3-25

Table 3-4. Effective Operand- and Address-Size Attributes in 64-Bit Mode . . . . . . . . . 3-26

Table 3-5. Default Segment Selection Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-29

Table 4-1. Signed Integer Encodings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Table 4-2. Length, Precision, and Range of Floating-Point Data Types . . . . . . . . . . . . . 4-5

Table 4-3. Floating-Point Number and NaN Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Table 4-4. Packed Decimal Integer Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

Table 4-5. Real and Floating-Point Number Notation . . . . . . . . . . . . . . . . . . . . . . . . . . 4-15

Table 4-6. Denormalization Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

Table 4-7. Rules for Handling NaNs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

Table 4-8. Rounding Modes and Encoding of Rounding Control (RC) Field . . . . . . . . . 4-21

Table 4-9. Numeric Overflow Thresholds. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

Table 4-10. Masked Responses to Numeric Overflow. . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

Table 4-11. Numeric Underflow (Normalized) Thresholds . . . . . . . . . . . . . . . . . . . . . . . . 4-26

Table 5-1. Instruction Groups and IA-32 Processors . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Table 6-1. Exceptions and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-14

Table 7-1. Move Instruction Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

Table 7-2. Conditional Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

Table 7-3. Bit Test and Modify Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-19

Table 7-4. Conditional Jump Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-22

Table 8-1. Condition Code Interpretation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

Table 8-2. Precision Control Field (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

Table 8-3. Unsupported Double Extended-Precision Floating-Point Encodings

and Pseudo-Denormals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-19

Table 8-4. Data Transfer Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-21

Table 8-5. Floating-Point Conditional Move Instructions . . . . . . . . . . . . . . . . . . . . . . . . 8-22

Table 8-6. Setting of x87 FPU Condition Code Flags for Floating-Point

Number Comparisons . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-25

Table 8-7. Setting of EFLAGS Status Flags for Floating-Point Number Comparisons . 8-26

Table 8-8. TEST Instruction Constants for Conditional Branching. . . . . . . . . . . . . . . . . 8-26

Table 8-9. Arithmetic and Non-arithmetic Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . 8-32

Table 8-10. Invalid Arithmetic Operations and the Masked Responses to Them . . . . . . 8-36

Table 8-11. Divide-By-Zero Conditions and the Masked Responses to Them . . . . . . . . 8-37

Table 9-1. Data Range Limits for Saturation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6

Table 9-2. MMX Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-7

Table 9-3. Effect of Prefixes on MMX Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-14

Table 10-1. PREFETCHh Instructions Caching Hints . . . . . . . . . . . . . . . . . . . . . . . . . . 10-19

Table 11-1. Masked Responses of SSE/SSE2/SSE3 Instructions to Invalid

Arithmetic Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-20

Table 11-2. SSE and SSE2 State Following a Power-up/Reset or INIT . . . . . . . . . . . . 11-29

Table 11-3. Effect of Prefixes on SSE, SSE2, and SSE3 Instructions. . . . . . . . . . . . . . 11-37

Table 13-1. I/O Instruction Serialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-7

Table A-1. Codes Describing Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Table A-2. EFLAGS Cross-Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Table B-1. EFLAGS Condition Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Table C-1. x87 FPU and SIMD Floating-Point Exceptions . . . . . . . . . . . . . . . . . . . . . . . . C-1