实例介绍

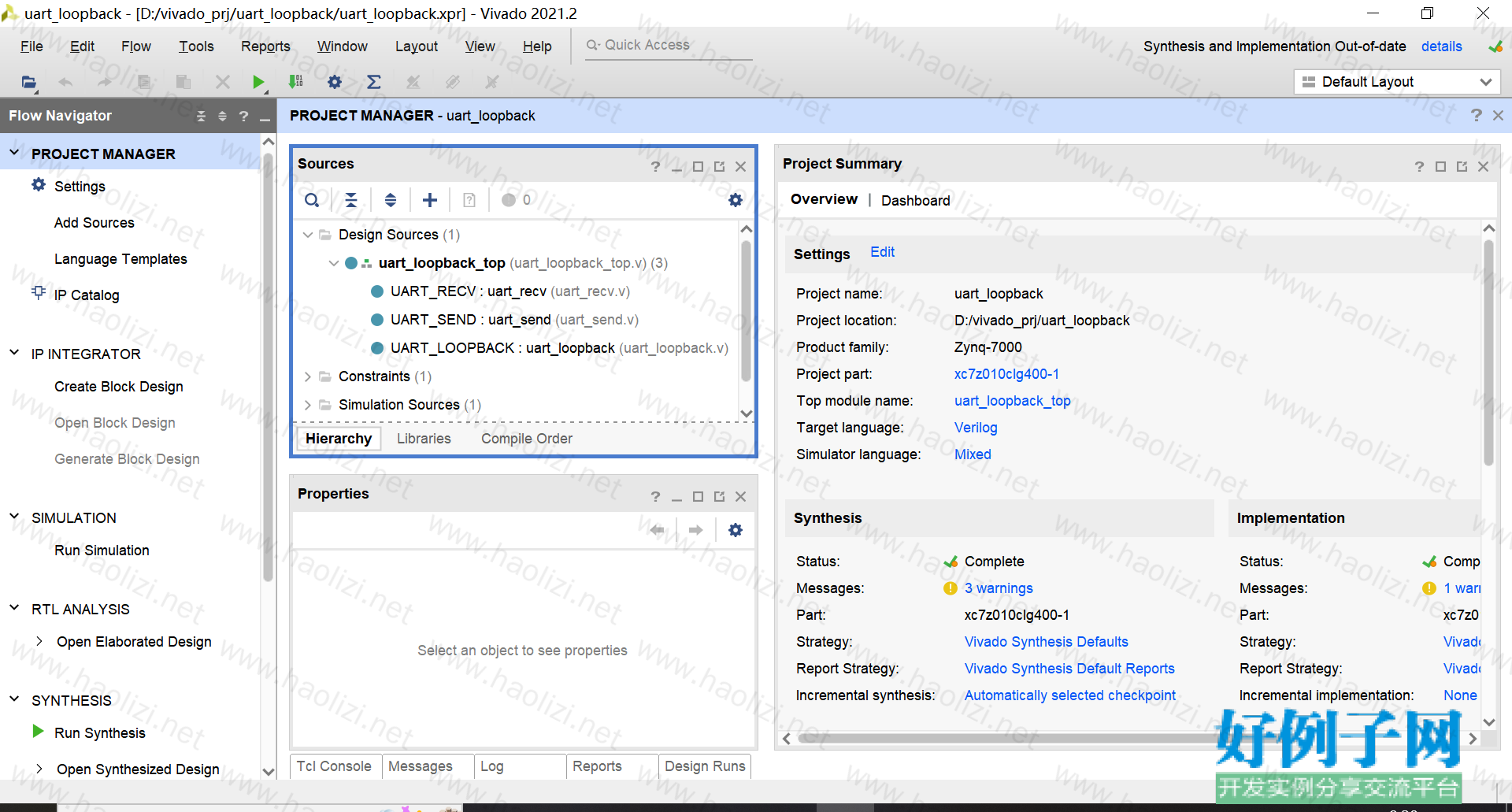

【实例截图】

【核心代码】

.

├── uart_loopback

│ ├── uart_loopback.cache

│ │ ├── compile_simlib

│ │ │ ├── activehdl

│ │ │ ├── modelsim

│ │ │ ├── questa

│ │ │ ├── riviera

│ │ │ ├── vcs

│ │ │ └── xcelium

│ │ ├── ip

│ │ │ └── 2021.2

│ │ └── wt

│ │ ├── project.wpc

│ │ ├── synthesis.wdf

│ │ ├── synthesis_details.wdf

│ │ └── webtalk_pa.xml

│ ├── uart_loopback.hw

│ │ ├── hw_1

│ │ │ ├── hw.xml

│ │ │ ├── layout

│ │ │ └── wave

│ │ └── uart_loopback.lpr

│ ├── uart_loopback.ip_user_files

│ │ └── README.txt

│ ├── uart_loopback.runs

│ │ ├── impl_1

│ │ │ ├── ISEWrap.js

│ │ │ ├── ISEWrap.sh

│ │ │ ├── gen_run.xml

│ │ │ ├── htr.txt

│ │ │ ├── init_design.pb

│ │ │ ├── opt_design.pb

│ │ │ ├── phys_opt_design.pb

│ │ │ ├── place_design.pb

│ │ │ ├── project.wdf

│ │ │ ├── route_design.pb

│ │ │ ├── rundef.js

│ │ │ ├── runme.bat

│ │ │ ├── runme.log

│ │ │ ├── runme.sh

│ │ │ ├── uart_loopback_top.bit

│ │ │ ├── uart_loopback_top.tcl

│ │ │ ├── uart_loopback_top.vdi

│ │ │ ├── uart_loopback_top_bus_skew_routed.pb

│ │ │ ├── uart_loopback_top_bus_skew_routed.rpt

│ │ │ ├── uart_loopback_top_bus_skew_routed.rpx

│ │ │ ├── uart_loopback_top_clock_utilization_routed.rpt

│ │ │ ├── uart_loopback_top_control_sets_placed.rpt

│ │ │ ├── uart_loopback_top_drc_opted.pb

│ │ │ ├── uart_loopback_top_drc_opted.rpt

│ │ │ ├── uart_loopback_top_drc_opted.rpx

│ │ │ ├── uart_loopback_top_drc_routed.pb

│ │ │ ├── uart_loopback_top_drc_routed.rpt

│ │ │ ├── uart_loopback_top_drc_routed.rpx

│ │ │ ├── uart_loopback_top_io_placed.rpt

│ │ │ ├── uart_loopback_top_methodology_drc_routed.pb

│ │ │ ├── uart_loopback_top_methodology_drc_routed.rpt

│ │ │ ├── uart_loopback_top_methodology_drc_routed.rpx

│ │ │ ├── uart_loopback_top_opt.dcp

│ │ │ ├── uart_loopback_top_physopt.dcp

│ │ │ ├── uart_loopback_top_placed.dcp

│ │ │ ├── uart_loopback_top_power_routed.rpt

│ │ │ ├── uart_loopback_top_power_routed.rpx

│ │ │ ├── uart_loopback_top_power_summary_routed.pb

│ │ │ ├── uart_loopback_top_route_status.pb

│ │ │ ├── uart_loopback_top_route_status.rpt

│ │ │ ├── uart_loopback_top_routed.dcp

│ │ │ ├── uart_loopback_top_timing_summary_routed.pb

│ │ │ ├── uart_loopback_top_timing_summary_routed.rpt

│ │ │ ├── uart_loopback_top_timing_summary_routed.rpx

│ │ │ ├── uart_loopback_top_utilization_placed.pb

│ │ │ ├── uart_loopback_top_utilization_placed.rpt

│ │ │ ├── vivado.jou

│ │ │ ├── vivado.pb

│ │ │ └── write_bitstream.pb

│ │ └── synth_1

│ │ ├── ISEWrap.js

│ │ ├── ISEWrap.sh

│ │ ├── __synthesis_is_complete__

│ │ ├── gen_run.xml

│ │ ├── htr.txt

│ │ ├── rundef.js

│ │ ├── runme.bat

│ │ ├── runme.log

│ │ ├── runme.sh

│ │ ├── uart_loopback_top.dcp

│ │ ├── uart_loopback_top.tcl

│ │ ├── uart_loopback_top.vds

│ │ ├── uart_loopback_top_utilization_synth.pb

│ │ ├── uart_loopback_top_utilization_synth.rpt

│ │ ├── vivado.jou

│ │ └── vivado.pb

│ ├── uart_loopback.sim

│ ├── uart_loopback.srcs

│ │ ├── constrs_1

│ │ │ └── new

│ │ │ └── uart_loopback.xdc

│ │ ├── sources_1

│ │ │ └── new

│ │ │ ├── uart_loopback.v

│ │ │ ├── uart_loopback_top.v

│ │ │ ├── uart_recv.v

│ │ │ └── uart_send.v

│ │ └── utils_1

│ │ └── imports

│ │ └── synth_1

│ │ └── uart_loopback_top.dcp

│ ├── uart_loopback.xpr

│ ├── vivado.jou

│ ├── vivado.log

│ ├── vivado_18984.backup.jou

│ └── vivado_18984.backup.log

└── zynq7系列FPGA串口通信回环实验.zip

29 directories, 84 files

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论