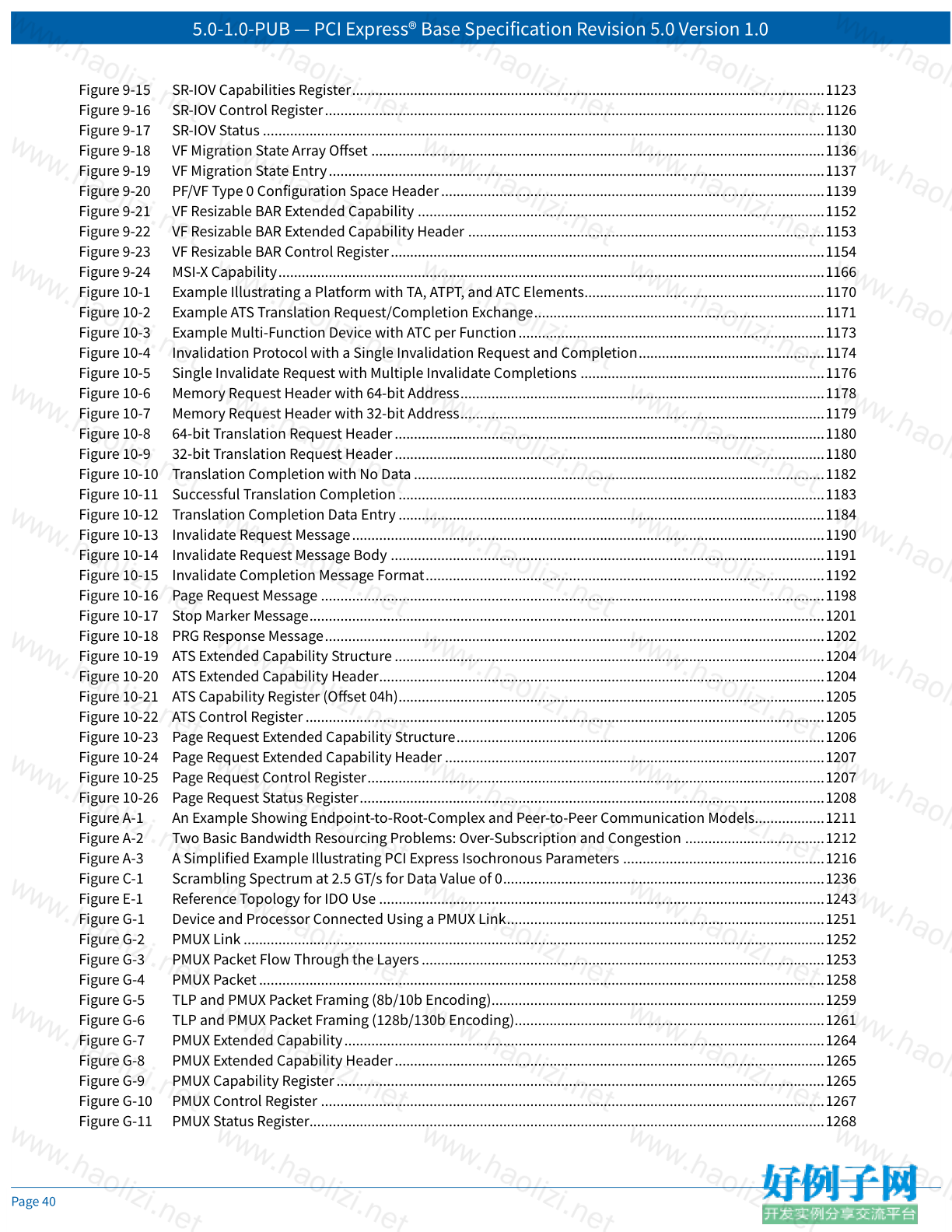

实例介绍

【实例简介】PCIe标准规范5.0

【实例截图】

【实例截图】

【核心代码】

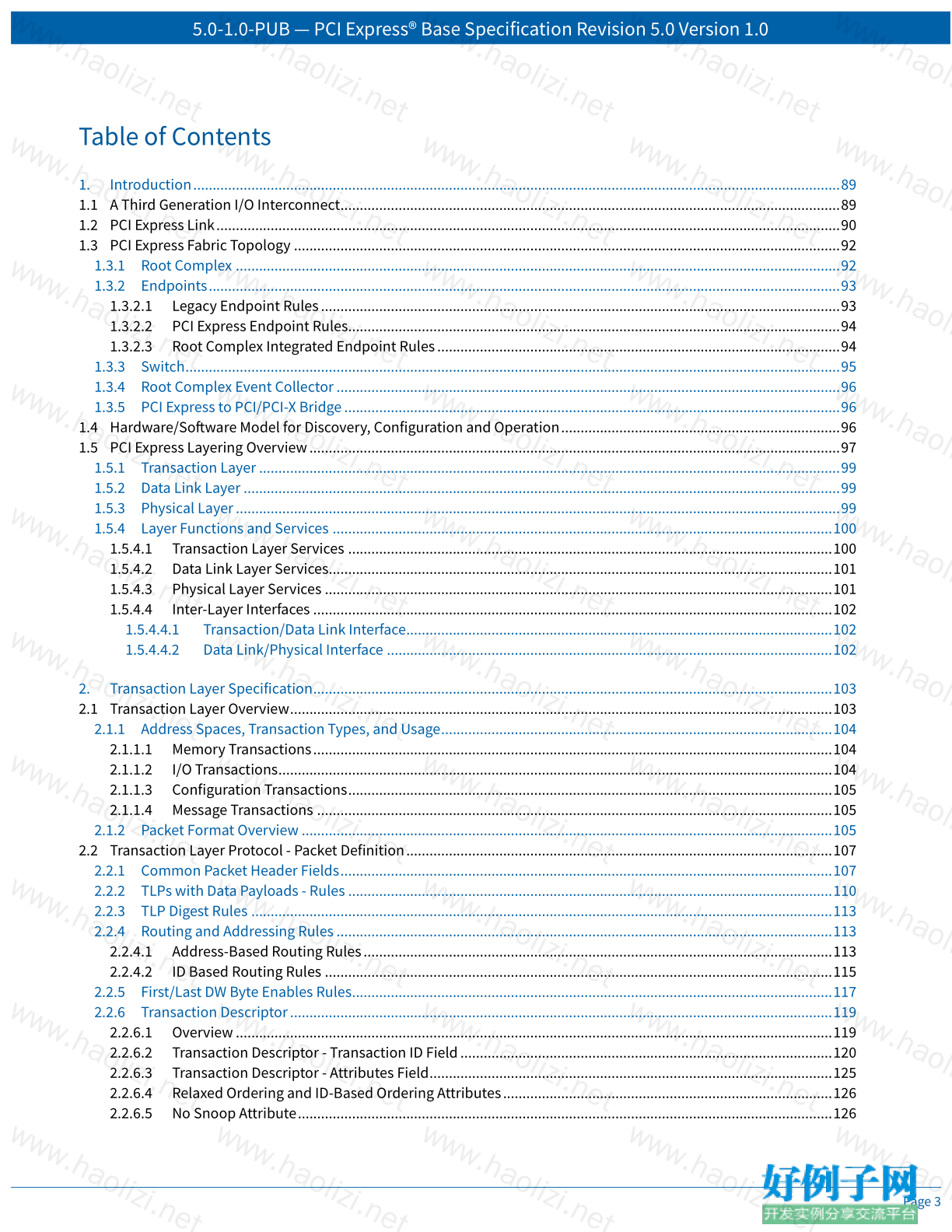

Table of Contents

1.

Introduction.......................................................................................................................................................................89

1.1 A Third Generation I/O Interconnect.................................................................................................................................89

1.2 PCI Express Link.................................................................................................................................................................90

1.3 PCI Express Fabric Topology .............................................................................................................................................92

1.3.1 Root Complex ............................................................................................................................................................92

1.3.2 Endpoints...................................................................................................................................................................93

1.3.2.1

Legacy Endpoint Rules ......................................................................................................................................93

1.3.2.2

PCI Express Endpoint Rules...............................................................................................................................94

1.3.2.3

Root Complex Integrated Endpoint Rules ........................................................................................................94

1.3.3 Switch.........................................................................................................................................................................95

1.3.4 Root Complex Event Collector ..................................................................................................................................96

1.3.5 PCI Express to PCI/PCI-X Bridge ................................................................................................................................96

1.4 Hardware/Software Model for Discovery, Configuration and Operation........................................................................96

1.5 PCI Express Layering Overview.........................................................................................................................................97

1.5.1 Transaction Layer ......................................................................................................................................................99

1.5.2 Data Link Layer ..........................................................................................................................................................99

1.5.3 Physical Layer............................................................................................................................................................99

1.5.4 Layer Functions and Services .................................................................................................................................100

1.5.4.1 Transaction Layer Services .............................................................................................................................100

1.5.4.2

Data Link Layer Services..................................................................................................................................101

1.5.4.3

Physical Layer Services ...................................................................................................................................101

1.5.4.4

Inter-Layer Interfaces ......................................................................................................................................102

1.5.4.4.1

Transaction/Data Link Interface..............................................................................................................102

1.5.4.4.2

Data Link/Physical Interface ...................................................................................................................102

2. Transaction Layer Specification......................................................................................................................................103

2.1 Transaction Layer Overview............................................................................................................................................103

2.1.1 Address Spaces, Transaction Types, and Usage.....................................................................................................104

2.1.1.1

Memory Transactions ......................................................................................................................................104

2.1.1.2

I/O Transactions...............................................................................................................................................104

2.1.1.3

Configuration Transactions.............................................................................................................................105

2.1.1.4

Message Transactions .....................................................................................................................................105

2.1.2 Packet Format Overview .........................................................................................................................................105

2.2 Transaction Layer Protocol - Packet Definition..............................................................................................................107

2.2.1 Common Packet Header Fields...............................................................................................................................107

2.2.2 TLPs with Data Payloads - Rules .............................................................................................................................110

2.2.3 TLP Digest Rules ......................................................................................................................................................113

2.2.4 Routing and Addressing Rules ................................................................................................................................113

2.2.4.1 Address-Based Routing Rules .........................................................................................................................113

2.2.4.2

ID Based Routing Rules ...................................................................................................................................115

2.2.5 First/Last DW Byte Enables Rules............................................................................................................................117

2.2.6 Transaction Descriptor............................................................................................................................................119

2.2.6.1 Overview ..........................................................................................................................................................119

2.2.6.2 Transaction Descriptor - Transaction ID Field ................................................................................................120

2.2.6.3

Transaction Descriptor - Attributes Field........................................................................................................125

2.2.6.4

Relaxed Ordering and ID-Based Ordering Attributes .....................................................................................126

2.2.6.5

No Snoop Attribute..........................................................................................................................................126

5.0-1.0-PUB — PCI Express® Base Specification Revision 5.0 Version 1.0

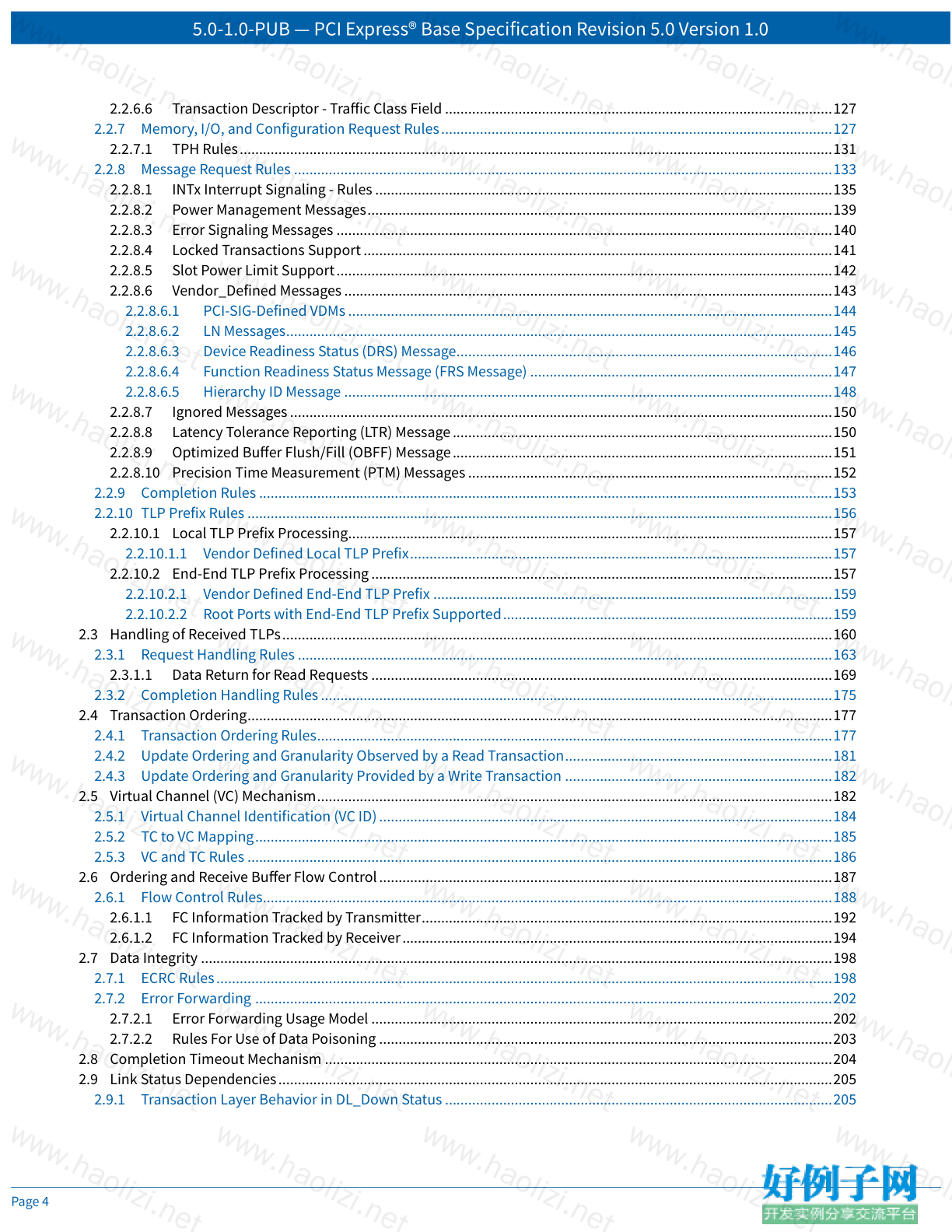

Page 32.2.6.6 Transaction Descriptor - Traffic Class Field ....................................................................................................127

2.2.7 Memory, I/O, and Configuration Request Rules .....................................................................................................127

2.2.7.1 TPH Rules.........................................................................................................................................................131

2.2.8 Message Request Rules ...........................................................................................................................................133

2.2.8.1

INTx Interrupt Signaling - Rules ......................................................................................................................135

2.2.8.2

Power Management Messages........................................................................................................................139

2.2.8.3

Error Signaling Messages ................................................................................................................................140

2.2.8.4

Locked Transactions Support .........................................................................................................................141

2.2.8.5

Slot Power Limit Support................................................................................................................................142

2.2.8.6 Vendor_Defined Messages ..............................................................................................................................143

2.2.8.6.1

PCI-SIG-Defined VDMs .............................................................................................................................144

2.2.8.6.2

LN Messages.............................................................................................................................................145

2.2.8.6.3

Device Readiness Status (DRS) Message.................................................................................................146

2.2.8.6.4

Function Readiness Status Message (FRS Message) ..............................................................................147

2.2.8.6.5

Hierarchy ID Message ..............................................................................................................................148

2.2.8.7

Ignored Messages ............................................................................................................................................150

2.2.8.8

Latency Tolerance Reporting (LTR) Message ..................................................................................................150

2.2.8.9

Optimized Buffer Flush/Fill (OBFF) Message..................................................................................................151

2.2.8.10 Precision Time Measurement (PTM) Messages ..............................................................................................152

2.2.9 Completion Rules ....................................................................................................................................................153

2.2.10 TLP Prefix Rules .......................................................................................................................................................156

2.2.10.1 Local TLP Prefix Processing.............................................................................................................................157

2.2.10.1.1 Vendor Defined Local TLP Prefix.............................................................................................................157

2.2.10.2 End-End TLP Prefix Processing .......................................................................................................................157

2.2.10.2.1 Vendor Defined End-End TLP Prefix .......................................................................................................159

2.2.10.2.2 Root Ports with End-End TLP Prefix Supported.....................................................................................159

2.3 Handling of Received TLPs..............................................................................................................................................160

2.3.1 Request Handling Rules ..........................................................................................................................................163

2.3.1.1

Data Return for Read Requests .......................................................................................................................169

2.3.2 Completion Handling Rules ....................................................................................................................................175

2.4 Transaction Ordering.......................................................................................................................................................177

2.4.1 Transaction Ordering Rules.....................................................................................................................................177

2.4.2 Update Ordering and Granularity Observed by a Read Transaction.....................................................................181

2.4.3 Update Ordering and Granularity Provided by a Write Transaction .....................................................................182

2.5 Virtual Channel (VC) Mechanism.....................................................................................................................................182

2.5.1 Virtual Channel Identification (VC ID).....................................................................................................................184

2.5.2 TC to VC Mapping.....................................................................................................................................................185

2.5.3 VC and TC Rules .......................................................................................................................................................186

2.6 Ordering and Receive Buffer Flow Control .....................................................................................................................187

2.6.1 Flow Control Rules...................................................................................................................................................188

2.6.1.1

FC Information Tracked by Transmitter..........................................................................................................192

2.6.1.2

FC Information Tracked by Receiver...............................................................................................................194

2.7 Data Integrity ...................................................................................................................................................................198

2.7.1 ECRC Rules ...............................................................................................................................................................198

2.7.2 Error Forwarding .....................................................................................................................................................202

2.7.2.1

Error Forwarding Usage Model .......................................................................................................................202

2.7.2.2

Rules For Use of Data Poisoning .....................................................................................................................203

2.8 Completion Timeout Mechanism ...................................................................................................................................204

2.9 Link Status Dependencies ...............................................................................................................................................205

2.9.1 Transaction Layer Behavior in DL_Down Status ....................................................................................................205

5.0-1.0-PUB — PCI Express® Base Specification Revision 5.0 Version 1.0

Page 42.9.2 Transaction Layer Behavior in DL_Up Status .........................................................................................................206

2.9.3 Transaction Layer Behavior During Downstream Port Containment....................................................................206

3.

Data Link Layer Specification..........................................................................................................................................209

3.1 Data Link Layer Overview................................................................................................................................................209

3.2 Data Link Control and Management State Machine.......................................................................................................210

3.2.1 Data Link Control and Management State Machine Rules.....................................................................................211

3.3 Data Link Feature Exchange ............................................................................................................................................214

3.4 Flow Control Initialization Protocol................................................................................................................................215

3.4.1 Flow Control Initialization State Machine Rules.....................................................................................................215

3.4.2 Scaled Flow Control.................................................................................................................................................220

3.5 Data Link Layer Packets (DLLPs) .....................................................................................................................................221

3.5.1 Data Link Layer Packet Rules ..................................................................................................................................221

3.6 Data Integrity Mechansisms ............................................................................................................................................227

3.6.1 Introduction.............................................................................................................................................................227

3.6.2 LCRC, Sequence Number, and Retry Management (TLP Transmitter)..................................................................228

3.6.2.1

LCRC and Sequence Number Rules (TLP Transmitter) ..................................................................................228

3.6.2.2

Handling of Received DLLPs............................................................................................................................235

3.6.3 LCRC and Sequence Number (TLP Receiver)..........................................................................................................238

3.6.3.1

LCRC and Sequence Number Rules (TLP Receiver)........................................................................................239

4.

Physical Layer Logical Block ...........................................................................................................................................245

4.1 Introduction.....................................................................................................................................................................245

4.2 Logical Sub-block ............................................................................................................................................................245

4.2.1 Encoding for 2.5 GT/s and 5.0 GT/s Data Rates .......................................................................................................246

4.2.1.1 Symbol Encoding.............................................................................................................................................246

4.2.1.1.1

Serialization and De-serialization of Data ..............................................................................................246

4.2.1.1.2

Special Symbols for Framing and Link Management (K Codes)............................................................247

4.2.1.1.3

8b/10b Decode Rules...............................................................................................................................248

4.2.1.2

Framing and Application of Symbols to Lanes...............................................................................................249

4.2.1.3

Data Scrambling ..............................................................................................................................................252

4.2.2 Encoding for 8.0 GT/s and Higher Data Rates .........................................................................................................253

4.2.2.1

Lane Level Encoding........................................................................................................................................254

4.2.2.2

Ordered Set Blocks ..........................................................................................................................................256

4.2.2.2.1

Block Alignment ......................................................................................................................................256

4.2.2.3

Data Blocks ......................................................................................................................................................257

4.2.2.3.1

Framing Tokens .......................................................................................................................................258

4.2.2.3.2

Transmitter Framing Requirements........................................................................................................263

4.2.2.3.3

Receiver Framing Requirements.............................................................................................................264

4.2.2.3.4

Recovery from Framing Errors ................................................................................................................266

4.2.2.4

Scrambling.......................................................................................................................................................267

4.2.2.5

Precoding.........................................................................................................................................................272

4.2.2.6

Loopback with 128b/130b Code .....................................................................................................................274

4.2.3 Link Equalization Procedure for 8.0 GT/s and Higher Data Rates..........................................................................274

4.2.3.1

Rules for Transmitter Coefficients ..................................................................................................................286

4.2.3.2

Encoding of Presets .........................................................................................................................................287

4.2.4 Link Initialization and Training ...............................................................................................................................288

4.2.4.1 Training Sequences .........................................................................................................................................288

4.2.4.2 Alternate Protocol Negotiation .......................................................................................................................298

4.2.4.3

Electrical Idle Sequences (EIOS) .....................................................................................................................301

5.0-1.0-PUB — PCI Express® Base Specification Revision 5.0 Version 1.0

Page 54.2.4.4

Inferring Electrical Idle ....................................................................................................................................305

4.2.4.5

Lane Polarity Inversion....................................................................................................................................306

4.2.4.6

Fast Training Sequence (FTS)..........................................................................................................................306

4.2.4.7

Start of Data Stream Ordered Set (SDS Ordered Set).....................................................................................308

4.2.4.8

Link Error Recovery .........................................................................................................................................309

4.2.4.9

Reset.................................................................................................................................................................309

4.2.4.9.1

Fundamental Reset .................................................................................................................................309

4.2.4.9.2

Hot Reset..................................................................................................................................................310

4.2.4.10 Link Data Rate Negotiation .............................................................................................................................310

4.2.4.11 Link Width and Lane Sequence Negotiation ..................................................................................................310

4.2.4.11.1 Required and Optional Port Behavior ....................................................................................................310

4.2.4.12 Lane-to-Lane De-skew.....................................................................................................................................311

4.2.4.13 Lane vs. Link Training......................................................................................................................................312

4.2.5 Link Training and Status State Machine (LTSSM) Descriptions..............................................................................312

4.2.5.1

Detect Overview ..............................................................................................................................................313

4.2.5.2

Polling Overview..............................................................................................................................................313

4.2.5.3

Configuration Overview ..................................................................................................................................313

4.2.5.4

Recovery Overview..........................................................................................................................................313

4.2.5.5

L0 Overview .....................................................................................................................................................314

4.2.5.6

L0s Overview....................................................................................................................................................314

4.2.5.7

L1 Overview .....................................................................................................................................................314

4.2.5.8

L2 Overview .....................................................................................................................................................314

4.2.5.9

Disabled Overview...........................................................................................................................................314

4.2.5.10 Loopback Overview.........................................................................................................................................314

4.2.5.11 Hot Reset Overview .........................................................................................................................................315

4.2.6 Link Training and Status State Rules ......................................................................................................................315

4.2.6.1

Detect...............................................................................................................................................................317

4.2.6.1.1

Detect.Quiet.............................................................................................................................................317

4.2.6.1.2

Detect.Active............................................................................................................................................318

4.2.6.2

Polling ..............................................................................................................................................................319

4.2.6.2.1

Polling.Active ...........................................................................................................................................319

4.2.6.2.2

Polling.Compliance .................................................................................................................................320

4.2.6.2.3

Polling.Configuration ..............................................................................................................................324

4.2.6.2.4

Polling.Speed...........................................................................................................................................325

4.2.6.3

Configuration...................................................................................................................................................325

4.2.6.3.1

Configuration.Linkwidth.Start................................................................................................................326

4.2.6.3.1.1

Downstream Lanes..........................................................................................................................326

4.2.6.3.1.2

Upstream Lanes...............................................................................................................................327

4.2.6.3.2

Configuration.Linkwidth.Accept.............................................................................................................329

4.2.6.3.2.1

Downstream Lanes..........................................................................................................................329

4.2.6.3.2.2

Upstream Lanes...............................................................................................................................330

4.2.6.3.3

Configuration.Lanenum.Accept..............................................................................................................332

4.2.6.3.3.1

Downstream Lanes..........................................................................................................................332

4.2.6.3.3.2

Upstream Lanes...............................................................................................................................333

4.2.6.3.4

Configuration.Lanenum.Wait..................................................................................................................333

4.2.6.3.4.1

Downstream Lanes..........................................................................................................................333

4.2.6.3.4.2

Upstream Lanes...............................................................................................................................334

4.2.6.3.5

Configuration.Complete..........................................................................................................................334

4.2.6.3.5.1

Downstream Lanes..........................................................................................................................334

4.2.6.3.5.2

Upstream Lanes...............................................................................................................................336

5.0-1.0-PUB — PCI Express® Base Specification Revision 5.0 Version 1.0

Page 64.2.6.3.6

Configuration.Idle....................................................................................................................................337

4.2.6.4

Recovery...........................................................................................................................................................340

4.2.6.4.1

Recovery.RcvrLock ..................................................................................................................................340

4.2.6.4.2

Recovery.Equalization.............................................................................................................................346

4.2.6.4.2.1

Downstream Lanes..........................................................................................................................347

4.2.6.4.2.1.1 Phase 1 of Transmitter Equalization.......................................................................................347

4.2.6.4.2.1.2 Phase 2 of Transmitter Equalization.......................................................................................349

4.2.6.4.2.1.3 Phase 3 of Transmitter Equalization.......................................................................................350

4.2.6.4.2.2

Upstream Lanes...............................................................................................................................352

4.2.6.4.2.2.1 Phase 0 of Transmitter Equalization.......................................................................................352

4.2.6.4.2.2.2 Phase 1 of Transmitter Equalization.......................................................................................353

4.2.6.4.2.2.3 Phase 2 of Transmitter Equalization.......................................................................................354

4.2.6.4.2.2.4 Phase 3 of Transmitter Equalization.......................................................................................356

4.2.6.4.3

Recovery.Speed .......................................................................................................................................357

4.2.6.4.4

Recovery.RcvrCfg.....................................................................................................................................358

4.2.6.4.5

Recovery.Idle ...........................................................................................................................................363

4.2.6.5

L0......................................................................................................................................................................366

4.2.6.6

L0s ....................................................................................................................................................................367

4.2.6.6.1

Receiver L0s .............................................................................................................................................368

4.2.6.6.1.1

Rx_L0s.Entry ....................................................................................................................................368

4.2.6.6.1.2

Rx_L0s.Idle.......................................................................................................................................368

4.2.6.6.1.3

Rx_L0s.FTS .......................................................................................................................................368

4.2.6.6.2

Transmitter L0s ........................................................................................................................................369

4.2.6.6.2.1

Tx_L0s.Entry ....................................................................................................................................369

4.2.6.6.2.2

Tx_L0s.Idle .......................................................................................................................................369

4.2.6.6.2.3

Tx_L0s.FTS .......................................................................................................................................369

4.2.6.7

L1......................................................................................................................................................................371

4.2.6.7.1

L1.Entry....................................................................................................................................................371

4.2.6.7.2

L1.Idle.......................................................................................................................................................371

4.2.6.8

L2......................................................................................................................................................................373

4.2.6.8.1

L2.Idle.......................................................................................................................................................373

4.2.6.8.2

L2.TransmitWake .....................................................................................................................................374

4.2.6.9

Disabled ...........................................................................................................................................................374

4.2.6.10 Loopback .........................................................................................................................................................375

4.2.6.10.1 Loopback.Entry .......................................................................................................................................375

4.2.6.10.2 Loopback.Active ......................................................................................................................................378

4.2.6.10.3 Loopback.Exit ..........................................................................................................................................379

4.2.6.11 Hot Reset..........................................................................................................................................................380

4.2.7 Clock Tolerance Compensation ..............................................................................................................................381

4.2.7.1 SKP Ordered Set for 8b/10b Encoding............................................................................................................382

4.2.7.2

SKP Ordered Set for 128b/130b Encoding......................................................................................................382

4.2.7.3

Rules for Transmitters .....................................................................................................................................386

4.2.7.4

Rules for Receivers...........................................................................................................................................387

4.2.8 Compliance Pattern in 8b/10b Encoding................................................................................................................388

4.2.9 Modified Compliance Pattern in 8b/10b Encoding ................................................................................................389

4.2.10 Compliance Pattern in 128b/130b Encoding..........................................................................................................390

4.2.11 Modified Compliance Pattern in 128b/130b Encoding ..........................................................................................393

4.2.12 Jitter Measurement Pattern in 128b/130b..............................................................................................................393

4.2.13 Lane Margining at Receiver.....................................................................................................................................394

4.2.13.1 Receiver Number, Margin Type, Usage Model, and Margin Payload Fields...................................................394

5.0-1.0-PUB — PCI Express® Base Specification Revision 5.0 Version 1.0

Page 74.2.13.1.1 Step Margin Execution Status .................................................................................................................399

4.2.13.1.2 Margin Payload for Step Margin Commands ..........................................................................................399

4.2.13.2 Margin Command and Response Flow...........................................................................................................400

4.2.13.3 Receiver Margin Testing Requirements ..........................................................................................................403

4.3 Retimers ...........................................................................................................................................................................407

4.3.1 Retimer Requirements ............................................................................................................................................408

4.3.2 Supported Retimer Topologies...............................................................................................................................409

4.3.3 Variables...................................................................................................................................................................410

4.3.4 Receiver Impedance Propagation Rules.................................................................................................................411

4.3.5 Switching Between Modes ......................................................................................................................................411

4.3.6 Forwarding Rules.....................................................................................................................................................411

4.3.6.1

Forwarding Type Rules....................................................................................................................................412

4.3.6.2

Orientation and Lane Numbers Rules ............................................................................................................412

4.3.6.3

Electrical Idle Exit Rules ..................................................................................................................................413

4.3.6.4

Data Rate Change and Determination Rules ..................................................................................................415

4.3.6.5

Electrical Idle Entry Rules................................................................................................................................416

4.3.6.6 Transmitter Settings Determination Rules .....................................................................................................417

4.3.6.7

Ordered Set Modification Rules ......................................................................................................................418

4.3.6.8

DLLP, TLP, and Logical Idle Modification Rules ..............................................................................................420

4.3.6.9

8b/10b Encoding Rules....................................................................................................................................421

4.3.6.10 8b/10b Scrambling Rules ................................................................................................................................421

4.3.6.11 Hot Reset Rules................................................................................................................................................421

4.3.6.12 Disable Link Rules............................................................................................................................................421

4.3.6.13 Loopback .........................................................................................................................................................422

4.3.6.14 Compliance Receive Rules ..............................................................................................................................423

4.3.6.15 Enter Compliance Rules ..................................................................................................................................424

4.3.7 Execution Mode Rules .............................................................................................................................................427

4.3.7.1 CompLoadBoard Rules....................................................................................................................................427

4.3.7.1.1

CompLoadBoard.Entry ...........................................................................................................................427

4.3.7.1.2

CompLoadBoard.Pattern ........................................................................................................................427

4.3.7.1.3

CompLoadBoard.Exit ..............................................................................................................................428

4.3.7.2

Link Equalization Rules ...................................................................................................................................429

4.3.7.2.1

Downstream Lanes ..................................................................................................................................429

4.3.7.2.1.1

Phase 2.............................................................................................................................................429

4.3.7.2.1.2

Phase 3 Active..................................................................................................................................429

4.3.7.2.1.3

Phase 3 Passive................................................................................................................................429

4.3.7.2.2

Upstream Lanes.......................................................................................................................................430

4.3.7.2.2.1

Phase 2 Active..................................................................................................................................430

4.3.7.2.2.2

Phase 2 Passive................................................................................................................................430

4.3.7.2.2.3

Phase 3.............................................................................................................................................430

4.3.7.2.3

Force Timeout..........................................................................................................................................431

4.3.7.3

Slave Loopback................................................................................................................................................431

4.3.7.3.1

Slave Loopback.Entry .............................................................................................................................431

4.3.7.3.2

Slave Loopback.Active ............................................................................................................................432

4.3.7.3.3

Slave Loopback.Exit ................................................................................................................................432

4.3.8 Retimer Latency.......................................................................................................................................................432

4.3.8.1

Measurement...................................................................................................................................................432

4.3.8.2

Maximum Limit on Retimer Latency...............................................................................................................432

4.3.8.3

Impacts on Upstream and Downstream Ports ...............................................................................................433

4.3.9 SRIS ..........................................................................................................................................................................433

5.0-1.0-PUB — PCI Express® Base Specification Revision 5.0 Version 1.0

Page 84.3.10 L1 PM Substates Support ........................................................................................................................................434

4.3.11 Retimer Configuration Parameters .........................................................................................................................436

4.3.11.1 Global Parameters ...........................................................................................................................................437

4.3.11.2 Per Physical Pseudo Port Parameters.............................................................................................................437

4.3.12 In Band Register Access ...........................................................................................................................................438

5.

Power Management.........................................................................................................................................................439

5.1 Overview ..........................................................................................................................................................................439

5.2 Link State Power Management .......................................................................................................................................440

5.3 PCI-PM Software Compatible Mechanisms ....................................................................................................................444

5.3.1 Device Power Management States (D-States) of a Function..................................................................................444

5.3.1.1

D0 State ............................................................................................................................................................445

5.3.1.2

D1 State ............................................................................................................................................................445

5.3.1.3

D2 State ............................................................................................................................................................445

5.3.1.4

D3 State ............................................................................................................................................................446

5.3.1.4.1

D3Hot State ...............................................................................................................................................447

5.3.1.4.2

D3Cold State..............................................................................................................................................448

5.3.2 PM Software Control of the Link Power Management State..................................................................................449

5.3.2.1

Entry into the L1 State.....................................................................................................................................450

5.3.2.2

Exit from L1 State.............................................................................................................................................453

5.3.2.3

Entry into the L2/L3 Ready State ....................................................................................................................454

5.3.3 Power Management Event Mechanisms.................................................................................................................454

5.3.3.1

Motivation ........................................................................................................................................................454

5.3.3.2

Link Wakeup.....................................................................................................................................................455

5.3.3.2.1

PME Synchronization...............................................................................................................................456

5.3.3.3

PM_PME Messages...........................................................................................................................................458

5.3.3.3.1

PM_PME “Backpressure” Deadlock Avoidance......................................................................................458

5.3.3.4

PME Rules.........................................................................................................................................................458

5.3.3.5

PM_PME Delivery State Machine.....................................................................................................................459

5.4 Native PCI Express Power Management Mechanisms ...................................................................................................460

5.4.1 Active State Power Management (ASPM) ...............................................................................................................460

5.4.1.1

L0s ASPM State.................................................................................................................................................462

5.4.1.1.1

Entry into the L0s State ...........................................................................................................................463

5.4.1.1.2

Exit from the L0s State.............................................................................................................................464

5.4.1.2

L1 ASPM State ..................................................................................................................................................464

5.4.1.2.1

ASPM Entry into the L1 State...................................................................................................................465

5.4.1.2.2

Exit from the L1 State ..............................................................................................................................471

5.4.1.3 ASPM Configuration.........................................................................................................................................474

5.4.1.3.1

Software Flow for Enabling or Disabling ASPM......................................................................................477

5.5 L1 PM Substates...............................................................................................................................................................478

5.5.1 Entry conditions for L1 PM Substates and L1.0 Requirements..............................................................................482

5.5.2 L1.1 Requirements...................................................................................................................................................483

5.5.2.1

Exit from L1.1 ...................................................................................................................................................483

5.5.3 L1.2 Requirements...................................................................................................................................................484

5.5.3.1

L1.2.Entry.........................................................................................................................................................485

5.5.3.2

L1.2.Idle............................................................................................................................................................486

5.5.3.3

L1.2.Exit............................................................................................................................................................486

5.5.3.3.1

Exit from L1.2 ...........................................................................................................................................487

5.5.4 L1 PM Substates Configuration...............................................................................................................................488

5.5.5 L1 PM Substates Timing Parameters ......................................................................................................................488

5.0-1.0-PUB — PCI Express® Base Specification Revision 5.0 Version 1.0

Page 95.5.6 Link Activation .........................................................................................................................................................489

5.6 Auxiliary Power Support..................................................................................................................................................490

5.7 Power Management System Messages and DLLPs ........................................................................................................490

5.8 PCI Function Power State Transitions.............................................................................................................................491

5.9 State Transition Recovery Time Requirements ..............................................................................................................492

5.10 PCI Bridges and Power Management..............................................................................................................................493

5.10.1 Switches and PCI Express to PCI Bridges................................................................................................................494

5.11 Power Management Events.............................................................................................................................................494

6. System Architecture ........................................................................................................................................................495

6.1 Interrupt and PME Support.............................................................................................................................................495

6.1.1 Rationale for PCI Express Interrupt Model..............................................................................................................495

6.1.2 PCI-compatible INTx Emulation..............................................................................................................................495

6.1.3 INTx Emulation Software Model..............................................................................................................................496

6.1.4 MSI and MSI-X Operation.........................................................................................................................................496

6.1.4.1

MSI Configuration............................................................................................................................................497

6.1.4.2

MSI-X Configuration.........................................................................................................................................498

6.1.4.3

Enabling Operation .........................................................................................................................................499

6.1.4.4

Sending Messages ...........................................................................................................................................500

6.1.4.5

Per-vector Masking and Function Masking.....................................................................................................500

6.1.4.6

Hardware/Software Synchronization .............................................................................................................501

6.1.4.7

Message Transaction Reception and Ordering Requirements ......................................................................503

6.1.5 PME Support............................................................................................................................................................503

6.1.6 Native PME Software Model ....................................................................................................................................503

6.1.7 Legacy PME Software Model ...................................................................................................................................504

6.1.8 Operating System Power Management Notification..............................................................................................504

6.1.9 PME Routing Between PCI Express and PCI Hierarchies........................................................................................504

6.2 Error Signaling and Logging............................................................................................................................................505

6.2.1 Scope........................................................................................................................................................................505

6.2.2 Error Classification ..................................................................................................................................................505

6.2.2.1 Correctable Errors ...........................................................................................................................................506

6.2.2.2

Uncorrectable Errors .......................................................................................................................................507

6.2.2.2.1

Fatal Errors...............................................................................................................................................507

6.2.2.2.2

Non-Fatal Errors.......................................................................................................................................507

6.2.3 Error Signaling .........................................................................................................................................................507

6.2.3.1 Completion Status...........................................................................................................................................507

6.2.3.2

Error Messages.................................................................................................................................................507

6.2.3.2.1

Uncorrectable Error Severity Programming (Advanced Error Reporting) ............................................509

6.2.3.2.2

Masking Individual Errors........................................................................................................................509

6.2.3.2.3

Error Pollution .........................................................................................................................................509

6.2.3.2.4

Advisory Non-Fatal Error Cases...............................................................................................................510

6.2.3.2.4.1

Completer Sending a Completion with UR/CA Status ...................................................................510

6.2.3.2.4.2

Intermediate Receiver.....................................................................................................................511

6.2.3.2.4.3

Ultimate PCI Express Receiver of a Poisoned TLP..........................................................................511

6.2.3.2.4.4

Requester with Completion Timeout .............................................................................................512

6.2.3.2.4.5

Receiver of an Unexpected Completion .........................................................................................512

6.2.3.2.5

Requester Receiving a Completion with UR/CA Status..........................................................................512

6.2.3.3

Error Forwarding (Data Poisoning).................................................................................................................512

6.2.3.4

Optional Error Checking..................................................................................................................................513

6.2.4 Error Logging ...........................................................................................................................................................513

5.0-1.0-PUB — PCI Express® Base Specification Revision 5.0 Version 1.0

Page 106.2.4.1

Root Complex Considerations (Advanced Error Reporting)..........................................................................514

6.2.4.1.1

Error Source Identification......................................................................................................................514

6.2.4.1.2

Interrupt Generation ...............................................................................................................................514

6.2.4.2

Multiple Error Handling (Advanced Error Reporting Capability)...................................................................515

6.2.4.3 Advisory Non-Fatal Error Logging...................................................................................................................516

6.2.4.4

TLP Prefix Logging ...........................................................................................................................................517

6.2.5 Sequence of Device Error Signaling and Logging Operations ...............................................................................517

6.2.6 Error Message Controls ...........................................................................................................................................519

6.2.7 Error Listing and Rules ............................................................................................................................................520

6.2.7.1 Conventional PCI Mapping..............................................................................................................................524

6.2.8 Virtual PCI Bridge Error Handling ...........................................................................................................................524

6.2.8.1

Error Message Forwarding and PCI Mapping for Bridge - Rules ....................................................................524

6.2.9 Internal Errors..........................................................................................................................................................525

6.2.10 Downstream Port Containment (DPC)....................................................................................................................526

6.2.10.1 DPC Interrupts .................................................................................................................................................529

6.2.10.2 DPC ERR_COR Signaling..................................................................................................................................529

6.2.10.3 Root Port Programmed I/O (RP PIO) Error Controls ......................................................................................530

6.2.10.4 Software Triggering of DPC .............................................................................................................................533

6.2.10.5 DL_Active ERR_COR Signaling ........................................................................................................................533

6.3 Virtual Channel Support..................................................................................................................................................534

6.3.1 Introduction and Scope...........................................................................................................................................534

6.3.2 TC/VC Mapping and Example Usage .......................................................................................................................534

6.3.3 VC Arbitration...........................................................................................................................................................536

6.3.3.1 Traffic Flow and Switch Arbitration Model .....................................................................................................537

6.3.3.2 VC Arbitration - Arbitration Between VCs .......................................................................................................540

6.3.3.2.1

Strict Priority Arbitration Model..............................................................................................................541

6.3.3.2.2

Round Robin Arbitration Model ..............................................................................................................541

6.3.3.3

Port Arbitration - Arbitration Within VC ..........................................................................................................542

6.3.3.4

Multi-Function Devices and Function Arbitration..........................................................................................542

6.3.4 Isochronous Support...............................................................................................................................................546

6.3.4.1

Rules for Software Configuration....................................................................................................................546

6.3.4.2

Rules for Requesters........................................................................................................................................547

6.3.4.3

Rules for Completers .......................................................................................................................................547

6.3.4.4

Rules for Switches and Root Complexes ........................................................................................................547

6.3.4.5

Rules for Multi-Function Devices ....................................................................................................................547

6.4 Device Synchronization...................................................................................................................................................548

6.5 Locked Transactions........................................................................................................................................................549

6.5.1 Introduction.............................................................................................................................................................549

6.5.2 Initiation and Propagation of Locked Transactions - Rules...................................................................................549

6.5.3 Switches and Lock - Rules .......................................................................................................................................550

6.5.4 PCI Express/PCI Bridges and Lock - Rules ..............................................................................................................551

6.5.5 Root Complex and Lock - Rules ..............................................................................................................................551

6.5.6 Legacy Endpoints ....................................................................................................................................................551

6.5.7 PCI Express Endpoints.............................................................................................................................................551

6.6 PCI Express Reset - Rules.................................................................................................................................................552

6.6.1 Conventional Reset .................................................................................................................................................552

6.6.2 Function Level Reset (FLR)......................................................................................................................................554

6.7 PCI Express Native Hot-Plug............................................................................................................................................558

6.7.1 Elements of Hot-Plug...............................................................................................................................................558

6.7.1.1

Indicators .........................................................................................................................................................558

5.0-1.0-PUB — PCI Express® Base Specification Revision 5.0 Version 1.0

Page 116.7.1.1.1

Attention Indicator ..................................................................................................................................559

6.7.1.1.2

Power Indicator .......................................................................................................................................560

6.7.1.2

Manually-operated Retention Latch (MRL).....................................................................................................560

6.7.1.3

MRL Sensor ......................................................................................................................................................560

6.7.1.4

Electromechanical Interlock...........................................................................................................................561

6.7.1.5 Attention Button..............................................................................................................................................561

6.7.1.6

Software User Interface...................................................................................................................................562

6.7.1.7

Slot Numbering................................................................................................................................................562

6.7.1.8

Power Controller..............................................................................................................................................562

6.7.2 Registers Grouped by Hot-Plug Element Association............................................................................................563

6.7.2.1 Attention Button Registers ..............................................................................................................................563

6.7.2.2 Attention Indicator Registers ..........................................................................................................................563

6.7.2.3

Power Indicator Registers ...............................................................................................................................563

6.7.2.4

Power Controller Registers..............................................................................................................................563

6.7.2.5

Presence Detect Registers ...............................................................................................................................564

6.7.2.6

MRL Sensor Registers ......................................................................................................................................564

6.7.2.7