实例介绍

【实例截图】

【核心代码】

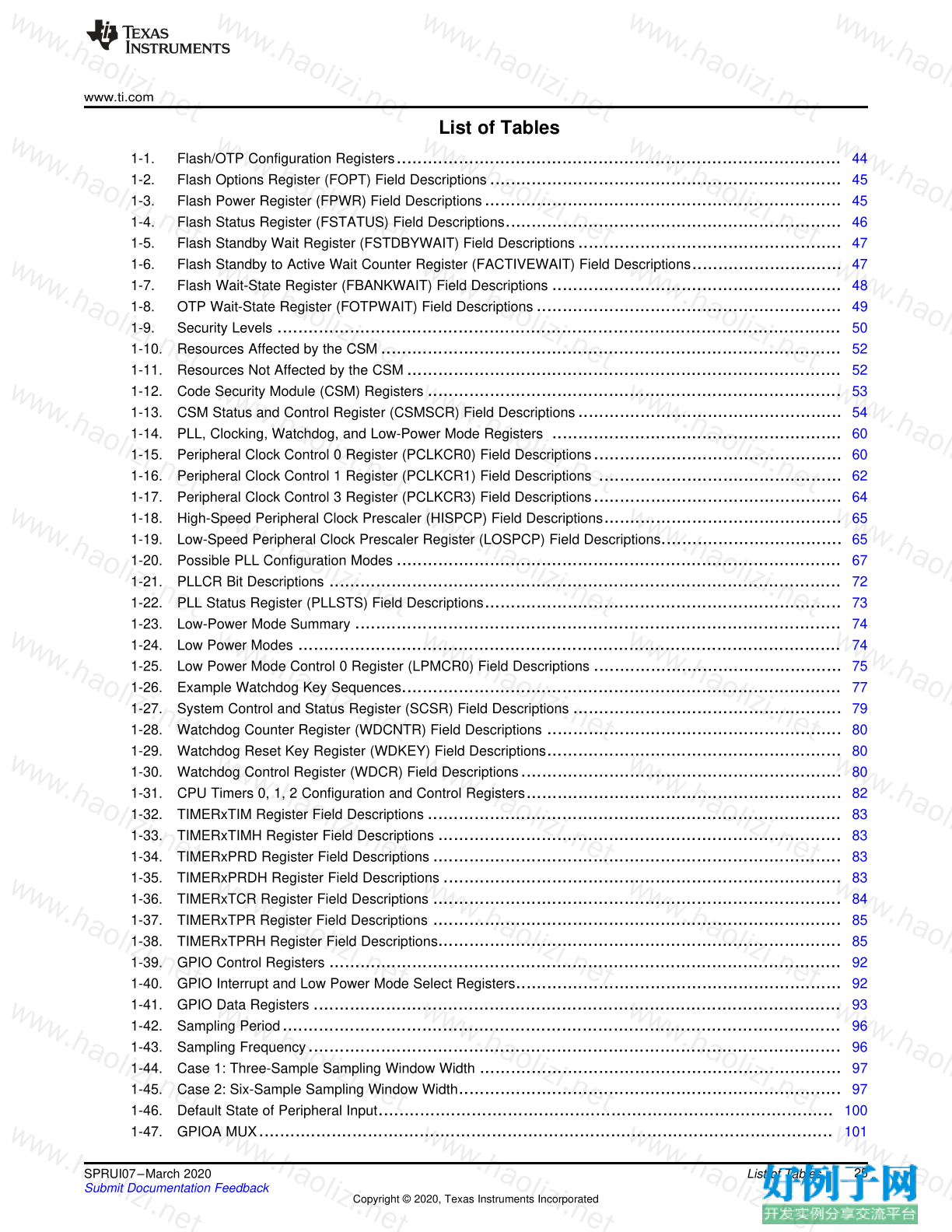

Contents

Preface ....................................................................................................................................... 36

1 System Control and Interrupts ............................................................................................. 38

1.1 Flash and OTP Memory Blocks .......................................................................................... 39

1.1.1 Flash Memory ...................................................................................................... 39

1.1.2 OTP Memory ....................................................................................................... 39

1.1.3 Flash and OTP Power Modes ................................................................................... 39

1.1.4 Flash and OTP Registers ........................................................................................ 44

1.2 Code Security Module (CSM) ............................................................................................. 49

1.2.1 Functional Description ............................................................................................ 49

1.2.2 CSM Impact on Other On-Chip Resources .................................................................... 52

1.2.3 Incorporating Code Security in User Applications ............................................................ 53

1.2.4 Do's and Don'ts to Protect Security Logic ...................................................................... 58

1.2.5 CSM Features - Summary ....................................................................................... 58

1.3 Clocking and System Control ............................................................................................. 59

1.3.1 Clocking ............................................................................................................ 59

1.3.2 OSC and PLL Block ............................................................................................... 66

1.3.3 Low-Power Modes Block ......................................................................................... 74

1.3.4 Watchdog Block ................................................................................................... 76

1.3.5 32-Bit CPU Timers 0/1/2 ......................................................................................... 81

1.4 General-Purpose Input/Output (GPIO) .................................................................................. 86

1.4.1 GPIO Module Overview .......................................................................................... 86

1.4.2 Configuration Overview ........................................................................................... 92

1.4.3 Digital General Purpose I/O Control ............................................................................ 93

1.4.4 Input Qualification ................................................................................................. 95

1.4.5 GPIO and Peripheral Multiplexing (MUX) ...................................................................... 99

1.4.6 Register Bit Definitions .......................................................................................... 104

1.5 Peripheral Frames ........................................................................................................ 129

1.5.1 Peripheral Frame Registers .................................................................................... 129

1.5.2 EALLOW-Protected Registers ................................................................................. 131

1.5.3 Device Emulation Registers .................................................................................... 135

1.5.4 Write-Followed-by-Read Protection ........................................................................... 137

1.6 Peripheral Interrupt Expansion (PIE) ................................................................................... 138

1.6.1 Overview of the PIE Controller ................................................................................. 138

1.6.2 Vector Table Mapping ........................................................................................... 141

1.6.3 Interrupt Sources ................................................................................................. 143

1.6.4 PIE Configuration and Control Registers ..................................................................... 153

1.6.5 External Interrupt Control Registers .......................................................................... 163

2 Boot ROM ........................................................................................................................ 166

2.1 Boot ROM Memory Map ................................................................................................. 167

2.1.1 On-Chip Boot ROM IQmath Tables ........................................................................... 167

2.1.2 CPU Vector Table ............................................................................................... 170

2.2 Bootloader Features ...................................................................................................... 171

2.2.1 Bootloader Functional Operation .............................................................................. 171

2.2.2 Bootloader Device Configuration .............................................................................. 173

2.2.3 PLL Multiplier and DIVSEL Selection ......................................................................... 173

www.ti.com

3 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Contents

2.2.4 Watchdog Module ............................................................................................... 174

2.2.5 Taking an ITRAP Interrupt ...................................................................................... 174

2.2.6 Internal Pullup Circuit ............................................................................................ 174

2.2.7 PIE Configuration ................................................................................................ 174

2.2.8 Reserved Memory ............................................................................................... 174

2.2.9 Bootloader Modes ............................................................................................... 175

2.2.10 Bootloader Data Stream Structure ........................................................................... 179

2.2.11 Basic Transfer Procedure ..................................................................................... 183

2.2.12 InitBoot Assembly Routine .................................................................................... 183

2.2.13 SelectBootMode Function .................................................................................... 184

2.2.14 ADC_cal Assembly Routine ................................................................................... 186

2.2.15 CopyData Function ............................................................................................. 187

2.2.16 McBSP_Boot Function ......................................................................................... 188

2.2.17 SCI_Boot Function ............................................................................................. 189

2.2.18 Parallel_Boot Function (GPIO) ................................................................................ 191

2.2.19 XINTF_Parallel_Boot Function ................................................................................ 197

2.2.20 SPI_Boot Function .............................................................................................. 204

2.2.21 I2C Boot Function .............................................................................................. 207

2.2.22 eCAN Boot Function ........................................................................................... 210

2.2.23 ExitBoot Assembly Routine ................................................................................... 212

2.3 Building the Boot Table .................................................................................................. 213

2.3.1 The C2000 Hex Utility ........................................................................................... 213

2.3.2 Example: Preparing a COFF File for eCAN Bootloading ................................................... 214

2.4 Bootloader Code Overview .............................................................................................. 217

2.4.1 Boot ROM Version and Checksum Information ............................................................. 217

2.4.2 Bootloader Code Revision History ............................................................................. 217

3 Enhanced Pulse Width Modulator (ePWM) Module ................................................................ 218

3.1 Introduction ................................................................................................................ 219

3.1.1 Submodule Overview ............................................................................................ 219

3.1.2 Register Mapping ................................................................................................ 222

3.2 ePWM Submodules ...................................................................................................... 224

3.2.1 Overview .......................................................................................................... 224

3.2.2 Time-Base (TB) Submodule .................................................................................... 228

3.2.3 Counter-Compare (CC) Submodule ........................................................................... 236

3.2.4 Action-Qualifier (AQ) Submodule .............................................................................. 242

3.2.5 Dead-Band Generator (DB) Submodule ...................................................................... 256

3.2.6 PWM-Chopper (PC) Submodule ............................................................................... 261

3.2.7 Trip-Zone (TZ) Submodule ..................................................................................... 265

3.2.8 Event-Trigger (ET) Submodule ................................................................................ 269

3.3 Applications to Power Topologies ...................................................................................... 274

3.3.1 Overview of Multiple Modules ................................................................................. 274

3.3.2 Key Configuration Capabilities ................................................................................. 274

3.3.3 Controlling Multiple Buck Converters With Independent Frequencies .................................... 275

3.3.4 Controlling Multiple Buck Converters With Same Frequencies ............................................ 279

3.3.5 Controlling Multiple Half H-Bridge (HHB) Converters ....................................................... 282

3.3.6 Controlling Dual 3-Phase Inverters for Motors (ACI and PMSM) .......................................... 284

3.3.7 Practical Applications Using Phase Control Between PWM Modules .................................... 288

3.3.8 Controlling a 3-Phase Interleaved DC/DC Converter ....................................................... 289

3.3.9 Controlling Zero Voltage Switched Full Bridge (ZVSFB) Converter ....................................... 293

3.4 Registers ................................................................................................................... 296

3.4.1 Time-Base Submodule Registers .............................................................................. 296

3.4.2 Counter-Compare Submodule Registers ..................................................................... 300

3.4.3 Action-Qualifier Submodule Registers ........................................................................ 304

www.ti.com

4 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Contents

3.4.4 Dead-Band Submodule Registers ............................................................................. 308

3.4.5 PWM-Chopper Submodule Control Register ................................................................. 311

3.4.6 Trip-Zone Submodule Control and Status Registers ........................................................ 313

3.4.7 Event-Trigger Submodule Registers .......................................................................... 320

3.4.8 Proper Interrupt Initialization Procedure ...................................................................... 325

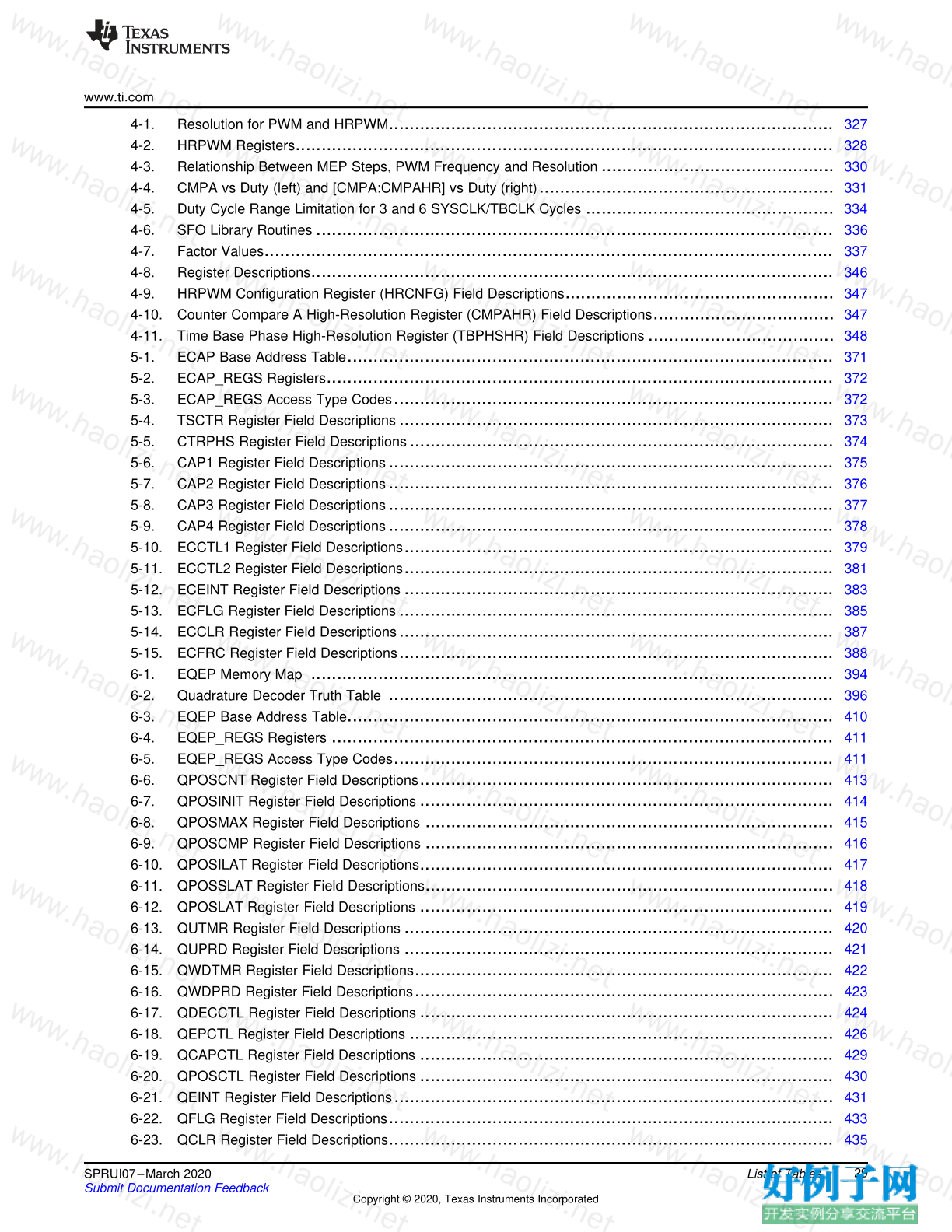

4 High-Resolution Pulse Width Modulator (HRPWM) ................................................................ 326

4.1 Introduction ................................................................................................................ 327

4.2 Operational Description of HRPWM .................................................................................... 328

4.2.1 Controlling the HRPWM Capabilities .......................................................................... 328

4.2.2 Configuring the HRPWM ........................................................................................ 330

4.2.3 Principle of Operation ........................................................................................... 330

4.2.4 Scale Factor Optimizing Software (SFO) ..................................................................... 335

4.2.5 HRPWM Examples Using Optimized Assembly Code ...................................................... 339

4.3 HRPWM Registers ........................................................................................................ 346

4.3.1 Register Summary ............................................................................................... 346

4.3.2 Registers and Field Descriptions .............................................................................. 347

5 Enhanced Capture (eCAP) ................................................................................................. 349

5.1 Introduction ................................................................................................................ 350

5.2 Features .................................................................................................................... 350

5.3 Description ................................................................................................................. 351

5.4 Capture and APWM Operating Mode .................................................................................. 353

5.5 Capture Mode Description ............................................................................................... 355

5.5.1 Event Prescaler .................................................................................................. 356

5.5.2 Edge Polarity Select and Qualifier ............................................................................. 356

5.5.3 Continuous/One-Shot Control .................................................................................. 358

5.5.4 32-Bit Counter and Phase Control ............................................................................. 359

5.5.5 CAP1-CAP4 Registers .......................................................................................... 359

5.5.6 Interrupt Control .................................................................................................. 359

5.5.7 Shadow Load and Lockout Control ............................................................................ 361

5.5.8 APWM Mode Operation ......................................................................................... 361

5.6 Application of the eCAP Module ....................................................................................... 364

5.6.1 Example 1 - Absolute Time-Stamp Operation Rising Edge Trigger ....................................... 364

5.6.2 Example 2 - Absolute Time-Stamp Operation Rising and Falling Edge Trigger ........................ 365

5.6.3 Example 3 - Time Difference (Delta) Operation Rising Edge Trigger ..................................... 366

5.6.4 Example 4 - Time Difference (Delta) Operation Rising and Falling Edge Trigger ...................... 367

5.7 Application of the APWM Mode ......................................................................................... 368

5.7.1 Example 1 - Simple PWM Generation (Independent Channel/s) .......................................... 368

5.7.2 Example 2 - Multi-channel PWM Generation With Phase Control ........................................ 368

5.8 eCAP Registers ........................................................................................................... 371

5.8.1 eCAP Base Addresses .......................................................................................... 371

5.8.2 ECAP_REGS Registers ......................................................................................... 372

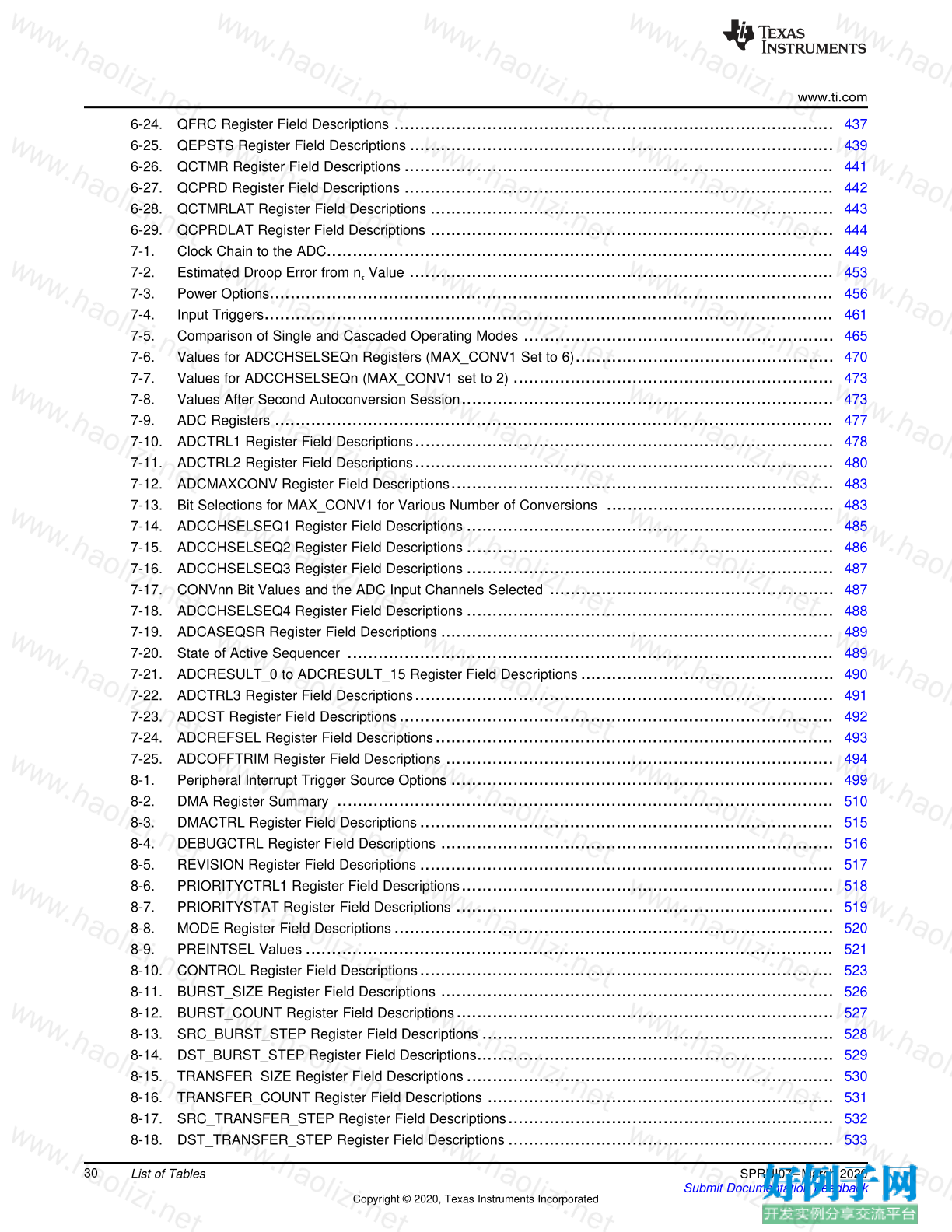

6 Enhanced Quadrature Encoder Pulse (eQEP) ....................................................................... 389

6.1 Introduction ................................................................................................................ 390

6.2 Configuring Device Pins ................................................................................................. 392

6.3 Description ................................................................................................................. 392

6.3.1 EQEP Inputs ...................................................................................................... 392

6.3.2 Functional Description ........................................................................................... 393

6.3.3 eQEP Memory Map ............................................................................................. 394

6.4 Quadrature Decoder Unit (QDU) ....................................................................................... 395

6.4.1 Position Counter Input Modes .................................................................................. 395

6.4.2 eQEP Input Polarity Selection .................................................................................. 398

6.4.3 Position-Compare Sync Output ................................................................................ 398

6.5 Position Counter and Control Unit (PCCU) ............................................................................ 398

www.ti.com

5 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Contents

6.5.1 Position Counter Operating Modes ............................................................................ 398

6.5.2 Position Counter Latch .......................................................................................... 400

6.5.3 Position Counter Initialization .................................................................................. 402

6.5.4 eQEP Position-compare Unit ................................................................................... 403

6.6 eQEP Edge Capture Unit ................................................................................................ 404

6.7 eQEP Watchdog .......................................................................................................... 408

6.8 Unit Timer Base ........................................................................................................... 409

6.9 eQEP Interrupt Structure ................................................................................................ 410

6.10 eQEP Registers ........................................................................................................... 410

6.10.1 eQEP Base Addresses ........................................................................................ 410

6.10.2 EQEP_REGS Registers ....................................................................................... 411

7 Analog-to-Digital Converter (ADC) ...................................................................................... 445

7.1 Features and Implementation ........................................................................................... 446

7.2 ADC Circuit ................................................................................................................ 448

7.2.1 ADC Clocking and Sample Rate Calculations ............................................................... 448

7.2.2 ADC Sample and Hold Circuit and Modeling ................................................................ 450

7.2.3 Reference Selection ............................................................................................. 455

7.2.4 Power-up Sequence and Power Modes ...................................................................... 456

7.2.5 Calibration and Offset Correction .............................................................................. 457

7.3 ADC Interface ............................................................................................................. 461

7.3.1 Input Trigger Description ....................................................................................... 461

7.3.2 Autoconversion Sequencer Principle of Operation .......................................................... 462

7.3.3 ADC Sequencer State Machine ................................................................................ 469

7.3.4 Interrupt Operation During Sequenced Conversions ....................................................... 474

7.3.5 ADC to DMA Interface .......................................................................................... 475

7.4 ADC Registers ............................................................................................................ 477

7.4.1 ADCTRL1 Register (Offset = 0h) [reset = 0h] ................................................................ 478

7.4.2 ADCTRL2 Register (Offset = 1h) [reset = 0h] ................................................................ 480

7.4.3 ADCMAXCONV Register (Offset = 2h) [reset = 0h] ......................................................... 483

7.4.4 ADCCHSELSEQ1 Register (Offset = 3h) [reset = 0h] ...................................................... 485

7.4.5 ADCCHSELSEQ2 Register (Offset = 4h) [reset = 0h] ...................................................... 486

7.4.6 ADCCHSELSEQ3 Register (Offset = 5h) [reset = 0h] ...................................................... 487

7.4.7 ADCCHSELSEQ4 Register (Offset = 6h) [reset = 0h] ...................................................... 488

7.4.8 ADCASEQSR Register (Offset = 7h) [reset = 0h] ........................................................... 489

7.4.9 ADCRESULT_0 to ADCRESULT_15 Register (Offset = 8h to 17h) [reset = 0h] ........................ 490

7.4.10 ADCTRL3 Register (Offset = 18h) [reset = 0h] ............................................................. 491

7.4.11 ADCST Register (Offset = 19h) [reset = 0h] ................................................................ 492

7.4.12 ADCREFSEL Register (Offset = 1Ch) [reset = 0h] ......................................................... 493

7.4.13 ADCOFFTRIM Register (Offset = 1Dh) [reset = 0h] ....................................................... 494

8 Direct Memory Access (DMA) Module ................................................................................ 495

8.1 Introduction ................................................................................................................ 496

8.2 Architecture ................................................................................................................ 497

8.2.1 Block Diagram .................................................................................................... 497

8.2.2 Peripheral Interrupt Event Trigger Sources .................................................................. 498

8.2.3 DMA Bus .......................................................................................................... 499

8.3 Pipeline Timing and Throughput ........................................................................................ 500

8.4 CPU Arbitration ........................................................................................................... 501

8.4.1 For the External Memory Interface (XINTF) Zones ......................................................... 501

8.4.2 For All Other Peripherals/Memories ........................................................................... 502

8.5 Channel Priority ........................................................................................................... 502

8.5.1 Round-Robin Mode .............................................................................................. 502

8.5.2 Channel 1 High Priority Mode .................................................................................. 503

8.6 Address Pointer and Transfer Control ................................................................................. 503

www.ti.com

6 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Contents

8.7 ADC Sync Feature ........................................................................................................ 508

8.8 Overrun Detection Feature .............................................................................................. 510

8.9 Register Descriptions ..................................................................................................... 510

8.9.1 DMACTRL Register (Offset = 1000h) [reset = 0h] .......................................................... 515

8.9.2 DEBUGCTRL Register (Offset = 1001h) [reset = 0h] ....................................................... 516

8.9.3 REVISION Register (Offset = 1002h) [reset = 0h] ........................................................... 517

8.9.4 PRIORITYCTRL1 Register (Offset = 1004h) [reset = 0h] .................................................. 518

8.9.5 PRIORITYSTAT Register (Offset = 1006h) [reset = 0h] .................................................... 519

8.9.6 MODE Register (Offset = 1020h [i * E3h]) [reset = 0h] ................................................... 520

8.9.7 CONTROL Register (Offset = 1021h [i * E3h]) [reset = 0h] ............................................. 523

8.9.8 BURST_SIZE Register (Offset = 1022h [i * E3h]) [reset = 0h] .......................................... 526

8.9.9 BURST_COUNT Register (Offset = 1023h [i * E3h]) [reset = 0h] ...................................... 527

8.9.10 SRC_BURST_STEP Register (Offset = 1024h [i * E3h]) [reset = 0h] ................................. 528

8.9.11 DST_BURST_STEP Register (Offset = 1025h [i * E3h]) [reset = 0h] ................................. 529

8.9.12 TRANSFER_SIZE Register (Offset = 1026h [i * E3h]) [reset = 0h] .................................... 530

8.9.13 TRANSFER_COUNT Register (Offset = 1027h [i * E3h]) [reset = 0h] ................................ 531

8.9.14 SRC_TRANSFER_STEP Register (Offset = 1028h [i * E3h]) [reset = 0h] ........................... 532

8.9.15 DST_TRANSFER_STEP Register (Offset = 1029h [i * E3h]) [reset = 0h] ............................ 533

8.9.16 SRC_WRAP_SIZE Register (Offset = 102Ah [i * E3h]) [reset = 0h] .................................. 534

8.9.17 SRC_WRAP_COUNT Register (Offset = 102Bh [i * E3h]) [reset = 0h] ............................... 535

8.9.18 SRC_WRAP_STEP Register (Offset = 102Ch [i * E3h]) [reset = 0h] ................................. 536

8.9.19 DST_WRAP_SIZE Register (Offset = 102Dh [i * E3h]) [reset = 0h] ................................... 537

8.9.20 DST_WRAP_COUNT Register (Offset = 102Eh [i * E3h]) [reset = 0h] ............................... 538

8.9.21 DST_WRAP_STEP Register (Offset = 102Fh [i * E3h]) [reset = 0h] .................................. 539

8.9.22 SRC_BEG_ADDR_SHADOW Register (Offset = 1030h [i * E3h]) [reset = 0h] ...................... 540

8.9.23 SRC_ADDR_SHADOW Register (Offset = 1032h [i * E3h]) [reset = 0h] ............................. 541

8.9.24 SRC_BEG_ADDR Register (Offset = 1034h [i * E3h]) [reset = 0h] .................................... 542

8.9.25 SRC_ADDR Register (Offset = 1036h [i * E3h]) [reset = 0h] ........................................... 543

8.9.26 DST_BEG_ADDR_SHADOW Register (Offset = 1038h [i * E3h]) [reset = 0h] ...................... 544

8.9.27 DST_ADDR_SHADOW Register (Offset = 103Ah [i * E3h]) [reset = 0h] ............................. 545

8.9.28 DST_BEG_ADDR Register (Offset = 103Ch [i * E3h]) [reset = 0h] ................................... 546

8.9.29 DST_ADDR Register (Offset = 103Eh [i * E3h]) [reset = 0h] ........................................... 547

9 Serial Peripheral Interface (SPI) .......................................................................................... 548

9.1 Introduction ................................................................................................................ 549

9.1.1 Features ........................................................................................................... 549

9.1.2 Block Diagram .................................................................................................... 550

9.2 System-Level Integration ................................................................................................ 550

9.2.1 SPI Module Signals .............................................................................................. 550

9.2.2 Configuring Device Pins ........................................................................................ 551

9.2.3 SPI Interrupts ..................................................................................................... 551

9.3 SPI Operation ............................................................................................................. 553

9.3.1 Introduction to Operation ....................................................................................... 553

9.3.2 Master Mode ..................................................................................................... 555

9.3.3 Slave Mode ....................................................................................................... 555

9.3.4 Data Format ...................................................................................................... 556

9.3.5 Baud Rate Selection ............................................................................................ 557

9.3.6 SPI Clocking Schemes .......................................................................................... 558

9.3.7 SPI FIFO Description ............................................................................................ 559

9.4 Programming Procedure ................................................................................................. 560

9.4.1 Initialization Upon Reset ........................................................................................ 560

9.4.2 Configuring the SPI .............................................................................................. 560

9.4.3 Data Transfer Example ......................................................................................... 561

9.5 SPI Registers .............................................................................................................. 562

www.ti.com

7 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Contents

9.5.1 SPI Base Addresses ............................................................................................ 562

9.5.2 SPI_REGS Registers ............................................................................................ 563

10 Serial Communications Interface (SCI) ................................................................................ 581

10.1 Introduction ................................................................................................................ 582

10.2 Architecture ................................................................................................................ 584

10.3 SCI Module Signal Summary ........................................................................................... 584

10.4 Configuring Device Pins ................................................................................................. 584

10.5 Multiprocessor and Asynchronous Communication Modes ......................................................... 584

10.6 SCI Programmable Data Format ....................................................................................... 585

10.7 SCI Multiprocessor Communication .................................................................................... 585

10.7.1 Recognizing the Address Byte ................................................................................ 586

10.7.2 Controlling the SCI TX and RX Features .................................................................... 586

10.7.3 Receipt Sequence .............................................................................................. 586

10.8 Idle-Line Multiprocessor Mode .......................................................................................... 586

10.8.1 Idle-Line Mode Steps ........................................................................................... 587

10.8.2 Block Start Signal ............................................................................................... 588

10.8.3 Wake-UP Temporary (WUT) Flag ............................................................................ 588

10.8.4 Receiver Operation ............................................................................................. 588

10.9 Address-Bit Multiprocessor Mode ...................................................................................... 588

10.9.1 Sending an Address ............................................................................................ 588

10.10 SCI Communication Format ............................................................................................. 589

10.10.1 Receiver Signals in Communication Modes ............................................................... 590

10.10.2 Transmitter Signals in Communication Modes ............................................................ 590

10.11 SCI Port Interrupts ....................................................................................................... 591

10.12 SCI Baud Rate Calculations ............................................................................................ 592

10.13 SCI Enhanced Features ................................................................................................. 592

10.13.1 SCI FIFO Description ......................................................................................... 592

10.13.2 SCI Auto-Baud ................................................................................................. 594

10.13.3 Autobaud-Detect Sequence ................................................................................. 594

10.14 SCI Registers ............................................................................................................. 595

10.14.1 SCI Base Addresses .......................................................................................... 595

10.14.2 SCI_REGS Registers ......................................................................................... 596

11 Inter-Integrated Circuit Module (I2C) ................................................................................... 616

11.1 Introduction ................................................................................................................ 617

11.1.1 Features .......................................................................................................... 617

11.1.2 Features Not Supported ....................................................................................... 618

11.1.3 Functional Overview ............................................................................................ 618

11.1.4 Clock Generation ............................................................................................... 619

11.1.5 I2C Clock Divider Registers (I2CCLKL and I2CCLKH) .................................................... 620

11.2 Configuring Device Pins ................................................................................................. 620

11.3 I2C Module Operational Details ......................................................................................... 621

11.3.1 Input and Output Voltage Levels ............................................................................. 621

11.3.2 Data Validity ..................................................................................................... 621

11.3.3 Operating Modes ............................................................................................... 621

11.3.4 I2C Module START and STOP Conditions .................................................................. 622

11.3.5 Serial Data Formats ............................................................................................ 623

11.3.6 NACK Bit Generation ........................................................................................... 625

11.3.7 Clock Synchronization ......................................................................................... 626

11.3.8 Arbitration ........................................................................................................ 626

11.3.9 Digital Loopback Mode ......................................................................................... 627

11.4 Interrupt Requests Generated by the I2C Module .................................................................... 628

11.4.1 Basic I2C Interrupt Requests .................................................................................. 628

11.4.2 I2C FIFO Interrupts ............................................................................................. 630

www.ti.com

8 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Contents

11.5 Resetting or Disabling the I2C Module ................................................................................. 631

11.6 I2C Registers .............................................................................................................. 632

11.6.1 I2C Base Addresses ........................................................................................... 632

11.6.2 I2C_REGS Registers ........................................................................................... 633

12 Multichannel Buffered Serial Port (McBSP) .......................................................................... 657

12.1 Overview ................................................................................................................... 658

12.1.1 Features of the McBSPs ....................................................................................... 658

12.1.2 McBSP Pins/Signals ............................................................................................ 659

12.2 Configuring Device Pins ................................................................................................. 660

12.3 McBSP Operation ......................................................................................................... 660

12.3.1 Data Transfer Process of McBSPs ........................................................................... 661

12.3.2 Companding (Compressing and Expanding) Data ......................................................... 662

12.3.3 Clocking and Framing Data ................................................................................... 663

12.3.4 Frame Phases ................................................................................................... 666

12.3.5 McBSP Reception .............................................................................................. 668

12.3.6 McBSP Transmission .......................................................................................... 669

12.3.7 Interrupts and DMA Events Generated by a McBSP ...................................................... 670

12.4 McBSP Sample Rate Generator ........................................................................................ 670

12.4.1 Block Diagram ................................................................................................... 671

12.4.2 Frame Synchronization Generation in the Sample Rate Generator ..................................... 674

12.4.3 Synchronizing Sample Rate Generator Outputs to an External Clock .................................. 674

12.4.4 Reset and Initialization Procedure for the Sample Rate Generator ...................................... 676

12.5 McBSP Exception/Error Conditions .................................................................................... 677

12.5.1 Types of Errors .................................................................................................. 677

12.5.2 Overrun in the Receiver ........................................................................................ 677

12.5.3 Unexpected Receive Frame-Synchronization Pulse ....................................................... 679

12.5.4 Overwrite in the Transmitter ................................................................................... 681

12.5.5 Underflow in the Transmitter .................................................................................. 682

12.5.6 Unexpected Transmit Frame-Synchronization Pulse ...................................................... 683

12.6 Multichannel Selection Modes .......................................................................................... 685

12.6.1 Channels, Blocks, and Partitions ............................................................................. 685

12.6.2 Multichannel Selection ......................................................................................... 686

12.6.3 Configuring a Frame for Multichannel Selection ............................................................ 686

12.6.4 Using Two Partitions ........................................................................................... 686

12.6.5 Using Eight Partitions .......................................................................................... 688

12.6.6 Receive Multichannel Selection Mode ....................................................................... 689

12.6.7 Transmit Multichannel Selection Modes ..................................................................... 689

12.6.8 Using Interrupts Between Block Transfers .................................................................. 691

12.7 SPI Operation Using the Clock Stop Mode ............................................................................ 692

12.7.1 SPI Protocol ..................................................................................................... 692

12.7.2 Clock Stop Mode ................................................................................................ 693

12.7.3 Enable and Configure the Clock Stop Mode ................................................................ 693

12.7.4 Clock Stop Mode Timing Diagrams .......................................................................... 694

12.7.5 Procedure for Configuring a McBSP for SPI Operation ................................................... 696

12.7.6 McBSP as the SPI Master ..................................................................................... 696

12.7.7 McBSP as an SPI Slave ....................................................................................... 698

12.8 Receiver Configuration ................................................................................................... 699

12.8.1 Programming the McBSP Registers for the Desired Receiver Operation ............................... 699

12.8.2 Resetting and Enabling the Receiver ........................................................................ 700

12.8.3 Set the Receiver Pins to Operate as McBSP Pins ......................................................... 700

12.8.4 Digital Loopback Mode ......................................................................................... 701

12.8.5 Clock Stop Mode ................................................................................................ 701

12.8.6 Receive Multichannel Selection Mode ....................................................................... 702

www.ti.com

9 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Contents

12.8.7 Receive Frame Phases ........................................................................................ 702

12.8.8 Receive Word Length(s) ....................................................................................... 703

12.8.9 Receive Frame Length ......................................................................................... 703

12.8.10 Receive Frame-Synchronization Ignore Function ......................................................... 704

12.8.11 Receive Companding Mode ................................................................................. 705

12.8.12 Receive Data Delay ........................................................................................... 706

12.8.13 Receive Sign-Extension and Justification Mode .......................................................... 708

12.8.14 Receive Interrupt Mode ....................................................................................... 709

12.8.15 Receive Frame-Synchronization Mode ..................................................................... 709

12.8.16 Receive Frame-Synchronization Polarity .................................................................. 711

12.8.17 Receive Clock Mode .......................................................................................... 713

12.8.18 Receive Clock Polarity ........................................................................................ 714

12.8.19 SRG Clock Divide-Down Value ............................................................................. 716

12.8.20 SRG Clock Synchronization Mode .......................................................................... 716

12.8.21 SRG Clock Mode (Choose an Input Clock) ................................................................ 717

12.8.22 SRG Input Clock Polarity ..................................................................................... 718

12.9 Transmitter Configuration ................................................................................................ 718

12.9.1 Programming the McBSP Registers for the Desired Transmitter Operation ............................ 718

12.9.2 Resetting and Enabling the Transmitter ..................................................................... 719

12.9.3 Set the Transmitter Pins to Operate as McBSP Pins ...................................................... 720

12.9.4 Digital Loopback Mode ......................................................................................... 720

12.9.5 Clock Stop Mode ................................................................................................ 720

12.9.6 Transmit Multichannel Selection Mode ...................................................................... 721

12.9.7 XCERs Used in the Transmit Multichannel Selection Mode .............................................. 722

12.9.8 Transmit Frame Phases ....................................................................................... 725

12.9.9 Transmit Word Length(s) ...................................................................................... 725

12.9.10 Transmit Frame Length ....................................................................................... 726

12.9.11 Enable/Disable the Transmit Frame-Synchronization Ignore Function ................................ 727

12.9.12 Transmit Companding Mode ................................................................................. 728

12.9.13 Transmit Data Delay .......................................................................................... 729

12.9.14 Transmit DXENA Mode ....................................................................................... 731

12.9.15 Transmit Interrupt Mode ...................................................................................... 731

12.9.16 Transmit Frame-Synchronization Mode .................................................................... 732

12.9.17 Transmit Frame-Synchronization Polarity .................................................................. 733

12.9.18 SRG Frame-Synchronization Period and Pulse Width ................................................... 734

12.9.19 Transmit Clock Mode ......................................................................................... 735

12.9.20 Transmit Clock Polarity ....................................................................................... 735

12.10 Emulation and Reset Considerations .................................................................................. 736

12.10.1 McBSP Emulation Mode ..................................................................................... 737

12.10.2 Resetting and Initializing McBSPs .......................................................................... 737

12.11 Data Packing Examples ................................................................................................. 739

12.11.1 Data Packing Using Frame Length and Word Length .................................................... 739

12.11.2 Data Packing Using Word Length and the Frame-Synchronization Ignore Function ................ 741

12.12 Interrupt Generation ...................................................................................................... 741

12.12.1 McBSP Receive Interrupt Generation ...................................................................... 742

12.12.2 McBSP Transmit Interrupt Generation ..................................................................... 742

12.12.3 Error Flags .................................................................................................... 743

12.13 McBSP Modes ............................................................................................................ 743

12.14 Special Case: External Device is the Transmit Frame Master ..................................................... 744

12.15 McBSP Registers ........................................................................................................ 746

12.15.1 McBSP Base Addresses ..................................................................................... 746

12.15.2 Data Receive Registers (DRR[1,2]) ......................................................................... 747

12.15.3 Data Transmit Registers (DXR[1,2]) ........................................................................ 747

www.ti.com

10 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Contents

12.15.4 Serial Port Control Registers (SPCR[1,2]) ................................................................. 748

12.15.5 Receive Control Registers (RCR[1, 2]) .................................................................... 753

12.15.6 Transmit Control Registers (XCR1 and XCR2) ........................................................... 755

12.15.7 Sample Rate Generator Registers (SRGR1 and SRGR2) ............................................... 758

12.15.8 Multichannel Control Registers (MCR[1,2]) ................................................................ 760

12.15.9 Pin Control Register (PCR) .................................................................................. 765

12.15.10 Receive Channel Enable Registers (RCERA, RCERB, RCERC, RCERD, RCERE, RCERF,

RCERG, RCERH) ............................................................................................... 767

12.15.11 Transmit Channel Enable Registers (XCERA, XCERB, XCERC, XCERD, XCERE, XCERF,

XCERG, XCERH) ................................................................................................ 769

12.15.12 XCERs Used in a Transmit Multichannel Selection Mode ............................................. 770

12.15.13 McBSP Interrupt Enable Register ......................................................................... 771

12.16 Register to Driverlib Function Mapping ................................................................................ 772

13 Controller Area Network (CAN) ........................................................................................... 773

13.1 CAN Overview ............................................................................................................. 774

13.1.1 Features .......................................................................................................... 774

13.1.2 Block Diagram ................................................................................................... 774

13.2 eCAN Compatibility With Other TI CAN Modules .................................................................... 775

13.3 The CAN Network and Module ......................................................................................... 776

13.3.1 CAN Protocol Overview ........................................................................................ 776

13.4 eCAN Controller Overview ............................................................................................... 778

13.4.1 Standard CAN Controller (SCC) Mode ...................................................................... 778

13.4.2 Memory Map .................................................................................................... 779

13.5 Message Objects ......................................................................................................... 782

13.6 Message Mailbox ......................................................................................................... 782

13.6.1 Transmit Mailbox ................................................................................................ 786

13.6.2 Receive Mailbox ................................................................................................ 787

13.6.3 CAN Module Operation in Normal Configuration ........................................................... 787

13.7 eCAN Configuration ...................................................................................................... 787

13.7.1 CAN Module Initialization ...................................................................................... 787

13.7.2 Steps to Configure eCAN ...................................................................................... 791

13.7.3 Handling of Remote Frame Mailboxes ....................................................................... 793

13.7.4 Interrupts ......................................................................................................... 794

13.7.5 CAN Power-Down Mode ....................................................................................... 799

13.8 eCAN Registers ........................................................................................................... 801

13.8.1 Mailbox Enable Register (CANME) .......................................................................... 801

13.8.2 Mailbox-Direction Register (CANMD) ........................................................................ 802

13.8.3 Transmission-Request Set Register (CANTRS) ............................................................ 803

13.8.4 Transmission-Request-Reset Register (CANTRR) ......................................................... 804

13.8.5 Transmission-Acknowledge Register (CANTA) ............................................................. 804

13.8.6 Abort-Acknowledge Register (CANAA) ...................................................................... 805

13.8.7 Received-Message-Pending Register (CANRMP) ......................................................... 805

13.8.8 Received-Message-Lost Register (CANRML) .............................................................. 806

13.8.9 Remote-Frame-Pending Register (CANRFP) ............................................................... 806

13.8.10 Global Acceptance Mask Register (CANGAM) ........................................................... 808

13.8.11 Master Control Register (CANMC) .......................................................................... 809

13.8.12 Bit-Timing Configuration Register (CANBTC) ............................................................. 812

13.8.13 Error and Status Register (CANES) ........................................................................ 814

13.8.14 CAN Error Counter Registers (CANTEC/CANREC) ...................................................... 816

13.8.15 Interrupt Registers ............................................................................................ 817

13.8.16 Overwrite Protection Control Register (CANOPC) ........................................................ 822

13.8.17 eCAN I/O Control Registers (CANTIOC, CANRIOC) ..................................................... 823

13.8.18 Timer Management Unit ...................................................................................... 825

13.8.19 Mailbox Layout ................................................................................................ 829

www.ti.com

11 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Contents

13.9 Message Data Registers (CANMDL, CANMDH) ..................................................................... 831

13.10 Acceptance Filter ......................................................................................................... 832

13.10.1 Local-Acceptance Masks (CANLAM) ....................................................................... 832

14 External Interface (XINTF) .................................................................................................. 834

14.1 Functional Description .................................................................................................... 835

14.1.1 Differences from the TMS320x281x XINTF ................................................................. 835

14.1.2 Differences from the TMS320x2834x XINTF ............................................................... 836

14.1.3 Accessing XINTF Zones ....................................................................................... 836

14.1.4 Write-Followed-by-Read Pipeline Protection ................................................................ 837

14.2 XINTF Configuration Overview .......................................................................................... 838

14.2.1 Procedure to Change the XINTF Configuration and Timing Registers .................................. 838

14.2.2 XINTF Clocking ................................................................................................. 839

14.2.3 Write Buffer ...................................................................................................... 840

14.2.4 XINTF Access Lead/Active/Trail Wait-State Timing Per Zone ............................................ 840

14.2.5 XREADY Sampling For Each Zone .......................................................................... 841

14.2.6 Bank Switching .................................................................................................. 841

14.2.7 Zone Data Bus Width .......................................................................................... 842

14.3 External DMA Support (XHOLD, XHOLDA) ........................................................................... 844

14.4 Configuring Lead, Active, and Trail Wait States ...................................................................... 845

14.4.1 USEREADY = 0 ................................................................................................. 846

14.4.2 Synchronous Mode (USEREADY = 1, READYMODE = 0) ............................................... 846

14.4.3 Asynchronous Mode (USEREADY = 1, READYMODE = 1) .............................................. 847

14.5 Configuring XBANK Cycles .............................................................................................. 850

14.6 XINTF Registers .......................................................................................................... 851

14.6.1 XRESET Register (Offset = 83Dh) [reset = 0h] ............................................................. 852

14.6.2 XTIMING0 Register (Offset = B20h) [reset = 41D2A5h] ................................................... 853

14.6.3 XTIMING6 Register (Offset = B2Ch) [reset = 41D2A5h] .................................................. 855

14.6.4 XTIMING7 Register (Offset = B2Eh) [reset = 41D2A5h] .................................................. 857

14.6.5 XBANK Register (Offset = B38h) [reset = 9h] .............................................................. 861

14.6.6 XREVISION Register (Offset = B3Ah) [reset = X] .......................................................... 862

14.7 Signal Descriptions ....................................................................................................... 863

14.8 Waveforms ................................................................................................................. 864

www.ti.com

12 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

List of Figures

List of Figures

1-1. Flash Power Mode State Diagram ....................................................................................... 40

1-2. Flash Pipeline ............................................................................................................... 42

1-3. Flash Configuration Access Flow Diagram ............................................................................. 43

1-4. Flash Options Register (FOPT) .......................................................................................... 45

1-5. Flash Power Register (FPWR) ........................................................................................... 45

1-6. Flash Status Register (FSTATUS) ....................................................................................... 46

1-7. Flash Standby Wait Register (FSTDBYWAIT) ......................................................................... 47

1-8. Flash Standby to Active Wait Counter Register (FACTIVEWAIT) .................................................. 47

1-9. Flash Wait-State Register (FBANKWAIT) .............................................................................. 48

1-10. OTP Wait-State Register (FOTPWAIT) ................................................................................. 49

1-11. CSM Status and Control Register (CSMSCR) ......................................................................... 54

1-12. Password Match Flow (PMF) ............................................................................................ 55

1-13. Clock and Reset Domains ................................................................................................ 59

1-14. Peripheral Clock Control 0 Register (PCLKCR0) ...................................................................... 60

1-15. Peripheral Clock Control 1 Register (PCLKCR1) ..................................................................... 62

1-16. Peripheral Clock Control 3 Register (PCLKCR3) ...................................................................... 64

1-17. High-Speed Peripheral Clock Prescaler (HISPCP) Register ......................................................... 65

1-18. Low-Speed Peripheral Clock Prescaler Register (LOSPCP) ......................................................... 65

1-19. OSC and PLL Block ........................................................................................................ 66

1-20. Oscillator Fail-Detection Logic Diagram ................................................................................. 67

1-21. XCLKOUT Generation ..................................................................................................... 69

1-22. PLLCR Change Procedure Flow Chart .................................................................................. 71

1-23. PLLCR Register Layout ................................................................................................... 72

1-24. PLL Status Register (PLLSTS) ........................................................................................... 72

1-25. Low Power Mode Control 0 Register (LPMCR0) ....................................................................... 75

1-26. Watchdog Module .......................................................................................................... 76

1-27. System Control and Status Register (SCSR) .......................................................................... 79

1-28. Watchdog Counter Register (WDCNTR) ................................................................................ 80

1-29. Watchdog Reset Key Register (WDKEY) ............................................................................... 80

1-30. Watchdog Control Register (WDCR) .................................................................................... 80

1-31. CPU Timers ................................................................................................................. 81

1-32. CPU-Timer Interrupt Signals and Output Signal ....................................................................... 82

1-33. TIMERxTIM Register (x = 0, 1, 2) ........................................................................................ 83

1-34. TIMERxTIMH Register (x = 0, 1, 2) ...................................................................................... 83

1-35. TIMERxPRD Register (x = 0, 1, 2) ....................................................................................... 83

1-36. TIMERxPRDH Register (x = 0, 1, 2) ..................................................................................... 83

1-37. TIMERxTCR Register (x = 0, 1, 2) ....................................................................................... 84

1-38. TIMERxTPR Register (x = 0, 1, 2) ....................................................................................... 85

1-39. TIMERxTPRH Register (x = 0, 1, 2) .................................................................................... 85

1-40. GPIO0 to GPIO27 Multiplexing Diagram ................................................................................ 87

1-41. GPIO28 to GPIO31 Multiplexing Diagram (Peripheral 2 and Peripheral 3 Outputs Merged) .................... 88

1-42. GPIO32, GPIO33 Multiplexing Diagram ................................................................................. 89

1-43. GPIO34 to GPIO63 Multiplexing Diagram (Peripheral 2 and Peripheral 3 Outputs Merged) .................... 90

1-44. GPIO64 to GPIO79 Multiplexing Diagram (Minimal GPIOs Without Qualification) ................................ 91

1-45. Input Qualification Using a Sampling Window .......................................................................... 95

1-46. Input Qualifier Clock Cycles .............................................................................................. 98

1-47. GPIO Port A MUX 1 (GPAMUX1) Register ........................................................................... 104

www.ti.com

13 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

List of Figures

1-48. GPIO Port A MUX 2 (GPAMUX2) Register ........................................................................... 106

1-49. GPIO Port B MUX 1 (GPBMUX1) Register ........................................................................... 108

1-50. GPIO Port B MUX 2 (GPBMUX2) Register ........................................................................... 110

1-51. GPIO Port C MUX 1 (GPCMUX1) Register ........................................................................... 112

1-52. GPIO Port C MUX 2 (GPCMUX2) Register ........................................................................... 113

1-53. GPIO Port A Qualification Control (GPACTRL) Register ........................................................... 115

1-54. GPIO Port B Qualification Control (GPBCTRL) Register ........................................................... 116

1-55. GPIO Port A Qualification Select 1 (GPAQSEL1) Register ......................................................... 117

1-56. GPIO Port A Qualification Select 2 (GPAQSEL2) Register ......................................................... 117

1-57. GPIO Port B Qualification Select 1 (GPBQSEL1) Register ......................................................... 118

1-58. GPIO Port B Qualification Select 2 (GPBQSEL2) Register ......................................................... 118

1-59. GPIO Port A Direction (GPADIR) Register ........................................................................... 119

1-60. GPIO Port B Direction (GPBDIR) Register ........................................................................... 119

1-61. GPIO Port C Direction (GPCDIR) Register ........................................................................... 120

1-62. GPIO Port A Pullup Disable (GPAPUD) Registers .................................................................. 120

1-63. GPIO Port B Pullup Disable (GPBPUD) Registers .................................................................. 121

1-64. GPIO Port C Pullup Disable (GPCPUD) Registers .................................................................. 121

1-65. GPIO Port A Data (GPADAT) Register ............................................................................... 122

1-66. GPIO Port B Data (GPBDAT) Register ............................................................................... 122

1-67. GPIO Port C Data (GPCDAT) Register ............................................................................... 123

1-68. GPIO Port A Set, Clear and Toggle (GPASET, GPACLEAR, GPATOGGLE) Registers ....................... 124

1-69. GPIO Port B Set, Clear and Toggle (GPBSET, GPBCLEAR, GPBTOGGLE) Registers ....................... 125

1-70. GPIO Port C Set, Clear and Toggle (GPCSET, GPCCLEAR, GPCTOGGLE) Registers ...................... 126

1-71. GPIO XINTn, XNMI Interrupt Select (GPIOXINTnSEL, GPIOXNMISEL) Registers ............................. 127

1-72. GPIO Low Power Mode Wakeup Select (GPIOLPMSEL) Register ................................................ 128

1-73. MAPCNF Register (0x702E) ............................................................................................ 130

1-74. Device Configuration (DEVICECNF) Register ........................................................................ 135

1-75. Part ID Register ........................................................................................................... 136

1-76. CLASSID Register ........................................................................................................ 136

1-77. REVID Register ........................................................................................................... 136

1-78. Overview: Multiplexing of Interrupts Using the PIE Block ........................................................... 139

1-79. Typical PIE/CPU Interrupt Response - INTx.y ........................................................................ 140

1-80. Reset Flow Diagram ...................................................................................................... 142

1-81. PIE Interrupt Sources and External Interrupts XINT1/XINT2 ....................................................... 143

1-82. PIE Interrupt Sources and External Interrupts (XINT3 – XINT7) ................................................... 144

1-83. Multiplexed Interrupt Request Flow Diagram ......................................................................... 147

1-84. PIE Control Register (PIECTRL) (Address CE0) ..................................................................... 154

1-85. PIE Interrupt Acknowledge Register (PIEACK) (Address CE1) .................................................... 154

1-86. PIE Interrupt Enable Register (PIEIERx, x = 1 to 12) ................................................................ 155

1-87. PIE Interrupt Flag Register (PIEIFRx, x = 1 to 12) ................................................................... 156

1-88. Interrupt Flag Register (IFR) — CPU Register ....................................................................... 157

1-89. Interrupt Enable Register (IER) — CPU Register .................................................................... 159

1-90. Debug Interrupt Enable Register (DBGIER) — CPU Register ...................................................... 161

1-91. External Interrupt n Control Register (XINTnCR) ..................................................................... 163

1-92. External NMI Interrupt Control Register (XNMICR) — Address 7077h ............................................ 163

1-93. External Interrupt 1 Counter (XINT1CTR) (Address 7078h) ........................................................ 164

1-94. External Interrupt 2 Counter (XINT2CTR) (Address 7079h) ........................................................ 165

1-95. External NMI Interrupt Counter (XNMICTR) (Address 707Fh) ..................................................... 165

2-1. Memory Map of On-Chip ROM ......................................................................................... 167

www.ti.com

14 SPRUI07–March 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

List of Figures

2-2. Vector Table Map ......................................................................................................... 170

2-3. Bootloader Flow Diagram ................................................................................................ 172

2-4. Boot ROM Stack .......................................................................................................... 174

2-5. Boot ROM Function Overview .......................................................................................... 176

2-6. Jump-to-Flash Flow Diagram ............................................................................................ 177

2-7. Flow Diagram of Jump to M0 SARAM ................................................................................. 177

2-8. Flow Diagram of Jump-to-OTP Memory ............................................................................... 177

2-9. Flow Diagram of Jump to XINTF x16 .................................................................................. 178

2-10. Flow Diagram of Jump to XINTF x32 .................................................................................. 178

2-11. Bootloader Basic Transfer Procedure ................................................................................. 183

2-12. Overview of InitBoot Assembly Function .............................................................................. 184

2-13. Overview of the SelectBootMode Function ........................................................................... 185