实例介绍

【实例截图】

【核心代码】

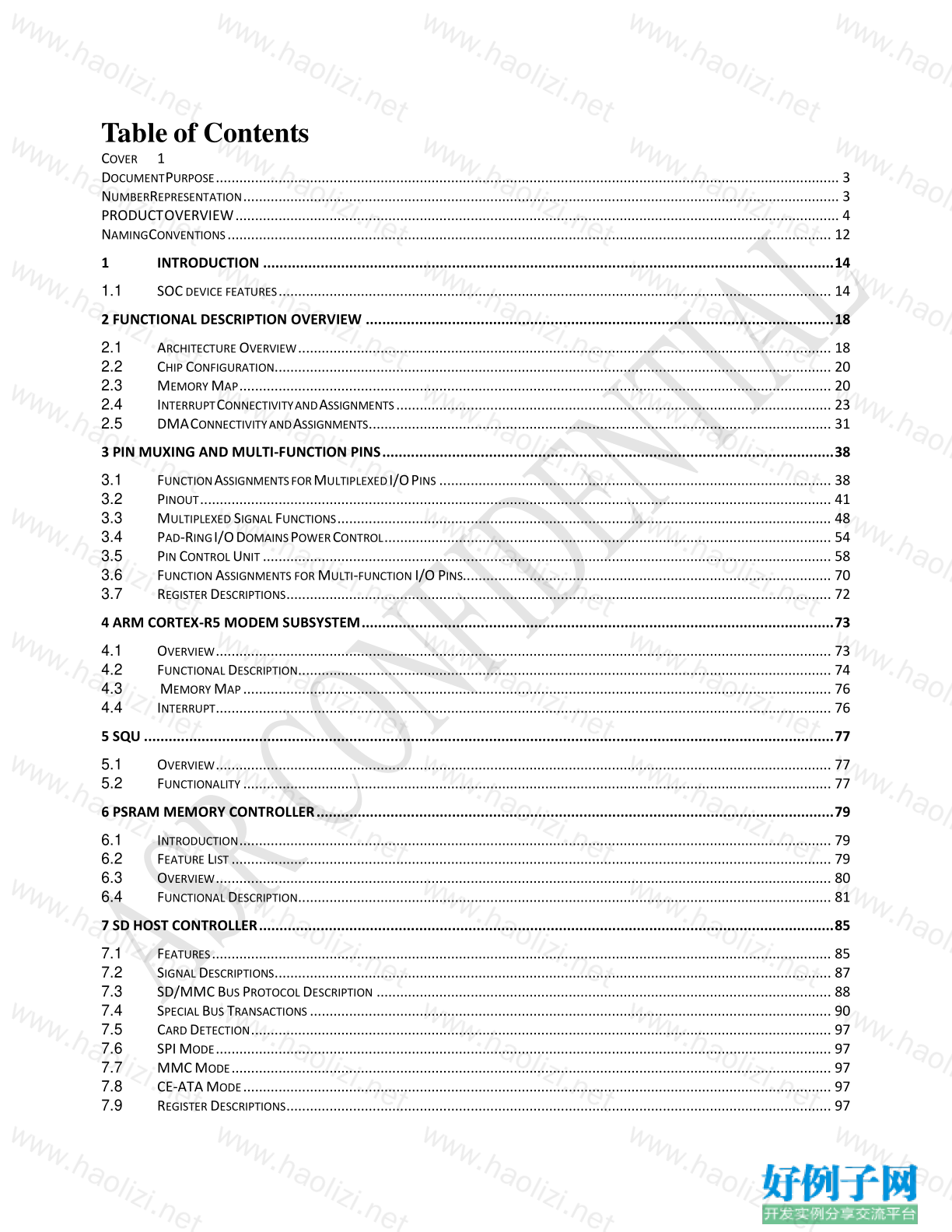

Table of Contents

C OVER 1

D OCUMENT P URPOSE ............................................................................................................................................................... 3

N UMBER R EPRESENTATION ........................................................................................................................................................ 3

PRODUCT OVERVIEW .......................................................................................................................................................... 4

N AMING C ONVENTIONS .......................................................................................................................................................... 12

1 INTRODUCTION ........................................................................................................................................... 14

1.1 SOC DEVICE FEATURES ............................................................................................................................................. 14

2 FUNCTIONAL DESCRIPTION OVERVIEW .................................................................................................................. 18

2.1 A RCHITECTURE O VERVIEW ........................................................................................................................................ 18

2.2 C HIP C ONFIGURATION .............................................................................................................................................. 20

2.3 M EMORY M AP ....................................................................................................................................................... 20

2.4 I NTERRUPT C ONNECTIVITY AND A SSIGNMENTS ............................................................................................................... 23

2.5 DMA C ONNECTIVITY AND A SSIGNMENTS ...................................................................................................................... 31

3 PIN MUXING AND MULTI-FUNCTION PINS .............................................................................................................. 38

3.1 F UNCTION A SSIGNMENTS FOR M ULTIPLEXED I/O P INS .................................................................................................... 38

3.2 P INOUT ................................................................................................................................................................. 41

3.3 M ULTIPLEXED S IGNAL F UNCTIONS .............................................................................................................................. 48

3.4 P AD -R ING I/O D OMAINS P OWER C ONTROL .................................................................................................................. 54

3.5 P IN C ONTROL U NIT ................................................................................................................................................. 58

3.6 F UNCTION A SSIGNMENTS FOR M ULTI - FUNCTION I/O P INS .............................................................................................. 70

3.7 R EGISTER D ESCRIPTIONS ........................................................................................................................................... 72

4 ARM CORTEX-R5 MODEM SUBSYSTEM ................................................................................................................... 73

4.1 O VERVIEW ............................................................................................................................................................. 73

4.2 F UNCTIONAL D ESCRIPTION ........................................................................................................................................ 74

4.3 M EMORY M AP ...................................................................................................................................................... 76

4.4 I NTERRUPT ............................................................................................................................................................. 76

5 SQU ........................................................................................................................................................................ 77

5.1 O VERVIEW ............................................................................................................................................................. 77

5.2 F UNCTIONALITY ...................................................................................................................................................... 77

6 PSRAM MEMORY CONTROLLER .............................................................................................................................. 79

6.1 I NTRODUCTION ....................................................................................................................................................... 79

6.2 F EATURE L IST ......................................................................................................................................................... 79

6.3 O VERVIEW ............................................................................................................................................................. 80

6.4 F UNCTIONAL D ESCRIPTION ........................................................................................................................................ 81

7 SD HOST CONTROLLER ............................................................................................................................................ 85

7.1 F EATURES .............................................................................................................................................................. 85

7.2 S IGNAL D ESCRIPTIONS .............................................................................................................................................. 87

7.3 SD/MMC B US P ROTOCOL D ESCRIPTION .................................................................................................................... 88

7.4 S PECIAL B US T RANSACTIONS ..................................................................................................................................... 90

7.5 C ARD D ETECTION .................................................................................................................................................... 97

7.6 SPI M ODE ............................................................................................................................................................. 97

7.7 MMC M ODE ......................................................................................................................................................... 97

7.8 CE-ATA M ODE ...................................................................................................................................................... 97

7.9 R EGISTER D ESCRIPTIONS ........................................................................................................................................... 97

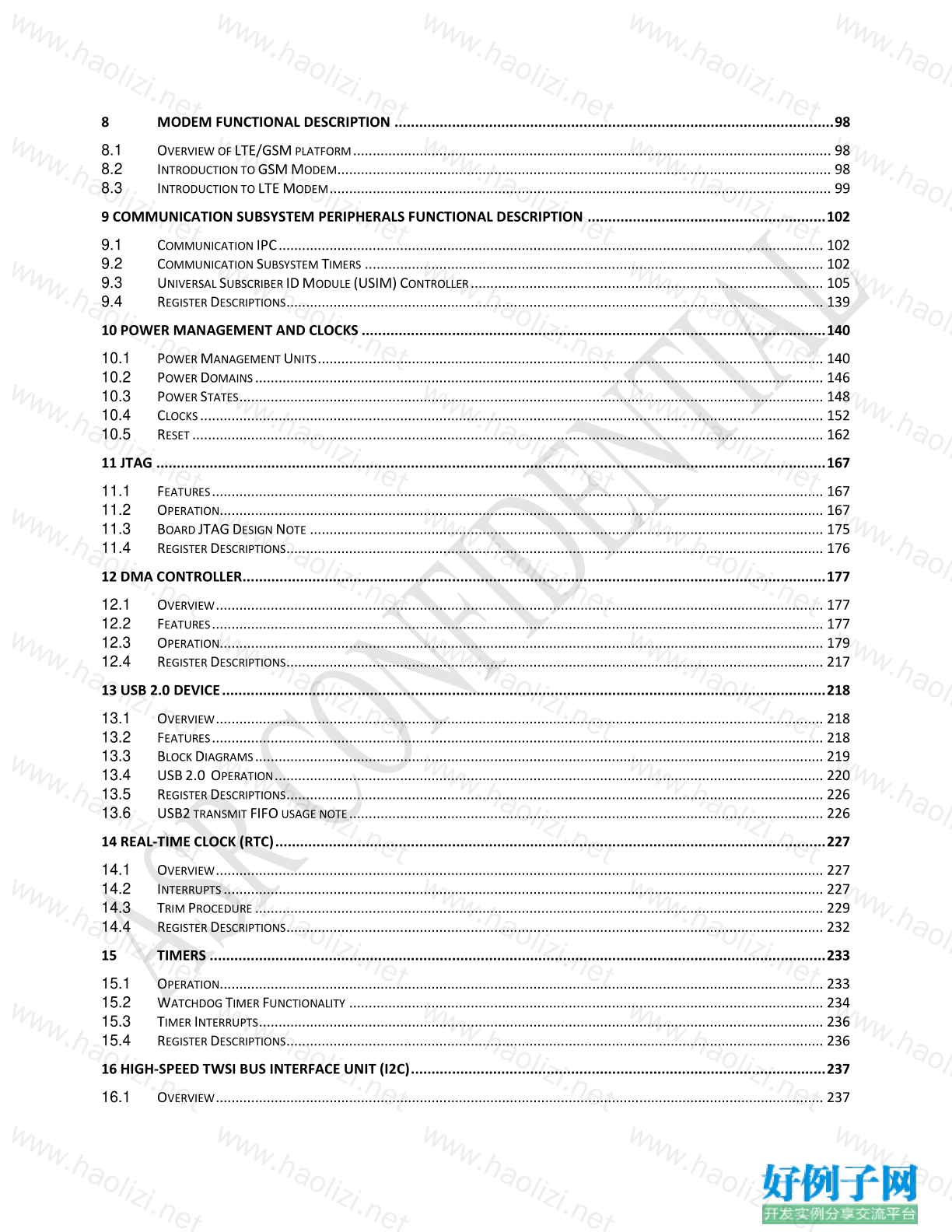

8 MODEM FUNCTIONAL DESCRIPTION ........................................................................................................... 98

8.1 O VERVIEW OF LTE/GSM PLATFORM .......................................................................................................................... 98

8.2 I NTRODUCTION TO GSM M ODEM .............................................................................................................................. 98

8.3 I NTRODUCTION TO LTE M ODEM ................................................................................................................................ 99

9 COMMUNICATION SUBSYSTEM PERIPHERALS FUNCTIONAL DESCRIPTION .......................................................... 102

9.1 C OMMUNICATION IPC ........................................................................................................................................... 102

9.2 C OMMUNICATION S UBSYSTEM T IMERS ..................................................................................................................... 102

9.3 U NIVERSAL S UBSCRIBER ID M ODULE (USIM) C ONTROLLER .......................................................................................... 105

9.4 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 139

10 POWER MANAGEMENT AND CLOCKS ................................................................................................................. 140

10.1 P OWER M ANAGEMENT U NITS ................................................................................................................................. 140

10.2 P OWER D OMAINS ................................................................................................................................................. 146

10.3 P OWER S TATES ..................................................................................................................................................... 148

10.4 C LOCKS ............................................................................................................................................................... 152

10.5 R ESET ................................................................................................................................................................. 162

11 JTAG ................................................................................................................................................................... 167

11.1 F EATURES ............................................................................................................................................................ 167

11.2 O PERATION .......................................................................................................................................................... 167

11.3 B OARD JTAG D ESIGN N OTE ................................................................................................................................... 175

11.4 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 176

12 DMA CONTROLLER.............................................................................................................................................. 177

12.1 O VERVIEW ........................................................................................................................................................... 177

12.2 F EATURES ............................................................................................................................................................ 177

12.3 O PERATION .......................................................................................................................................................... 179

12.4 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 217

13 USB 2.0 DEVICE ................................................................................................................................................... 218

13.1 O VERVIEW ........................................................................................................................................................... 218

13.2 F EATURES ............................................................................................................................................................ 218

13.3 B LOCK D IAGRAMS ................................................................................................................................................. 219

13.4 USB 2.0 O PERATION ............................................................................................................................................ 220

13.5 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 226

13.6 USB2 TRANSMIT FIFO USAGE NOTE ......................................................................................................................... 226

14 REAL-TIME CLOCK (RTC) ...................................................................................................................................... 227

14.1 O VERVIEW ........................................................................................................................................................... 227

14.2 I NTERRUPTS ......................................................................................................................................................... 227

14.3 T RIM P ROCEDURE ................................................................................................................................................. 229

14.4 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 232

15 TIMERS ...................................................................................................................................................... 233

15.1 O PERATION .......................................................................................................................................................... 233

15.2 W ATCHDOG T IMER F UNCTIONALITY ......................................................................................................................... 234

15.3 T IMER I NTERRUPTS ................................................................................................................................................ 236

15.4 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 236

16 HIGH-SPEED TWSI BUS INTERFACE UNIT (I2C) ..................................................................................................... 237

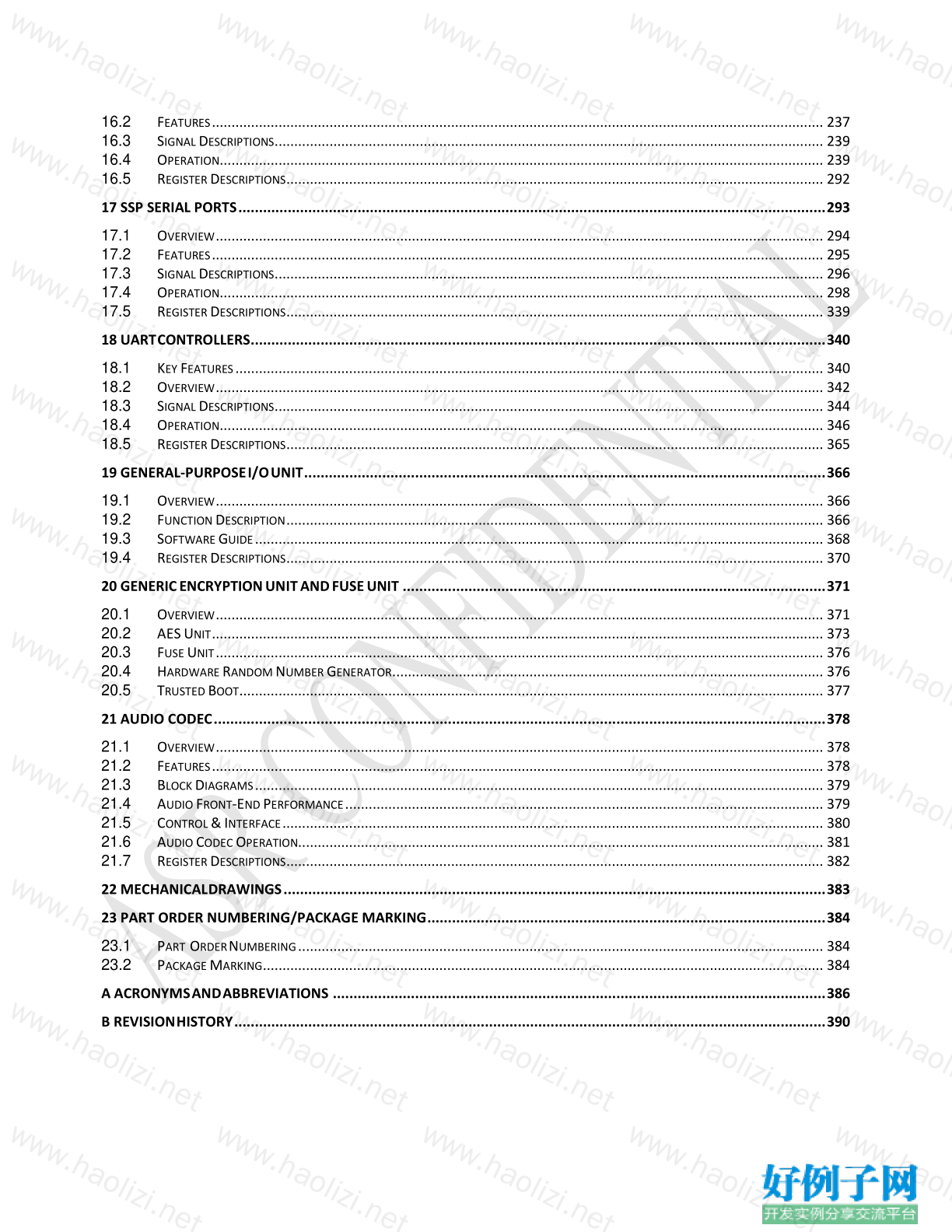

16.1 O VERVIEW ........................................................................................................................................................... 237

16.2 F EATURES ............................................................................................................................................................ 237

16.3 S IGNAL D ESCRIPTIONS ............................................................................................................................................ 239

16.4 O PERATION .......................................................................................................................................................... 239

16.5 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 292

17 SSP SERIAL PORTS ............................................................................................................................................... 293

17.1 O VERVIEW ........................................................................................................................................................... 294

17.2 F EATURES ............................................................................................................................................................ 295

17.3 S IGNAL D ESCRIPTIONS ............................................................................................................................................ 296

17.4 O PERATION .......................................................................................................................................................... 298

17.5 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 339

18 UART CONTROLLERS ............................................................................................................................................ 340

18.1 K EY F EATURES ...................................................................................................................................................... 340

18.2 O VERVIEW ........................................................................................................................................................... 342

18.3 S IGNAL D ESCRIPTIONS ............................................................................................................................................ 344

18.4 O PERATION .......................................................................................................................................................... 346

18.5 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 365

19 GENERAL-PURPOSE I/O UNIT ............................................................................................................................... 366

19.1 O VERVIEW ........................................................................................................................................................... 366

19.2 F UNCTION D ESCRIPTION ......................................................................................................................................... 366

19.3 S OFTWARE G UIDE ................................................................................................................................................. 368

19.4 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 370

20 GENERIC ENCRYPTION UNIT AND FUSE UNIT ....................................................................................................... 371

20.1 O VERVIEW ........................................................................................................................................................... 371

20.2 AES U NIT ............................................................................................................................................................ 373

20.3 F USE U NIT ........................................................................................................................................................... 376

20.4 H ARDWARE R ANDOM N UMBER G ENERATOR .............................................................................................................. 376

20.5 T RUSTED B OOT ..................................................................................................................................................... 377

21 AUDIO CODEC ..................................................................................................................................................... 378

21.1 O VERVIEW ........................................................................................................................................................... 378

21.2 F EATURES ............................................................................................................................................................ 378

21.3 B LOCK D IAGRAMS ................................................................................................................................................. 379

21.4 A UDIO F RONT -E ND P ERFORMANCE .......................................................................................................................... 379

21.5 C ONTROL & I NTERFACE .......................................................................................................................................... 380

21.6 A UDIO C ODEC O PERATION ...................................................................................................................................... 381

21.7 R EGISTER D ESCRIPTIONS ......................................................................................................................................... 382

22 MECHANICAL DRAWINGS .................................................................................................................................... 383

23 PART ORDER NUMBERING/PACKAGE MARKING ................................................................................................. 384

23.1 P ART O RDER N UMBERING ...................................................................................................................................... 384

23.2 P ACKAGE M ARKING ............................................................................................................................................... 384

A ACRONYMS AND ABBREVIATIONS ........................................................................................................................ 386

B REVISION HISTORY ................................................................................................................................................ 390

List of Tables

T ABLE 1:R ELATED D OCUMENTS ...................................................................................................................................... 13

T ABLE 2:PSRAM AXI P ORT C ONNECTIONS ..................................................................................................................... 19

T ABLE 3: ICU H ARDWARE I NTERRUPT ............................................................................................................................. 25

T ABLE 4:MIRQ INTERRUPT SOURCE ................................................................................................................................. 28

T ABLE 5:AIRQ INTERRUPT SOURCE .................................................................................................................................. 30

T ABLE 6:AP DMA PERIPHERALS ...................................................................................................................................... 33

T ABLE 7:CP DMA PERIPHERALS ...................................................................................................................................... 37

T ABLE 8:ASR3601 P IN L IST ............................................................................................................................................. 42

T ABLE 9:S IGNAL T YPES .................................................................................................................................................... 48

T ABLE 10:M ULTIPLEXED S IGNAL D ESCRIPTION ............................................................................................................... 48

T ABLE 11:P OWER S UPPLIES D ESCRIPTIONS ...................................................................................................................... 57

T ABLE 12:P IN F UNCTION E XAMPLE .................................................................................................................................. 64

T ABLE 13: <DRIVE> F IELD S ETTINGS ............................................................................................................................. 68

T ABLE 14:P REDEFINED INSTRUCTIONS .............................................................................................................................. 81

T ABLE 15:SD H OST S IGNAL D ESCRIPTIONS ...................................................................................................................... 87

T ABLE 16:LTE M ODEM M ODULES ................................................................................................................................. 100

T ABLE 17: USIM C ONTROLLER S IGNALS S UMMARY ...................................................................................................... 106

T ABLE 18:USIM S MART C ARD P INOUT ........................................................................................................................... 108

T ABLE 19:DCSR S ETUP TO I GNORE EOR ....................................................................................................................... 138

T ABLE 20:AMUCRM M ASK B ITS .................................................................................................................................. 143

T ABLE 21:ASR3601 P OWER S TATES .............................................................................................................................. 149

T ABLE 22:A PPLICATION APB P ERIPHERALS ................................................................................................................... 159

T ABLE 23:C OMMUNICATION APB P ERIPHERALS ............................................................................................................ 160

T ABLE 24:P RIMARY C LOCK D OMAINS C LOCK S HUTDOWN C ONDITIONS ........................................................................ 161

T ABLE 25:S YSTEM R ESET D OMAINS ............................................................................................................................... 164

T ABLE 26:JTAG I NSTRUCTION D ESCRIPTION ................................................................................................................. 169

T ABLE 27:DMA S UPPORT M ATRIX ................................................................................................................................. 178

T ABLE 28:C HANNEL P RIORITY ........................................................................................................................................ 180

T ABLE 29:C HANNEL S TATES B ASED ON S OFTWARE C ONFIGURATION ............................................................................ 182

T ABLE 30:C ONFIGURATION FOR P ERIPHERAL B US P ERIPHERAL R ELATED D ATA T RANSFERS ........................................ 203

T ABLE 31:C ONFIGURATION FOR M EMORY - TO -M EMORY D ATA T RANSFERS .................................................................. 203

T ABLE 32:S YSTEM B US P ERIPHERAL R ELATED D ATA T RANSFER C ONFIGURATION ....................................................... 204

T ABLE 33:C ONFIGURATION FOR C OMPANION C HIP (CC) R ELATED D ATA T RANSFERS .................................................. 204

T ABLE 34:DMA Q UICK R EFERENCE FOR O N -C HIP P ERIPHERALS ................................................................................... 206

T ABLE 35:DMA Q UICK R EFERENCE FOR O N -C HIP P ERIPHERALS ................................................................................... 239

T ABLE 36:TWSI B US D EFINITIONS ................................................................................................................................. 240

T ABLE 37:M ODES OF O PERATION ................................................................................................................................... 246

T ABLE 38:START AND STOP B IT D EFINITIONS ............................................................................................................. 249

T ABLE 39:M ASTER T RANSACTIONS ................................................................................................................................ 264

T ABLE 40:S LAVE T RANSACTIONS ................................................................................................................................... 281

T ABLE 41:G ENERAL C ALL A DDRESS S ECOND B YTE D EFINITIONS .................................................................................. 290

T ABLE 42:ASR3601 E XTERNAL S IGNAL D ESCRIPTIONS ................................................................................................. 296

T ABLE 43:P ROGRAMMABLE P ROTOCOL P ARAMETERS .................................................................................................... 322

T ABLE 44:SSP_SSCR1[TFT] AND SSP_SSCR1[RFT] V ALUES WITH DMA B URST S IZES ............................................ 334

T ABLE 45:S UPPORTED B AUD R ATES ............................................................................................................................... 343

T ABLE 46:UART S IGNAL D ESCRIPTIONS ........................................................................................................................ 344

T ABLE 47:R ECOMMENDED B AUD R ATES ........................................................................................................................ 364

T ABLE 48:GPIO I NTERRUPTS .......................................................................................................................................... 368

T ABLE 49: A NALOG M ICROPHONE INPUT TO ADC PERFORMANCE ................................................................................. 379

T ABLE 50: G ENERAL A UDIO R X P ATH F EATURE S UMMARY ........................................................................................... 380

T ABLE 51:ASR3601 P ART O RDER O PTIONS ................................................................................................................... 384

T ABLE 52:ASR3601 W ORK T EMPERATURE .................................................................................................................... 384

T ABLE 53:R EVISION H ISTORY ......................................................................................................................................... 390

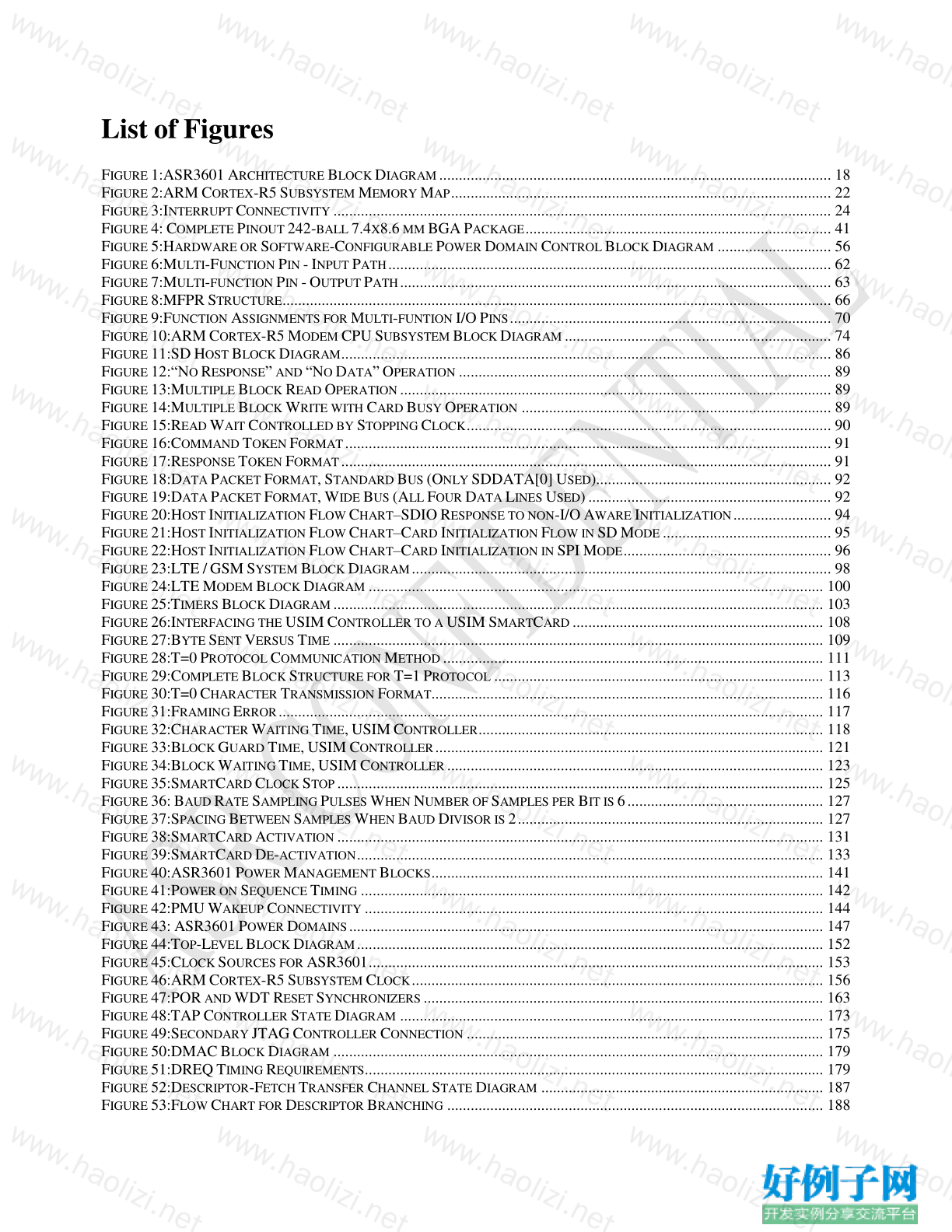

List of Figures

F IGURE 1:ASR3601 A RCHITECTURE B LOCK D IAGRAM .................................................................................................... 18

F IGURE 2:ARM C ORTEX -R5 S UBSYSTEM M EMORY M AP ................................................................................................. 22

F IGURE 3:I NTERRUPT C ONNECTIVITY ............................................................................................................................... 24

F IGURE 4: C OMPLETE P INOUT 242- BALL 7.4 X 8.6 MM BGA P ACKAGE .............................................................................. 41

F IGURE 5:H ARDWARE OR S OFTWARE -C ONFIGURABLE P OWER D OMAIN C ONTROL B LOCK D IAGRAM ............................. 56

F IGURE 6:M ULTI -F UNCTION P IN - I NPUT P ATH ................................................................................................................. 62

F IGURE 7:M ULTI - FUNCTION P IN - O UTPUT P ATH .............................................................................................................. 63

F IGURE 8:MFPR S TRUCTURE ............................................................................................................................................ 66

F IGURE 9:F UNCTION A SSIGNMENTS FOR M ULTI - FUNTION I/O P INS .................................................................................. 70

F IGURE 10:ARM C ORTEX -R5 M ODEM CPU S UBSYSTEM B LOCK D IAGRAM .................................................................... 74

F IGURE 11:SD H OST B LOCK D IAGRAM ............................................................................................................................. 86

F IGURE 12:“N O R ESPONSE ” AND “N O D ATA ” O PERATION ............................................................................................... 89

F IGURE 13:M ULTIPLE B LOCK R EAD O PERATION .............................................................................................................. 89

F IGURE 14:M ULTIPLE B LOCK W RITE WITH C ARD B USY O PERATION ............................................................................... 89

F IGURE 15:R EAD W AIT C ONTROLLED BY S TOPPING C LOCK ............................................................................................. 90

F IGURE 16:C OMMAND T OKEN F ORMAT ............................................................................................................................ 91

F IGURE 17:R ESPONSE T OKEN F ORMAT ............................................................................................................................. 91

F IGURE 18:D ATA P ACKET F ORMAT , S TANDARD B US (O NLY SDDATA[0] U SED )............................................................ 92

F IGURE 19:D ATA P ACKET F ORMAT , W IDE B US (A LL F OUR D ATA L INES U SED ) .............................................................. 92

F IGURE 20:H OST I NITIALIZATION F LOW C HART –SDIO R ESPONSE TO NON -I/O A WARE I NITIALIZATION ......................... 94

F IGURE 21:H OST I NITIALIZATION F LOW C HART –C ARD I NITIALIZATION F LOW IN SD M ODE ........................................... 95

F IGURE 22:H OST I NITIALIZATION F LOW C HART –C ARD I NITIALIZATION IN SPI M ODE ..................................................... 96

F IGURE 23:LTE / GSM S YSTEM B LOCK D IAGRAM ........................................................................................................... 98

F IGURE 24:LTE M ODEM B LOCK D IAGRAM .................................................................................................................... 100

F IGURE 25:T IMERS B LOCK D IAGRAM ............................................................................................................................. 103

F IGURE 26:I NTERFACING THE USIM C ONTROLLER TO A USIM S MART C ARD ................................................................ 108

F IGURE 27:B YTE S ENT V ERSUS T IME ............................................................................................................................. 109

F IGURE 28:T=0 P ROTOCOL C OMMUNICATION M ETHOD ................................................................................................. 111

F IGURE 29:C OMPLETE B LOCK S TRUCTURE FOR T=1 P ROTOCOL .................................................................................... 113

F IGURE 30:T=0 C HARACTER T RANSMISSION F ORMAT .................................................................................................... 116

F IGURE 31:F RAMING E RROR ........................................................................................................................................... 117

F IGURE 32:C HARACTER W AITING T IME , USIM C ONTROLLER ........................................................................................ 118

F IGURE 33:B LOCK G UARD T IME , USIM C ONTROLLER ................................................................................................... 121

F IGURE 34:B LOCK W AITING T IME , USIM C ONTROLLER ................................................................................................ 123

F IGURE 35:S MART C ARD C LOCK S TOP ............................................................................................................................ 125

F IGURE 36: B AUD R ATE S AMPLING P ULSES W HEN N UMBER OF S AMPLES PER B IT IS 6 .................................................. 127

F IGURE 37:S PACING B ETWEEN S AMPLES W HEN B AUD D IVISOR IS 2 .............................................................................. 127

F IGURE 38:S MART C ARD A CTIVATION ............................................................................................................................ 131

F IGURE 39:S MART C ARD D E - ACTIVATION ....................................................................................................................... 133

F IGURE 40:ASR3601 P OWER M ANAGEMENT B LOCKS .................................................................................................... 141

F IGURE 41:P OWER ON S EQUENCE T IMING ...................................................................................................................... 142

F IGURE 42:PMU W AKEUP C ONNECTIVITY ..................................................................................................................... 144

F IGURE 43: ASR3601 P OWER D OMAINS ......................................................................................................................... 147

F IGURE 44:T OP -L EVEL B LOCK D IAGRAM ....................................................................................................................... 152

F IGURE 45:C LOCK S OURCES FOR ASR3601 .................................................................................................................... 153

F IGURE 46:ARM C ORTEX -R5 S UBSYSTEM C LOCK ......................................................................................................... 156

F IGURE 47:POR AND WDT R ESET S YNCHRONIZERS ...................................................................................................... 163

F IGURE 48:TAP C ONTROLLER S TATE D IAGRAM ............................................................................................................ 173

F IGURE 49:S ECONDARY JTAG C ONTROLLER C ONNECTION ........................................................................................... 175

F IGURE 50:DMAC B LOCK D IAGRAM ............................................................................................................................. 179

F IGURE 51:DREQ T IMING R EQUIREMENTS ..................................................................................................................... 179

F IGURE 52:D ESCRIPTOR -F ETCH T RANSFER C HANNEL S TATE D IAGRAM ........................................................................ 187

F IGURE 53:F LOW C HART FOR D ESCRIPTOR B RANCHING ................................................................................................ 188

F IGURE 54:N O -D ESCRIPTOR -F ETCH T RANSFER C HANNEL S TATE D IAGRAM .................................................................. 191

F IGURE 55:D ESCRIPTOR C HAIN FOR S OFTWARE I MPLEMENTATION OF F ULL AND E MPTY B ITS ...................................... 217

F IGURE 56:USB 2.0 B LOCK D IAGRAM ............................................................................................................................ 219

F IGURE 57:USB 2.0 PHY B LOCK D IAGRAM ................................................................................................................... 220

F IGURE 58:T IMERS B LOCK D IAGRAM ............................................................................................................................. 234

F IGURE 59:TWSI B US C ONFIGURATION E XAMPLE ......................................................................................................... 241

F IGURE 60:TWSI B US I NTERFACE U NIT B LOCK D IAGRAM ............................................................................................. 243

F IGURE 61:T X AND R X FIFO S S HOWN IN FIFO M ODE ................................................................................................... 245

F IGURE 62:SDA AND SCL S IGNALS D URING S TART AND S TOP C ONDITIONS ................................................................. 248

F IGURE 63:S TART AND S TOP C ONDITIONS ...................................................................................................................... 251

F IGURE 64:D ATA F ORMAT OF F IRST B YTE IN M ASTER T RANSACTION ............................................................................ 254

F IGURE 65:A CKNOWLEDGE P ULSE ON THE TWSI B US ................................................................................................... 255

F IGURE 66:C LOCK S YNCHRONIZATION D URING A RBITRATION ...................................................................................... 258

F IGURE 67:A RBITRATION P ROCEDURE FOR T WO M ASTERS ............................................................................................ 259

F IGURE 68:H IGH S PEED M ODE D ATA T RANSFER ............................................................................................................ 263

F IGURE 69:M ASTER R ECEIVER R EAD FROM S LAVE T RANSMITTER ................................................................................. 266

F IGURE 70:M ASTER -R ECEIVER R EAD FROM S LAVE -T RANSMITTER / R EPEATED S TART /M ASTER -T RANSMITTER W RITE TO

S LAVE -R ECEIVER .................................................................................................................................................. 266

F IGURE 71:A C OMPLETE D ATA T RANSFER ..................................................................................................................... 266

F IGURE 72:T X FIFO E NTRY F ORMAT ............................................................................................................................. 277

F IGURE 73:R X FIFO E NTRY F ORMAT ............................................................................................................................. 277

F IGURE 74:T RANSMIT AND R ECEIVE FIFO S .................................................................................................................... 277

F IGURE 75:C ASE 1: W RITE 10 B YTES .............................................................................................................................. 279

F IGURE 76:C ASE 2: R EAD 8 B YTES F OLLOWED BY W RITE 2 B YTES ................................................................................ 279

F IGURE 77:M ASTER T RANSMITTER W RITE TO S LAVE R ECEIVER .................................................................................... 283

F IGURE 78:M ASTER R ECEIVER R EAD FROM S LAVE -T RANSMITTER ................................................................................ 283

F IGURE 79:M ASTER -R ECEIVER R EAD TO S LAVE -T RANSMITTER , R EPEATED S TART , M ASTER -T RANSMITTER W RITE TO

S LAVE R ECEIVER ................................................................................................................................................... 283

F IGURE 80:G ENERAL C ALL A DDRESS ............................................................................................................................. 289

F IGURE 81:T EXAS I NSTRUMENTS * S YNCHRONOUS S ERIAL F RAME P ROTOCOL (S INGLE T RANSFERS ) ............................ 309

F IGURE 82:T EXAS I NSTRUMENTS * S YNCHRONOUS S ERIAL F RAME P ROTOCOL (M ULTIPLE T RANSFERS ) ....................... 310

F IGURE 83:M OTOROLA * SPI F RAME P ROTOCOL (S INGLE T RANSFERS ) .......................................................................... 312

F IGURE 84:M OTOROLA * SPI F RAME P ROTOCOL (M ULTIPLE T RANSFERS ) ..................................................................... 313

F IGURE 85:M OTOROLA * SPI F RAME P ROTOCOLS FOR SPO AND SPH P ROGRAMMING (SPH S ET ) ................................. 315

F IGURE 86:M OTOROLA * SPI F RAME P ROTOCOLS FOR SPO AND SPH P ROGRAMMING ................................................... 315

F IGURE 87:N ATIONAL S EMICONDUCTOR * M ICROWIRE F RAME P ROTOCOL (S INGLE T RANSFER ) .................................... 317

F IGURE 88:N ATIONAL S EMICONDUCTOR * M ICROWIRE F RAME P ROTOCOL (M ULTIPLE T RANSFERS ) ............................. 318

F IGURE 89:P ROGRAMMABLE S ERIAL P ROTOCOL F ORMAT .............................................................................................. 321

F IGURE 90:P ROGRAMMABLE P ROTOCOL F ORMAT (C ONSECUTIVE T RANSFERS ) ............................................................. 322

F IGURE 91:TI SSP WITH SSP_SSCR1[TTE] = 1 AND SSP_SSCR1[TTELP]] = 0 .......................................................... 324

F IGURE 92:TI SSP WITH SSP_SSCR1[TTE] = 1 AND SSP_SSCR1[TTELP] = 1 ............................................................ 325

F IGURE 93:M OTOROLA * SPI WITH <TXD T HREE -S TATE E NABLE > = 1 AND <TXD T HREE - STATE E NABLE O N L AST

P HASE > = 0 ............................................................................................................................................................ 325

F IGURE 94:N ATIONAL M ICROWIRE WITH SSP_SSCR1[TTE] = 1 AND SSP_SSCR1[TTELP] = 0 .................................. 327

F IGURE 95:PSP F ORMAT WITH SSP_SSCR1[TTE] = 1, SSP_SSCR1[TTELP] = 0, AND SSP_ SSCR1[SFRMDIR] = 1 327

F IGURE 96:PSP F ORMAT WITH SSP_SSCR1[TTE] = 1, AND EITHER SSP_SSCR1[TTELP] = 1, OR SSP_

SSCR1[SFRMDIR] = 0 ......................................................................................................................................... 328

F IGURE 97:N ETWORK M ODE (E XAMPLE U SING 4 T IME S LOTS ) ...................................................................................... 331

F IGURE 98:SSP B AUD R ATE G ENERATION ...................................................................................................................... 338

F IGURE 99:E XAMPLE UART D ATA F RAME .................................................................................................................... 346

F IGURE 100:E XAMPLE NRZ B IT E NCODING — 0 B 0100_1011 ........................................................................................ 347

F IGURE 101:IR T RANSMIT AND R ECEIVE E XAMPLE ........................................................................................................ 360

F IGURE 102:XMODE E XAMPLE ..................................................................................................................................... 361

F IGURE 103:G ENERAL -P URPOSE I/O B LOCK D IAGRAM .................................................................................................. 367

F IGURE 104:GEU B LOCK D IAGRAM ............................................................................................................................... 372

F IGURE 105:ECB B LOCK D IAGRAM ................................................................................................................................ 375

F IGURE 106:CBC E NCRYPTION B LOCK D IAGRAM .......................................................................................................... 375

F IGURE 107:CBC D ECRYPTION B LOCK D IAGRAM .......................................................................................................... 376

F IGURE 108:R ANDOM N UMBER G ENERATOR B LOCK D IAGRAM ..................................................................................... 377

F IGURE 109:S ECURE B OOT S OFTWARE F LOW ................................................................................................................. 377

F IGURE 110: A UDIO C ODEC B LOCK D IAGRAM ................................................................................................................ 379

F IGURE 111: A UDIO C ODEC INTERFACE D IAGRAM ......................................................................................................... 380

F IGURE 112:242- PIN 7.4X8.6 MM BGA P ACKAGE ........................................................................................................... 383

F IGURE 113:C OMMERCIAL P ACKAGE M ARKING AND P IN 1 L OCATION ........................................................................... 384

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论