实例介绍

【实例简介】VHDL programming by example

vhdl入门

【实例截图】

【核心代码】

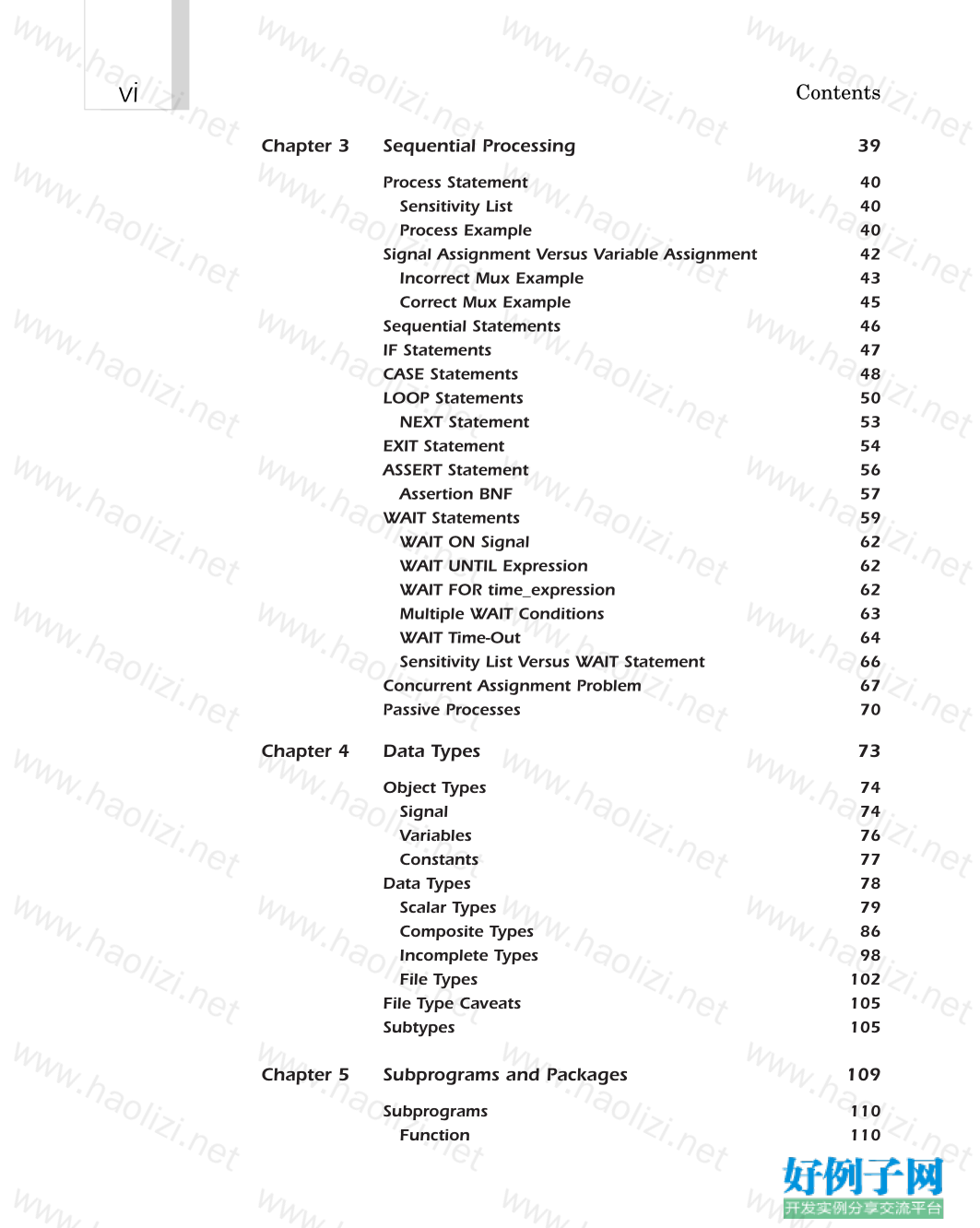

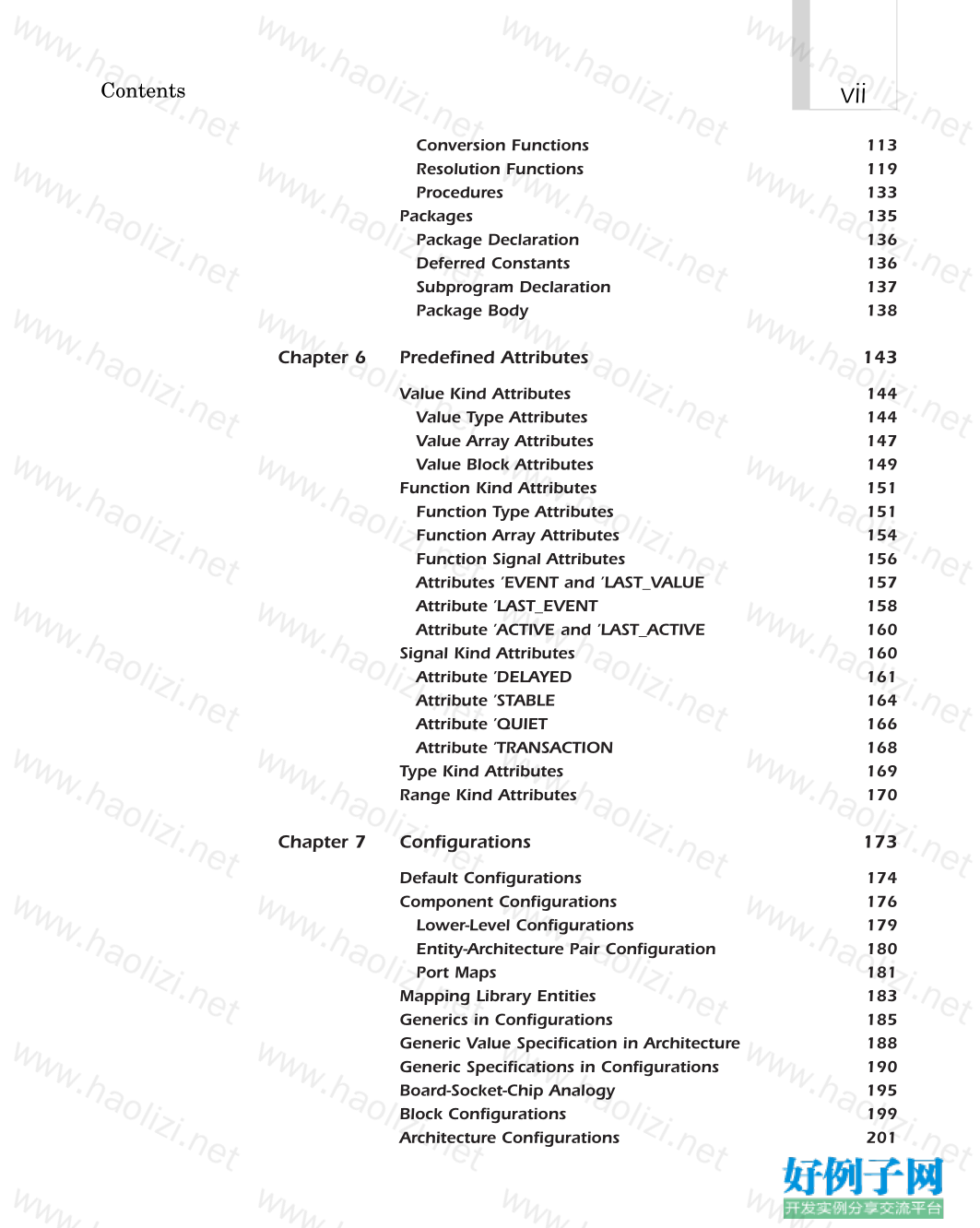

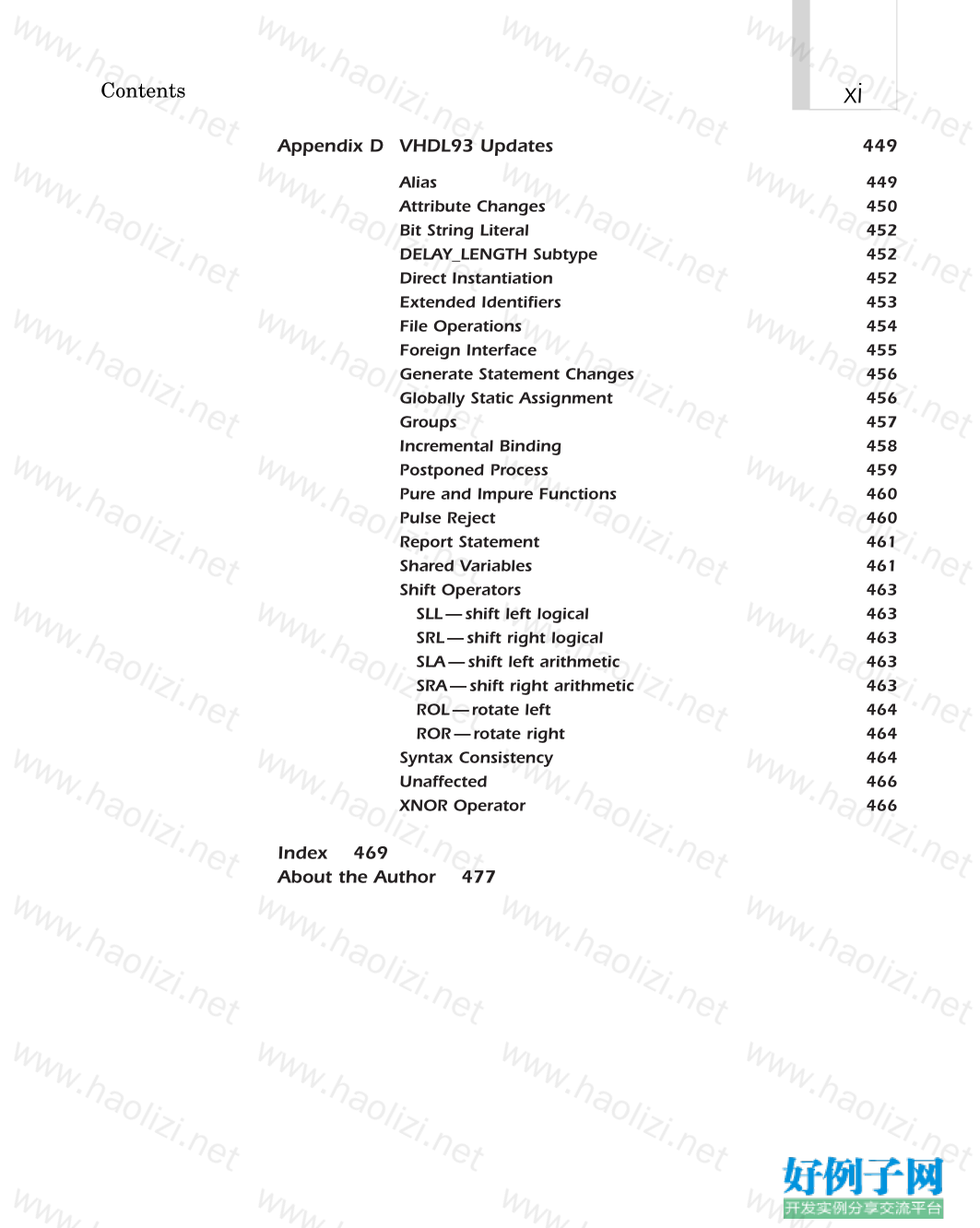

CONTENTS

Foreword xiii

Preface xv

Acknowledgments xviii

Chapter 1 Introduction to VHDL 1

VHDL Terms 2

Describing Hardware in VHDL 3

Entity 3

Architectures 4

Concurrent Signal Assignment 5

Event Scheduling 6

Statement Concurrency 6

Structural Designs 7

Sequential Behavior 8

Process Statements 9

Process Declarative Region 9

Process Statement Part 9

Process Execution 10

Sequential Statements 10

Architecture Selection 11

Configuration Statements 11

Power of Configurations 12

Chapter 2 Behavioral Modeling 15

Introduction to Behavioral Modeling 16

Transport Versus Inertial Delay 20

Inertial Delay 20

Transport Delay 21

Inertial Delay Model 22

Transport Delay Model 23

Simulation Deltas 23

Drivers 27

Driver Creation 27

Bad Multiple Driver Model 28

Generics 29

Block Statements 31

Guarded Blocks 35

Chapter 3 Sequential Processing 39

Process Statement 40

Sensitivity List 40

Process Example 40

Signal Assignment Versus Variable Assignment 42

Incorrect Mux Example 43

Correct Mux Example 45

Sequential Statements 46

IF Statements 47

CASE Statements 48

LOOP Statements 50

NEXT Statement 53

EXIT Statement 54

ASSERT Statement 56

Assertion BNF 57

WAIT Statements 59

WAIT ON Signal 62

WAIT UNTIL Expression 62

WAIT FOR time_expression 62

Multiple WAIT Conditions 63

WAIT Time-Out 64

Sensitivity List Versus WAIT Statement 66

Concurrent Assignment Problem 67

Passive Processes 70

Chapter 4 Data Types 73

Object Types 74

Signal 74

Variables 76

Constants 77

Data Types 78

Scalar Types 79

Composite Types 86

Incomplete Types 98

File Types 102

File Type Caveats 105

Subtypes 105

Chapter 5 Subprograms and Packages 109

Subprograms 110

Function 110

Contents vi

Conversion Functions 113

Resolution Functions 119

Procedures 133

Packages 135

Package Declaration 136

Deferred Constants 136

Subprogram Declaration 137

Package Body 138

Chapter 6 Predefined Attributes 143

Value Kind Attributes 144

Value Type Attributes 144

Value Array Attributes 147

Value Block Attributes 149

Function Kind Attributes 151

Function Type Attributes 151

Function Array Attributes 154

Function Signal Attributes 156

Attributes ’EVENT and ’LAST_VALUE 157

Attribute ’LAST_EVENT 158

Attribute ’ACTIVE and ’LAST_ACTIVE 160

Signal Kind Attributes 160

Attribute ’DELAYED 161

Attribute ’STABLE 164

Attribute ’QUIET 166

Attribute ’TRANSACTION 168

Type Kind Attributes 169

Range Kind Attributes 170

Chapter 7 Configurations 173

Default Configurations 174

Component Configurations 176

Lower-Level Configurations 179

Entity-Architecture Pair Configuration 180

Port Maps 181

Mapping Library Entities 183

Generics in Configurations 185

Generic Value Specification in Architecture 188

Generic Specifications in Configurations 190

Board-Socket-Chip Analogy 195

Block Configurations 199

Architecture Configurations 201

vii

Contents

Chapter 8 Advanced Topics 205

Overloading 206

Subprogram Overloading 206

Overloading Operators 210

Aliases 215

Qualified Expressions 215

User-Defined Attributes 218

Generate Statements 220

Irregular Generate Statement 222

TextIO 224

Chapter 9 Synthesis 231

Register Transfer Level Description 232

Constraints 237

Timing Constraints 238

Clock Constraints 238

Attributes 239

Load 240

Drive 240

Arrival Time 240

Technology Libraries 241

Synthesis 243

Translation 243

Boolean Optimization 244

Flattening 245

Factoring 246

Mapping to Gates 247

Chapter 10 VHDL Synthesis 251

Simple Gate—Concurrent Assignment 252

IF Control Flow Statements 253

Case Control Flow Statements 256

Simple Sequential Statements 257

Asynchronous Reset 259

Asynchronous Preset and Clear 261

More Complex Sequential Statements 262

Four-Bit Shifter 264

State Machine Example 266

Contents viii

Chapter 11 High Level Design Flow 273

RTL Simulation 275

VHDL Synthesis 277

Functional Gate-Level Verification 283

Place and Route 284

Post Layout Timing Simulation 286

Static Timing 287

Chapter 12 Top-Level System Design 289

CPU Design 290

Top-Level System Operation 290

Instructions 291

Sample Instruction Representation 292

CPU Top-Level Design 293

Block Copy Operation 299

Chapter 13 CPU: Synthesis Description 303

ALU 306

Comp 309

Control 311

Reg 321

Regarray 322

Shift 324

Trireg 326

Chapter 14 CPU: RTL Simulation 329

Testbenches 330

Kinds of Testbenches 331

Stimulus Only 333

Full Testbench 337

Simulator Specific 340

Hybrid Testbenches 342

Fast Testbench 345

CPU Simulation 349

Chapter 15 CPU Design: Synthesis Results 357

ix

Contents

Chapter 16 Place and Route 369

Place and Route Process 370

Placing and Routing the Device 373

Setting up a project 373

Chapter 17 CPU: VITAL Simulation 379

VITAL Library 381

VITAL Simulation Process Overview 382

VITAL Implementation 382

Simple VITAL Model 383

VITAL Architecture 386

Wire Delay Section 386

Flip-Flop Example 388

SDF File 392

VITAL Simulation 394

Back-Annotated Simulation 397

Chapter 18 At Speed Debugging Techniques 399

Instrumentor 401

Debugger 401

Debug CPU Design 401

Create Project 402

Specify Top-Level Parameters 403

Specify Project Parameters 403

Instrument Signals 404

Write Instrumented Design 405

Implement New Design 405

Start Debug 406

Enable Breakpoint 406

Trigger Position 408

Waveform Display 408

Set Watchpoint 409

Complex Triggers 410

Appendix A Standard Logic Package 413

Appendix B VHDL Reference Tables 435

Appendix C Reading VHDL BNF 445

Contents x

Appendix D VHDL93 Updates 449

Alias 449

Attribute Changes 450

Bit String Literal 452

DELAY_LENGTH Subtype 452

Direct Instantiation 452

Extended Identifiers 453

File Operations 454

Foreign Interface 455

Generate Statement Changes 456

Globally Static Assignment 456

Groups 457

Incremental Binding 458

Postponed Process 459

Pure and Impure Functions 460

Pulse Reject 460

Report Statement 461

Shared Variables 461

Shift Operators 463

SLL—shift left logical 463

SRL—shift right logical 463

SLA—shift left arithmetic 463

SRA—shift right arithmetic 463

ROL—rotate left 464

ROR—rotate right 464

Syntax Consistency 464

Unaffected 466

XNOR Operator 466

Index 469

About the Author 477

标签: Programming example VHDL AMPL HDL

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论