实例介绍

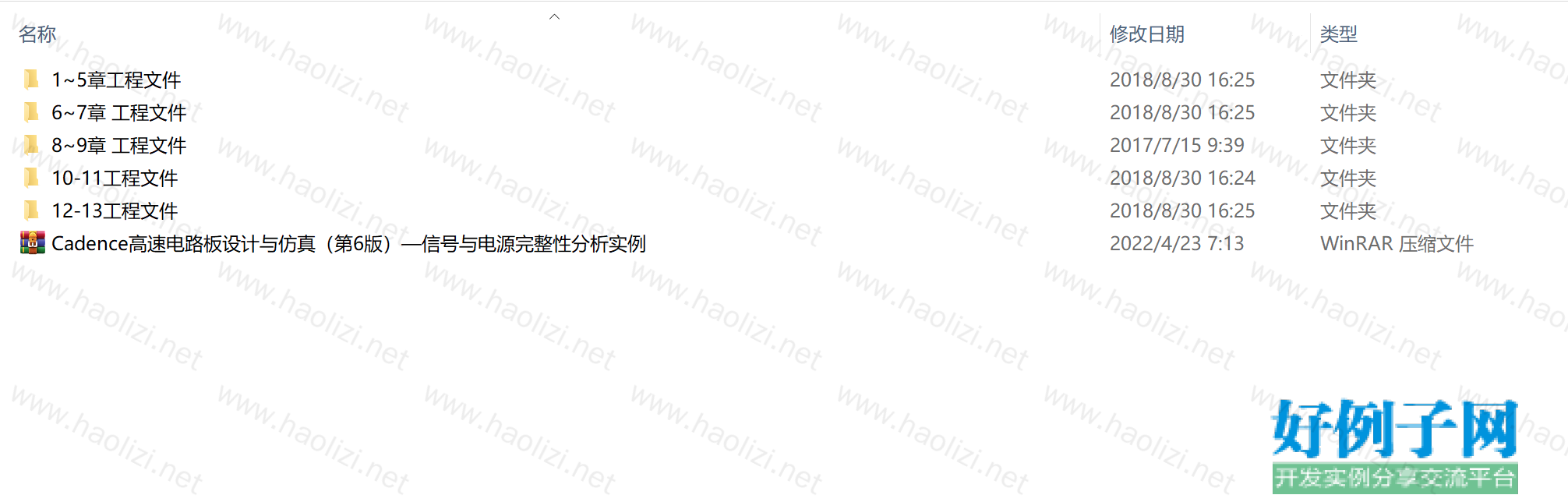

【实例简介】Cadence高速电路板设计与仿真(第6版)—信号与电源完整性分析实例

【实例截图】

【核心代码】

.

├── 10-11工程文件

│ ├── Module1

│ │ ├── Lab1

│ │ │ ├── PI_dc.brd

│ │ │ └── PI_dc_lab1.pdcx

│ │ ├── Lab2

│ │ │ └── PI_dc.brd

│ │ ├── Lab3

│ │ │ ├── PI_dc.brd

│ │ │ └── PI_dc_gnd_trace_changed.brd

│ │ └── Lab4

│ │ └── PI_dc_gnd_trace_changed.brd

│ ├── Module2

│ │ └── Lab1_2_3

│ │ ├── 0603rf_wv_12d.dra

│ │ ├── 0603rf_wv_12d.psm

│ │ ├── 0805rf_wv_12d.dra

│ │ ├── 0805rf_wv_12d.psm

│ │ ├── 40x30.pad

│ │ ├── 60x50.pad

│ │ ├── PI_ac_lab1_0.brd

│ │ ├── PI_ac_lab1_1.brd

│ │ ├── adw

│ │ │ └── shoppingCart.xml

│ │ ├── cap300.psm

│ │ ├── cap400.psm

│ │ ├── cds.lib

│ │ ├── conn50.dra

│ │ ├── conn50.psm

│ │ ├── conn50.txt

│ │ ├── cycle.msm

│ │ ├── demo.cpm

│ │ ├── flatlib

│ │ │ └── model_body

│ │ ├── master.tag

│ │ ├── obl30x30_r4sz.pad

│ │ ├── obl51x61_r5sz.pad

│ │ ├── obl51x61_r5z.pad

│ │ ├── obl71x91_r10_sz.pad

│ │ ├── obl71x91_r10z.pad

│ │ ├── pad60cir36d.pad

│ │ ├── pad60cir42d.pad

│ │ ├── pdns_segsymbol.dra

│ │ ├── pdns_segsymbol.ssm

│ │ ├── pdns_shapesymbol.dra

│ │ ├── pdns_shapesymbol.ssm

│ │ ├── pfe.run

│ │ │ └── PI_ac_lab1_1

│ │ ├── recchipn_0201c_smr.psm

│ │ ├── recchipn_0402_smr.psm

│ │ ├── sh108x71h.dra

│ │ ├── sh108x71h.ssm

│ │ ├── sh237x215fx.dra

│ │ ├── sh237x215fx.ssm

│ │ ├── sh30x30h.dra

│ │ ├── sh30x30h.ssm

│ │ ├── sh45x30h.dra

│ │ ├── sh45x30h.ssm

│ │ ├── sh51x61h.dra

│ │ ├── sh51x61h.ssm

│ │ ├── sh76x61h.dra

│ │ ├── sh76x61h.ssm

│ │ ├── sh91x71h.dra

│ │ ├── sh91x71h.ssm

│ │ ├── signoise.run

│ │ │ ├── case1

│ │ │ ├── cases.cfg

│ │ │ └── cases.cfg,1

│ │ ├── smd50_25.pad

│ │ ├── smd_1005.psm

│ │ ├── soic14.dra

│ │ ├── soic14.psm

│ │ ├── sqr24.pad

│ │ ├── testcds_ptf

│ │ │ ├── part_table.ptf

│ │ │ └── selecta.ptf

│ │ └── via1.pad

│ ├── Module3

│ │ └── Lab1_2

│ │ ├── S-Parameter File

│ │ │ ├── CL21B223KBANNN.s2p

│ │ │ ├── CL31B103KDCNNN.s2p

│ │ │ └── CL31F105ZACNNN.s2p

│ │ ├── opi_back_annotation.brd

│ │ ├── opi_back_annotation_EMI.amm

│ │ ├── opi_back_annotation_EMI.opix

│ │ ├── opi_back_annotation_EMI.spd

│ │ ├── opi_back_annotation_EMI_EMI.bnp

│ │ ├── opi_back_annotation_EMI_EMI_Optimization.restart

│ │ ├── opi_back_annotation_EMI_OPI.err

│ │ ├── opi_back_annotation_EMI_OPI.log

│ │ └── opi_back_annotation_EMI_OptimizationResult.dat

│ ├── Module4

│ │ └── Lab1

│ │ ├── amm_demo.brd

│ │ └── pinbasedamm.amm

│ └── Module5

│ └── Lab1

│ └── PI_dc.brd

├── 12-13工程文件

│ ├── Module1

│ │ └── Lab1

│ │ ├── amm_demo.spd

│ │ └── pinbasedamm.amm

│ ├── Module2

│ │ ├── Lab1

│ │ │ ├── Powermap.txt

│ │ │ ├── demo_co_extract.pdcx

│ │ │ ├── demo_co_extract_PackageElectricalThemalModel.petm

│ │ │ ├── pkg_brd_connector.spd

│ │ │ └── socket.def

│ │ └── Lab2

│ │ ├── board.spd

│ │ ├── demo_co_extract_PackageElectricalThemalModel.petm

│ │ └── test_co_sim.pdcx

│ ├── Module3

│ │ ├── Lab1

│ │ │ ├── ddr3_thermal1.map

│ │ │ ├── ddr3_thermal2.map

│ │ │ ├── demo_test.pdcx

│ │ │ ├── demo_test.spd

│ │ │ ├── inter_thermal.map

│ │ │ ├── stackedDie.xml

│ │ │ └── tc2_thermal.map

│ │ └── Lab2

│ │ ├── demo_test.spd

│ │ ├── inter_thermal.map

│ │ └── test_manual.pdcx

│ └── Module4

│ └── Lab1

│ ├── demo41.spd

│ └── demo_4_1.pdcx

├── 1~5章工程文件

│ ├── AllegroPI

│ │ ├── 11.brd

│ │ ├── 11.log

│ │ ├── allegro.jrl

│ │ ├── lab1

│ │ │ ├── 7-12-63.sim

│ │ │ ├── 8-4-3.sim

│ │ │ ├── 8-4-3.sim.sim

│ │ │ ├── 8-8-52.sim

│ │ │ ├── 8-8-69.sim

│ │ │ ├── 8-8-77.sim

│ │ │ ├── Run.Log

│ │ │ ├── Untitled.sim

│ │ │ ├── allegro.jrl

│ │ │ ├── allegro.jrl,1

│ │ │ ├── cycle.msm

│ │ │ ├── cycle.msm,1

│ │ │ ├── devices.dml

│ │ │ ├── empty.txt

│ │ │ ├── master.tag

│ │ │ ├── net.dl

│ │ │ ├── net.dl,1

│ │ │ ├── net.dst

│ │ │ ├── net.dst,1

│ │ │ ├── pfe.run

│ │ │ │ └── pwr_integrity

│ │ │ ├── powerAnalysis.run

│ │ │ │ ├── Z0vsF.tlsim

│ │ │ │ └── ZvsF.tlsim

│ │ │ ├── pwr_integrity.brd

│ │ │ ├── pwr_integrity.log

│ │ │ ├── signoise.log

│ │ │ ├── signoise.log,1

│ │ │ ├── signoise.log,2

│ │ │ ├── signoise.log,3

│ │ │ ├── signoise.run

│ │ │ │ ├── case1

│ │ │ │ ├── cases.cfg

│ │ │ │ ├── cases.cfg,1

│ │ │ │ ├── signoise.cfg

│ │ │ │ └── signoise.cfg,1

│ │ │ ├── sigwave.jrl

│ │ │ ├── sigwave.jrl,1

│ │ │ ├── tlsim.log

│ │ │ └── tlsim.log,1

│ │ ├── lab2

│ │ │ ├── allegro.jrl

│ │ │ ├── allegro.jrl,1

│ │ │ ├── cycle.msm

│ │ │ ├── cycle.msm,1

│ │ │ ├── devices.dml

│ │ │ ├── devices.dml,1

│ │ │ ├── import.brd

│ │ │ ├── interconn.iml

│ │ │ ├── interconn.iml,1

│ │ │ ├── lab2.brd

│ │ │ ├── master.tag

│ │ │ ├── modeleditor.log

│ │ │ ├── net.dl

│ │ │ ├── net.dl,1

│ │ │ ├── net.dst

│ │ │ ├── net.dst,1

│ │ │ ├── powerAnalysis.run

│ │ │ │ ├── Z0vsF.tlsim

│ │ │ │ └── ZvsF.tlsim

│ │ │ ├── pwr_integrity.brd

│ │ │ ├── pwr_integrity.log

│ │ │ ├── signoise.log

│ │ │ ├── signoise.log,1

│ │ │ ├── signoise.log,2

│ │ │ ├── signoise.log,3

│ │ │ ├── signoise.run

│ │ │ │ ├── case1

│ │ │ │ ├── cases.cfg

│ │ │ │ ├── cases.cfg,1

│ │ │ │ ├── signoise.cfg

│ │ │ │ └── signoise.cfg,1

│ │ │ ├── sigwave.jrl

│ │ │ ├── sigwave.jrl,1

│ │ │ ├── tlsim.log

│ │ │ ├── tlsim.log,1

│ │ │ ├── tlsim.log,2

│ │ │ └── tlsim.log,3

│ │ ├── lab3

│ │ │ ├── Run.Log

│ │ │ ├── allegro.jrl

│ │ │ ├── allegro.jrl,1

│ │ │ ├── devices.dml

│ │ │ ├── devices.dml,1

│ │ │ ├── lab3.brd

│ │ │ ├── lab3.log

│ │ │ ├── lab3Placed.brd

│ │ │ ├── lab3PlacedBottom.brd

│ │ │ ├── pfe.run

│ │ │ │ └── lab3

│ │ │ ├── powerAnalysis.run

│ │ │ │ ├── S1_S2_10x10L1.sim

│ │ │ │ ├── S1_S2_10x10L1.sim,1

│ │ │ │ ├── S1_S2_10x10L1.sim,2

│ │ │ │ ├── S1_S2_10x10L1.sim,3

│ │ │ │ ├── S1_S2_10x10L1.sim,4

│ │ │ │ ├── S1_S2_10x10L1.sim,5

│ │ │ │ ├── S1_S2_10x10L1.sim,6

│ │ │ │ ├── S1_S2_10x10L1.sim,7

│ │ │ │ ├── S1_S2_10x10L1.tlsim

│ │ │ │ ├── S1_S2_10x10L1.tlsim,1

│ │ │ │ ├── S1_S2_10x10L1.tlsim,2

│ │ │ │ ├── S1_S2_10x10L1.tlsim,3

│ │ │ │ ├── S1_S2_10x10L1.tlsim,4

│ │ │ │ ├── S1_S2_10x10L1.tlsim,5

│ │ │ │ ├── S1_S2_10x10L1.tlsim,6

│ │ │ │ ├── S1_S2_10x10L1.tlsim,7

│ │ │ │ ├── S1_S2_10x10L1Im.sim

│ │ │ │ ├── S1_S2_10x10L1Ma.sim

│ │ │ │ ├── S1_S2_10x10L1Ph.sim

│ │ │ │ ├── S1_S2_10x10L1Re.sim

│ │ │ │ ├── Zc.mat

│ │ │ │ ├── cycle.msm

│ │ │ │ ├── cycle.msm,1

│ │ │ │ ├── fastHenry.in

│ │ │ │ ├── fasthenry.report

│ │ │ │ ├── net.dl

│ │ │ │ ├── net.dl,1

│ │ │ │ ├── net.dst

│ │ │ │ ├── net.dst,1

│ │ │ │ ├── tlsim.log

│ │ │ │ ├── tlsim.log,1

│ │ │ │ ├── tlsim.log,2

│ │ │ │ └── tlsim.log,3

│ │ │ ├── signoise.log

│ │ │ ├── signoise.log,1

│ │ │ ├── signoise.log,2

│ │ │ ├── signoise.log,3

│ │ │ ├── signoise.run

│ │ │ │ ├── case1

│ │ │ │ ├── cases.cfg

│ │ │ │ ├── cases.cfg,1

│ │ │ │ ├── signoise.cfg

│ │ │ │ └── signoise.cfg,1

│ │ │ ├── sigwave.jrl

│ │ │ ├── sigwave.jrl,1

│ │ │ ├── sigxp.jrl

│ │ │ ├── sigxp.run

│ │ │ │ ├── case0

│ │ │ │ ├── cases.cfg

│ │ │ │ ├── cases.cfg,1

│ │ │ │ └── signoise.cfg

│ │ │ └── unnamed.log

│ │ ├── lab4

│ │ │ ├── 1

│ │ │ ├── 10-7-99.sim

│ │ │ ├── VendorCaps

│ │ │ │ ├── Cmfcs

│ │ │ │ └── muratacap

│ │ │ ├── _pqmll_devicetype_z.txt

│ │ │ ├── allegro.jrl

│ │ │ ├── allegro.jrl,1

│ │ │ ├── allegro_P00416.6_AllegroMiniDump.dmp

│ │ │ ├── devices.dml

│ │ │ ├── devices.dml,1

│ │ │ ├── devices.map

│ │ │ ├── devices.map,1

│ │ │ ├── env

│ │ │ ├── interconn.iml

│ │ │ ├── lab4.brd

│ │ │ ├── lab4.dml

│ │ │ ├── lab4.dml,1

│ │ │ ├── lab4_5.brd

│ │ │ ├── lab4_npo_0603_100uf.txt

│ │ │ ├── lab4_npo_0603_100uf.txt,1

│ │ │ ├── lab4_npo_0603_caps.dcl

│ │ │ ├── lab4_smd_tmppkg.dra

│ │ │ ├── lab4_smd_tmppkg.psm

│ │ │ ├── lab4_smd_tmppkg_smd.pad

│ │ │ ├── lab4_smd_tmppkg_via.pad

│ │ │ ├── master.tag

│ │ │ ├── mergedml.log

│ │ │ ├── murata.dml

│ │ │ ├── murata.dml,1

│ │ │ ├── perf_advisor.log

│ │ │ ├── powerAnalysis.run

│ │ │ │ ├── S1_S2_8x8L1.sim

│ │ │ │ ├── S1_S2_8x8L1.tlsim

│ │ │ │ ├── S1_S2_8x8L1Im.sim

│ │ │ │ ├── S1_S2_8x8L1Ma.sim

│ │ │ │ ├── S1_S2_8x8L1Ph.sim

│ │ │ │ ├── S1_S2_8x8L1Re.sim

│ │ │ │ ├── S5_S3_8x8L1.sim

│ │ │ │ ├── S5_S3_8x8L1.tlsim

│ │ │ │ ├── S5_S3_8x8L1Im.sim

│ │ │ │ ├── S5_S3_8x8L1Ma.sim

│ │ │ │ ├── S5_S3_8x8L1Ph.sim

│ │ │ │ ├── S5_S3_8x8L1Re.sim

│ │ │ │ ├── Zc.mat

│ │ │ │ ├── cycle.msm

│ │ │ │ ├── cycle.msm,1

│ │ │ │ ├── fastHenry.in

│ │ │ │ ├── fasthenry.report

│ │ │ │ ├── net.dl

│ │ │ │ ├── net.dl,1

│ │ │ │ ├── net.dst

│ │ │ │ ├── net.dst,1

│ │ │ │ ├── tlsim.log

│ │ │ │ └── tlsim.log,1

│ │ │ ├── quickplace.log

│ │ │ ├── quickplace.log,1

│ │ │ ├── quickplace.log,2

│ │ │ ├── quickplace.log,3

│ │ │ ├── signal_analyze.sim

│ │ │ ├── signoise.log

│ │ │ ├── signoise.log,1

│ │ │ ├── signoise.log,2

│ │ │ ├── signoise.log,3

│ │ │ ├── signoise.run

│ │ │ │ ├── case1

│ │ │ │ ├── cases.cfg

│ │ │ │ ├── cases.cfg,1

│ │ │ │ ├── signoise.cfg

│ │ │ │ └── signoise.cfg,1

│ │ │ ├── sigwave.jrl

│ │ │ ├── sigxp.run

│ │ │ │ ├── case0

│ │ │ │ └── signoise.cfg

│ │ │ ├── tdk.dml

│ │ │ ├── tdk.dml,1

│ │ │ ├── tdk1.dml

│ │ │ ├── write_device.log

│ │ │ ├── write_device.log,1

│ │ │ ├── write_device.log,2

│ │ │ └── write_device.log,3

│ │ └── signoise.run

│ │ ├── case1

│ │ ├── cases.cfg

│ │ ├── cases.cfg,1

│ │ └── signoise.cfg

│ ├── AllegroSI

│ │ └── physical

│ │ ├── 83026i_3v3.dml

│ │ ├── 8304_3v.dml

│ │ ├── 8545.dml

│ │ ├── 87946I.dml

│ │ ├── GoodModelFiles

│ │ │ ├── 83026i_3v3

│ │ │ ├── 8304_3

│ │ │ ├── 8545

│ │ │ ├── 87946I

│ │ │ ├── AMP_Model.pdf

│ │ │ ├── DDR_SDRAM_PDFs

│ │ │ ├── EP1S40F1020.pin

│ │ │ ├── EP1SGX25F.pin

│ │ │ ├── TN0020.pdf

│ │ │ ├── TN4607.pdf

│ │ │ ├── TN4611.pdf

│ │ │ ├── alvch16244

│ │ │ ├── ds_sgx.pdf

│ │ │ ├── ep1s40f1020_5

│ │ │ ├── ep1sgx25f_11

│ │ │ ├── mc100ep139dt_33

│ │ │ ├── mc100ep33d_33

│ │ │ ├── mc100ept26d_33

│ │ │ ├── s29jl064h_tsop

│ │ │ ├── stratix

│ │ │ └── stratixgx

│ │ ├── PCB_ver1

│ │ │ ├── AUTOSAVE.brd

│ │ │ ├── BYTE_LANE0.lst

│ │ │ ├── BYTE_LANE0.lst,1

│ │ │ ├── DDR_D.lst

│ │ │ ├── DDR_D.lst,1

│ │ │ ├── DDR_DS0.lst

│ │ │ ├── DDR_DS0.lst,1

│ │ │ ├── DDR_DS0.top

│ │ │ ├── DDR_DS0.txt

│ │ │ ├── DDR_DS0why.top

│ │ │ ├── DDR_Data.top

│ │ │ ├── DDR_MS.top

│ │ │ ├── DDR_MS_3_9.top

│ │ │ ├── DDR_MS_swp_rpt.txt

│ │ │ ├── DDR_TL.top

│ │ │ ├── DDR_Template.top

│ │ │ ├── HtoDDR.scf

│ │ │ ├── VER0.brd

│ │ │ ├── VER1.brd

│ │ │ ├── VER12.brd

│ │ │ ├── allegro.jrl

│ │ │ ├── allegro.jrl,1

│ │ │ ├── basics_rpt.txt

│ │ │ ├── bestsave.w

│ │ │ ├── cmpshape.log

│ │ │ ├── complete.brd

│ │ │ ├── connector.dml

│ │ │ ├── connector.dml,1

│ │ │ ├── connectorwhy.dml

│ │ │ ├── ddr_module.brd

│ │ │ ├── devices.dml

│ │ │ ├── devices.dml,1

│ │ │ ├── dimm_discretes.dml

│ │ │ ├── dimm_discretes.dml,1

│ │ │ ├── dimm_discretesnew.dml

│ │ │ ├── dimm_discretesnew.dml,1

│ │ │ ├── discretes.dml

│ │ │ ├── hidesign.brd

│ │ │ ├── hidesign2.brd

│ │ │ ├── hidesign2.dsn

│ │ │ ├── hidesign3.brd

│ │ │ ├── hidesign3.dsn

│ │ │ ├── hidesign4.brd

│ │ │ ├── hidesign5.brd

│ │ │ ├── hidesign5.log

│ │ │ ├── hidesign_autoroute.brd

│ │ │ ├── hidesign_autorouter.brd

│ │ │ ├── hidesign_manroute.brd

│ │ │ ├── ibis_models.inc,1

│ │ │ ├── interconn.iml

│ │ │ ├── interconn.iml,1

│ │ │ ├── master.tag

│ │ │ ├── modeleditor.log

│ │ │ ├── monitor.sts

│ │ │ ├── netrev.lst

│ │ │ ├── nets1.lst

│ │ │ ├── nets1.lst,1

│ │ │ ├── pdns.run

│ │ │ ├── preplace.brd

│ │ │ ├── quickplace.log

│ │ │ ├── quickplace.log,1

│ │ │ ├── quickplace.log,2

│ │ │ ├── quickplace.log,3

│ │ │ ├── reflecsummary.txt

│ │ │ ├── signoise.log

│ │ │ ├── signoise.log,1

│ │ │ ├── signoise.log,2

│ │ │ ├── signoise.log,3

│ │ │ ├── signoise.run

│ │ │ ├── sigwave.jrl

│ │ │ ├── sigwave.jrl,1

│ │ │ ├── sigxp.dml

│ │ │ ├── sigxp.dml,1

│ │ │ ├── sigxp.jrl

│ │ │ ├── sigxp.jrl,1

│ │ │ ├── sigxp.run

│ │ │ ├── specctra.did

│ │ │ ├── specctra.did,1

│ │ │ ├── specctra.log

│ │ │ ├── specctra.log,1

│ │ │ ├── specctra.log,2

│ │ │ ├── specctra.log,3

│ │ │ ├── sweep_rpt_tab.txt

│ │ │ ├── sync.dat

│ │ │ ├── ttt.txt

│ │ │ ├── unnamed.SAV

│ │ │ ├── why3_10_56.sim

│ │ │ ├── why3_8_53.sim

│ │ │ ├── why3_8_68.sim

│ │ │ ├── why3_9_18.sim

│ │ │ ├── xtalkwork.top

│ │ │ └── xtalkwork1.top

│ │ ├── RES_PACK.dml

│ │ ├── allegro.jrl

│ │ ├── allegro.jrl,1

│ │ ├── alvch16244.dml

│ │ ├── appxA

│ │ │ ├── EP1SGX25F.pin

│ │ │ └── stratixgx.ibs

│ │ ├── appxB

│ │ │ ├── BTE_BSE.dml

│ │ │ ├── HSPICE_BTE_BSE.zip

│ │ │ ├── appxB.top

│ │ │ └── bte01_bse01.sp

│ │ ├── cycle.msm

│ │ ├── cycle.msm,1

│ │ ├── ddrsdram.dml

│ │ ├── ddrsdram.ibs

│ │ ├── diffPair

│ │ │ ├── CMCHOKE.dml

│ │ │ ├── CMCHOKE.ibs

│ │ │ ├── DIFFLOOPIN.top

│ │ │ ├── DIFFLOOPIN_trace.top

│ │ │ ├── DP_LOOPIN.top

│ │ │ ├── PCI1.brd

│ │ │ ├── PCI2.brd

│ │ │ ├── PCI3.brd

│ │ │ ├── PCI4.brd

│ │ │ ├── PCI5.brd

│ │ │ ├── SISWriteComps_buff

│ │ │ ├── allegro.jrl

│ │ │ ├── allegro.jrl,1

│ │ │ ├── atomic.dml

│ │ │ ├── atomic.ibs

│ │ │ ├── atomic_plcc44.dml

│ │ │ ├── atomic_plcc44.ibs

│ │ │ ├── atomic_trac1-1.txt

│ │ │ ├── batch_drc.log

│ │ │ ├── batch_drc.log,1

│ │ │ ├── batch_drc.log,2

│ │ │ ├── batch_drc.log,3

│ │ │ ├── cmpshape.log

│ │ │ ├── comp_rlgc.inc,1

│ │ │ ├── comps.spc,1

│ │ │ ├── create_devices.log

│ │ │ ├── cycle.msm,1

│ │ │ ├── delay.dl,1

│ │ │ ├── delete_layer_objects.rpt

│ │ │ ├── devices.dml

│ │ │ ├── devices.map

│ │ │ ├── diff_sim.top

│ │ │ ├── diffpair_auto.log

│ │ │ ├── diffpair_auto.log,1

│ │ │ ├── diffpair_auto.log,2

│ │ │ ├── diffpair_auto.log,3

│ │ │ ├── dimm_discretes.dml

│ │ │ ├── dimm_discretesnew.dml

│ │ │ ├── distortion.dst,1

│ │ │ ├── dump_libraries.log

│ │ │ ├── dv_autovoid.log

│ │ │ ├── emc.run

│ │ │ ├── genfeed.log

│ │ │ ├── hermon-6.txt

│ │ │ ├── ibis_models.inc,1

│ │ │ ├── inductor-52.txt

│ │ │ ├── interconn.iml

│ │ │ ├── interconn.iml,1

│ │ │ ├── led2x1-1.txt

│ │ │ ├── lib.dml

│ │ │ ├── lt1129-1.txt

│ │ │ ├── master.tag

│ │ │ ├── mergedml.log

│ │ │ ├── mi.run

│ │ │ ├── monitor.sts

│ │ │ ├── pci-1.txt

│ │ │ ├── pcipinbot.pad

│ │ │ ├── pcipintop.pad

│ │ │ ├── pinView.dat

│ │ │ ├── place_txt.txt

│ │ │ ├── plctxt.log

│ │ │ ├── shape_islands.rpt

│ │ │ ├── signoise.log

│ │ │ ├── signoise.log,1

│ │ │ ├── signoise.log,2

│ │ │ ├── signoise.log,3

│ │ │ ├── signoise.run

│ │ │ ├── sigwave.jrl

│ │ │ ├── sigwave.jrl,1

│ │ │ ├── sigxp.dml

│ │ │ ├── sigxp.dml,1

│ │ │ ├── sigxp.jrl

│ │ │ ├── sigxp.jrl,1

│ │ │ ├── sigxp.run

│ │ │ ├── specctra.did

│ │ │ ├── specctra.log

│ │ │ ├── stimulus.spc,1

│ │ │ ├── sunspot-1.txt

│ │ │ ├── sunspot.dml

│ │ │ ├── sunspot.dml,1

│ │ │ ├── sunspot.dml.txt

│ │ │ ├── sunspot.ibs

│ │ │ ├── sweep_rpt_tab.txt

│ │ │ ├── symbols

│ │ │ ├── tc5589j25-1.txt

│ │ │ ├── tech.tech

│ │ │ ├── techfile.log

│ │ │ ├── tlsim.log,1

│ │ │ ├── tlsim.log,2

│ │ │ ├── tlsim.log,3

│ │ │ ├── translate.log

│ │ │ ├── waveforms.sim,1

│ │ │ ├── zener2-6.txt

│ │ │ └── zener2-7.txt

│ │ ├── ep1s40f1020_5.dml

│ │ ├── ep1sgx25f_1.dml

│ │ ├── ep1sgx25f_1.ibs

│ │ ├── ep1sgx25f_11.dml

│ │ ├── ep1sgx25f_11.dml,1

│ │ ├── ep1sgx25f_11.ibs

│ │ ├── epc16q100.dml

│ │ ├── epc16q100.dml,1

│ │ ├── epc16q100.ibs

│ │ ├── ibis

│ │ │ ├── ep1sgx25f_11.dml

│ │ │ ├── epc16q100.dml

│ │ │ └── s29jl064h_tsop.dml

│ │ ├── ibis_models.inc

│ │ ├── mainOutput.spc

│ │ ├── mc100ep139dt_33.dml

│ │ ├── mc100ep33d_33.dml

│ │ ├── mc100ept26d_33.dml

│ │ ├── mi.run

│ │ │ ├── 1sgx_dhstl15c2_out_ibs_PWR_All.sim

│ │ │ ├── 1sgx_sstl25c2_io_dm_ibs_GND_All.sim

│ │ │ ├── 1sgx_sstl25c2_io_dm_ibs_GND_Min.sim

│ │ │ ├── EP1SGX25F_11_1sgx_dhstl15c2_out_dml_GND_All.sim

│ │ │ ├── EP1SGX25F_11_1sgx_sstl25c2_io_dm_Output.sim

│ │ │ ├── EP1SGX25F_1_1sgx_sstl25c2_io_dm_Output.sim

│ │ │ ├── ep1sgx25f_1.dml.log

│ │ │ ├── ep1sgx25f_1.dml.parse

│ │ │ ├── ep1sgx25f_1.ibs.log

│ │ │ ├── ep1sgx25f_1.ibs.parse

│ │ │ ├── ep1sgx25f_1.ibs.version.txt

│ │ │ ├── ep1sgx25f_11.dml.log

│ │ │ ├── ep1sgx25f_11.dml.parse

│ │ │ ├── ep1sgx25f_11.ibs.log

│ │ │ ├── ep1sgx25f_11.ibs.parse

│ │ │ ├── ep1sgx25f_11.ibs.version.txt

│ │ │ ├── epc16q100.ibs.parse

│ │ │ ├── mc100ep139dt_33.dml.parse

│ │ │ ├── mc100ep33d_33.dml.parse

│ │ │ └── mc100ept26d_33.dml.parse

│ │ ├── net.dl

│ │ ├── net.dl,1

│ │ ├── net.dst

│ │ ├── net.dst,1

│ │ ├── s29jl064h_tsop.dml

│ │ ├── s29jl064h_tsop.dml,1

│ │ ├── s29jl064h_tsop.ibs

│ │ ├── signoise.run

│ │ │ ├── case1

│ │ │ ├── cases.cfg

│ │ │ └── cases.cfg,1

│ │ ├── sigwave.jrl

│ │ ├── sigwave.jrl,1

│ │ ├── tlsim.log

│ │ ├── tlsim.log,1

│ │ ├── tlsim.log,2

│ │ └── tlsim.log,3

│ ├── SI

│ │ ├── Channel

│ │ │ └── Lab

│ │ │ ├── 10G_test.cacfg

│ │ │ ├── 10G_with_jitter.cacfg

│ │ │ ├── 3rd_party_imp_response.txt

│ │ │ ├── Lab_01.top

│ │ │ ├── awesome.dml

│ │ │ ├── devices.dml

│ │ │ ├── dimm_discretesnew.dml

│ │ │ ├── equalizer.ami

│ │ │ ├── ibis_models.inc,1

│ │ │ ├── signoise.log

│ │ │ ├── signoise.log,1

│ │ │ ├── signoise.log,2

│ │ │ ├── signoise.log,3

│ │ │ ├── sigwave.jrl

│ │ │ ├── sigwave.jrl,1

│ │ │ ├── sigxp.jrl

│ │ │ ├── sigxp.jrl,1

│ │ │ └── sigxp.run

│ │ └── PDN

│ │ ├── pdn166_database

│ │ │ ├── Decoupling_Capacitors_Management.csv

│ │ │ ├── Decoupling_Capacitors_Report.csv

│ │ │ ├── PDN166_AC.brd

│ │ │ ├── PDN166_AC_2.brd

│ │ │ ├── PDN166_DC.brd

│ │ │ ├── PDN166_DC_2.brd

│ │ │ ├── PDN166_ME.brd

│ │ │ ├── PDN166_ME_2.brd

│ │ │ ├── PDN166_SN.brd

│ │ │ ├── PDN166_SN_2.brd

│ │ │ ├── PDN166_cap_mngmnt.brd

│ │ │ ├── PDN166_cap_mngmnt_2.brd

│ │ │ ├── PDN166_resonant.brd

│ │ │ ├── PartTableMapping.txt

│ │ │ ├── allegro.jrl

│ │ │ ├── allegro.jrl,1

│ │ │ ├── cap0402-ht0_56_fl.psm

│ │ │ ├── cap0805-ht1_45_fl.psm

│ │ │ ├── capacitors.ptf

│ │ │ ├── dimm_discretesnew.dml

│ │ │ ├── hdre0_45x0_5_pm0_35x0_5.pad

│ │ │ ├── master.tag

│ │ │ ├── pdns.run

│ │ │ ├── signoise.log

│ │ │ ├── signoise.log,1

│ │ │ ├── signoise.log,2

│ │ │ ├── signoise.log,3

│ │ │ ├── signoise.run

│ │ │ ├── sigwave.jrl

│ │ │ └── smd35x27.pad

│ │ └── ~$N166_What'sNew_Rev1_4.docx

│ ├── SQAdv_14_2(new).rar

│ └── diffPair

│ ├── CMCHOKE.dml

│ ├── CMCHOKE.ibs

│ ├── DIFFLOOPIN.top

│ ├── DIFFLOOPIN_trace.top

│ ├── DP_LOOPIN.top

│ ├── PCI1.brd

│ ├── PCI2.brd

│ ├── PCI3.brd

│ ├── PCI4.brd

│ ├── PCI5.brd

│ ├── SISWriteComps_buff

│ ├── allegro.jrl

│ ├── allegro.jrl,1

│ ├── atomic.dml

│ ├── atomic.ibs

│ ├── atomic_plcc44.dml

│ ├── atomic_plcc44.ibs

│ ├── atomic_trac1-1.txt

│ ├── batch_drc.log

│ ├── batch_drc.log,1

│ ├── batch_drc.log,2

│ ├── batch_drc.log,3

│ ├── cmpshape.log

│ ├── create_devices.log

│ ├── delete_layer_objects.rpt

│ ├── devices.dml

│ ├── devices.map

│ ├── diff_sim.top

│ ├── diffpair_auto.log

│ ├── diffpair_auto.log,1

│ ├── diffpair_auto.log,2

│ ├── diffpair_auto.log,3

│ ├── dimm_discretes.dml

│ ├── dump_libraries.log

│ ├── dv_autovoid.log

│ ├── genfeed.log

│ ├── hermon-6.txt

│ ├── ibis_models.inc,1

│ ├── inductor-52.txt

│ ├── interconn.iml

│ ├── interconn.iml,1

│ ├── led2x1-1.txt

│ ├── lib.dml

│ ├── lt1129-1.txt

│ ├── master.tag

│ ├── mergedml.log

│ ├── mi.run

│ │ ├── CMCHOKE.ibs.parse

│ │ ├── atomic.dml.parse

│ │ ├── atomic.ibs.log

│ │ ├── atomic.ibs.parse

│ │ ├── atomic_plcc44.ibs.parse

│ │ ├── devices.dml.parse

│ │ └── sunspot.ibs.parse

│ ├── monitor.sts

│ ├── pci-1.txt

│ ├── pcipinbot.pad

│ ├── pcipintop.pad

│ ├── pinView.dat

│ ├── place_txt.txt

│ ├── plctxt.log

│ ├── shape_islands.rpt

│ ├── signoise.log

│ ├── signoise.log,1

│ ├── signoise.log,2

│ ├── signoise.log,3

│ ├── signoise.run

│ │ ├── case1

│ │ │ ├── case.cfg

│ │ │ └── case.cfg,1

│ │ ├── case10

│ │ │ ├── case.cfg

│ │ │ └── case.cfg,1

│ │ ├── case2

│ │ │ ├── case.cfg

│ │ │ └── case.cfg,1

│ │ ├── case9

│ │ │ ├── case.cfg

│ │ │ └── case.cfg,1

│ │ ├── cases.cfg

│ │ ├── cases.cfg,1

│ │ ├── signoise.cfg

│ │ └── signoise.cfg,1

│ ├── sigwave.jrl

│ ├── sigwave.jrl,1

│ ├── sigxp.dml

│ ├── sigxp.dml,1

│ ├── sigxp.jrl

│ ├── sigxp.jrl,1

│ ├── sigxp.run

│ │ ├── case0

│ │ │ ├── case.cfg

│ │ │ ├── case.cfg,1

│ │ │ ├── projstate.dat

│ │ │ ├── projstate.dat,1

│ │ │ ├── sigsimcntl.dat

│ │ │ ├── sigsimres.dat

│ │ │ ├── sim1

│ │ │ └── waveforms

│ │ ├── cases.cfg

│ │ ├── cases.cfg,1

│ │ ├── signoise.cfg

│ │ └── signoise.cfg,1

│ ├── specctra.did

│ ├── specctra.log

│ ├── sunspot-1.txt

│ ├── sunspot.dml

│ ├── sunspot.dml,1

│ ├── sunspot.dml.txt

│ ├── sunspot.ibs

│ ├── sweep_rpt_tab.txt

│ ├── symbols

│ │ ├── 035c049p.pad

│ │ ├── 040c054p.pad

│ │ ├── 040s054p.pad

│ │ ├── 042c060p.pad

│ │ ├── 050s064p.pad

│ │ ├── 065c079p.pad

│ │ ├── 126npth.pad

│ │ ├── 131npth.pad

│ │ ├── 74f125-2.txt

│ │ ├── a1.dra

│ │ ├── a1.osm

│ │ ├── allegro.jrl

│ │ ├── allegro.jrl,1

│ │ ├── am29f010p-1.txt

│ │ ├── amp1045496-1.txt

│ │ ├── amp1045499-1.txt

│ │ ├── assembly-notes.bsm

│ │ ├── assembly-notes.dra

│ │ ├── bbsmhdr_40.dra

│ │ ├── bbsmhdr_40.psm

│ │ ├── bbsmhdr_80.dra

│ │ ├── bbsmhdr_80.psm

│ │ ├── bestsave.w

│ │ ├── board-notes.bsm

│ │ ├── board-notes.dra

│ │ ├── capacitor-1.txt

│ │ ├── capacitor-120.txt

│ │ ├── capacitor-196.txt

│ │ ├── capacitor-3.txt

│ │ ├── capacitor-319.txt

│ │ ├── capacitor-320.txt

│ │ ├── capacitor-322.txt

│ │ ├── capacitor-324.txt

│ │ ├── capacitor-337.txt

│ │ ├── capacitor-4.txt

│ │ ├── capacitor-560.txt

│ │ ├── capacitor-649.txt

│ │ ├── capacitor-656.txt

│ │ ├── capacitor-660.txt

│ │ ├── capacitor-661.txt

│ │ ├── cardfid-s.bsm

│ │ ├── cardfid-s.dra

│ │ ├── cardfid.pad

│ │ ├── cmchoke-5.txt

│ │ ├── compfid.pad

│ │ ├── diode-18.txt

│ │ ├── dip4t_300.dra

│ │ ├── dip4t_300.psm

│ │ ├── f73g1652.dra

│ │ ├── f73g1652.psm

│ │ ├── goldtab-pci-62.dra

│ │ ├── goldtab-pci-62.psm

│ │ ├── led2x1a.dra

│ │ ├── led2x1a.psm

│ │ ├── melfr.dra

│ │ ├── melfr.psm

│ │ ├── mpc-2.txt

│ │ ├── osc_smc-1.txt

│ │ ├── osc_smc-7.txt

│ │ ├── plcc32.dra

│ │ ├── plcc32.psm

│ │ ├── plcc44.dra

│ │ ├── plcc44.psm

│ │ ├── qfp184p65.dra

│ │ ├── qfp184p65.psm

│ │ ├── qfp208p5x.dra

│ │ ├── qfp208p5x.psm

│ │ ├── resistor-1744.txt

│ │ ├── resistor-1941.txt

│ │ ├── resistor-2084.txt

│ │ ├── resistor-2152.txt

│ │ ├── resistor-2183.txt

│ │ ├── resistor-2186.txt

│ │ ├── resistor-2187.txt

│ │ ├── resistor-2198.txt

│ │ ├── resistor-2199.txt

│ │ ├── resistor-2202.txt

│ │ ├── resistor-2204.txt

│ │ ├── resistor-2208.txt

│ │ ├── resistor-2209.txt

│ │ ├── resistor-2325.txt

│ │ ├── resistor-2326.txt

│ │ ├── resistor-2326__1.txt

│ │ ├── resistor-2347.txt

│ │ ├── resistor-2370.txt

│ │ ├── resistor-2473.txt

│ │ ├── rj45l8s2-1.txt

│ │ ├── s016x080.pad

│ │ ├── s024x080.pad

│ │ ├── s029x138.pad

│ │ ├── s040x050.pad

│ │ ├── s055x100.pad

│ │ ├── s065x100.pad

│ │ ├── s065x125a.pad

│ │ ├── s070x090.pad

│ │ ├── s070x095.pad

│ │ ├── s071x083.pad

│ │ ├── s0805.dra

│ │ ├── s0805.ssm

│ │ ├── s0805nv.pad

│ │ ├── s0805pro.dra

│ │ ├── s0805pro.ssm

│ │ ├── s080x016.pad

│ │ ├── s080x024.pad

│ │ ├── s080x040.pad

│ │ ├── s080x050.pad

│ │ ├── s080x055.pad

│ │ ├── s084x030.pad

│ │ ├── s095x011.pad

│ │ ├── s095x090.pad

│ │ ├── s100x040.pad

│ │ ├── s100x100.pad

│ │ ├── s1206.dra

│ │ ├── s1206.ssm

│ │ ├── s1206nv.pad

│ │ ├── s1206pro.dra

│ │ ├── s1206pro.ssm

│ │ ├── sky126.bsm

│ │ ├── sky126.dra

│ │ ├── skyline.bsm

│ │ ├── skyline.dra

│ │ ├── smc0805.dra

│ │ ├── smc0805.psm

│ │ ├── smc1206.dra

│ │ ├── smc1206.psm

│ │ ├── smc1210.dra

│ │ ├── smc1210.psm

│ │ ├── smc1311.dra

│ │ ├── smc1311.psm

│ │ ├── smc1812.dra

│ │ ├── smc1812.psm

│ │ ├── smc2312.dra

│ │ ├── smc2312.psm

│ │ ├── smc2816.dra

│ │ ├── smc2816.psm

│ │ ├── smc_osc.dra

│ │ ├── smc_osc.psm

│ │ ├── sod123.dra

│ │ ├── sod123.psm

│ │ ├── sod87.dra

│ │ ├── sod87.psm

│ │ ├── sog08_250.dra

│ │ ├── sog08_250.psm

│ │ ├── sog14_250.dra

│ │ ├── sog14_250.psm

│ │ ├── soj04_osc.dra

│ │ ├── soj04_osc.psm

│ │ ├── soj16_400x.dra

│ │ ├── soj16_400x.psm

│ │ ├── soj28_350.dra

│ │ ├── soj28_350.psm

│ │ ├── sot23pin.pad

│ │ ├── sot23pina.pad

│ │ ├── target.dra

│ │ ├── target.osm

│ │ ├── tv016c030.pad

│ │ ├── tv016c040.pad

│ │ ├── v016c030.pad

│ │ └── v125c139p.pad

│ ├── tc5589j25-1.txt

│ ├── tech.tech

│ ├── techfile.log

│ ├── translate.log

│ ├── zener2-6.txt

│ └── zener2-7.txt

├── 6~7章 工程文件

│ ├── DDR3_ADDR.top

│ ├── Run.Log

│ ├── allegro.jrl

│ ├── allegro.jrl,1

│ ├── devices.dml

│ ├── devices.dml,1

│ ├── ibis_models.inc,1

│ ├── interconn.iml

│ ├── interconn.iml,1

│ ├── license_use.log

│ ├── master.tag

│ ├── mosaic.log

│ ├── mosaic_bak.log

│ ├── my_ddr3_mod1.brd

│ ├── my_ddr3_mod2.brd

│ ├── my_ddr3_mod3_1st.brd

│ ├── my_ddr3_mod3_fp.brd

│ ├── my_ddr3_mod3_rte.brd

│ ├── my_ddr3_mod4_no_tab.brd

│ ├── my_ddr3_mod4_tab.brd

│ ├── my_ddr3_mod4_tab.brd.lck

│ ├── my_ddr3_mod4_tab_gre.log

│ ├── my_ddr3_mod4_tab_gre_bak.log

│ ├── my_lib

│ │ └── Source_data

│ │ ├── in882lvgs02_135_v1p0_nopkg.ibs

│ │ └── v70sr1p2_1p35_nopkg.ibs

│ ├── no_tabs.sim

│ ├── quickplace.log

│ ├── quickplace.log,1

│ ├── signoise.log

│ ├── signoise.log,1

│ ├── signoise.log,2

│ ├── signoise.log,3

│ ├── signoise.run

│ │ ├── case1

│ │ │ ├── case.cfg

│ │ │ ├── case.cfg,1

│ │ │ ├── projstate.dat

│ │ │ ├── projstate.dat,1

│ │ │ ├── sigsimcntl.dat

│ │ │ ├── sigsimres.dat

│ │ │ └── waveforms

│ │ ├── cases.cfg

│ │ ├── cases.cfg,1

│ │ ├── report.html

│ │ ├── signoise.cfg

│ │ └── signoise.cfg,1

│ ├── sigxp.dml

│ ├── sigxp.dml,1

│ ├── sigxp.jrl

│ ├── sigxp.jrl,1

│ ├── sigxp.run

│ │ ├── case0

│ │ │ ├── case.cfg

│ │ │ ├── projstate.dat

│ │ │ ├── projstate.dat,1

│ │ │ ├── sigsimcntl.dat

│ │ │ ├── sigsimres.dat

│ │ │ └── waveforms

│ │ ├── cases.cfg

│ │ ├── cases.cfg,1

│ │ ├── signoise.cfg

│ │ └── signoise.cfg,1

│ ├── sweep_rpt_tab.txt

│ ├── topology.log.copy

│ └── unnamed.log

├── 8~9章 工程文件

│ └── #11 - Signal Integrity Signoff

│ ├── DDR4_Lab_database

│ │ ├── PCB_SPDGEN.tcl

│ │ ├── Run.Log

│ │ ├── Trace_Pad_Library

│ │ │ ├── spreadtrum_ref_TracePadLibrary.log

│ │ │ ├── spreadtrum_ref_lossless.lib

│ │ │ └── spreadtrum_ref_lossless__16.0.1.0.lib

│ │ ├── bufferdelay

│ │ │ └── Controller_ssi_pba_ex_Controller_BufferDelay.txt

│ │ ├── ddr.ssix

│ │ ├── ddr_with_vrm.ssix

│ │ ├── history

│ │ │ ├── 1

│ │ │ ├── 10

│ │ │ ├── 11

│ │ │ ├── 12

│ │ │ ├── 13

│ │ │ ├── 14

│ │ │ ├── 15

│ │ │ ├── 16

│ │ │ ├── 2

│ │ │ ├── 3

│ │ │ ├── 4

│ │ │ ├── 5

│ │ │ ├── 6

│ │ │ ├── 7

│ │ │ ├── 8

│ │ │ ├── 9

│ │ │ ├── ac

│ │ │ └── buffer

│ │ ├── result

│ │ │ ├── Controller_ssi_pba_ex.sp

│ │ │ ├── Memory1_ssi_pba_ex.sp

│ │ │ ├── ac

│ │ │ └── buffer

│ │ ├── spreadtrum_ref.spd

│ │ ├── spreadtrum_ref_03222016_084537

│ │ │ ├── CKTDef.sp

│ │ │ ├── ViaModel.sp

│ │ │ ├── WireLeadModel.sp

│ │ │ └── Wmodel.sp

│ │ ├── spreadtrum_ref_03222016_084537.sp

│ │ ├── spreadtrum_ref_07152017_113131

│ │ │ ├── CKTDef.sp

│ │ │ ├── ViaModel.sp

│ │ │ ├── WireLeadModel.sp

│ │ │ └── Wmodel.sp

│ │ ├── spreadtrum_ref_07152017_113131.sp

│ │ ├── spreadtrum_ref_07152017_135240

│ │ │ ├── CKTDef.sp

│ │ │ ├── ViaModel.sp

│ │ │ ├── WireLeadModel.sp

│ │ │ └── Wmodel.sp

│ │ ├── spreadtrum_ref_07152017_135240.sp

│ │ ├── spreadtrum_ref_07152017_140747

│ │ │ ├── CKTDef.sp

│ │ │ ├── ViaModel.sp

│ │ │ ├── WireLeadModel.sp

│ │ │ └── Wmodel.sp

│ │ ├── spreadtrum_ref_07152017_140747.sp

│ │ ├── spreadtrum_ref_07152017_151704

│ │ │ ├── CKTDef.sp

│ │ │ ├── ViaModel.sp

│ │ │ ├── WireLeadModel.sp

│ │ │ └── Wmodel.sp

│ │ ├── spreadtrum_ref_07152017_151704.sp

│ │ ├── spreadtrum_ref_07152017_165812

│ │ │ ├── CKTDef.sp

│ │ │ ├── ViaModel.sp

│ │ │ ├── WireLeadModel.sp

│ │ │ └── Wmodel.sp

│ │ ├── spreadtrum_ref_07152017_165812.sp

│ │ ├── spreadtrum_ref_07182017_170926

│ │ │ ├── CKTDef.sp

│ │ │ ├── ViaModel.sp

│ │ │ ├── WireLeadModel.sp

│ │ │ └── Wmodel.sp

│ │ ├── spreadtrum_ref_07182017_170926.sp

│ │ ├── spreadtrum_ref_GENERATOR.err

│ │ ├── spreadtrum_ref_spdsim.err

│ │ ├── spreadtrum_ref_spdsim_goldenparser.log

│ │ ├── ssi_pba_ex.ibs

│ │ ├── vrm1.sp

│ │ ├── vrm2.sp

│ │ └── vrm3.sp

│ ├── SW_patch_for_DDR4_Lab

│ │ ├── SystemSI.exe

│ │ ├── SystemSI_ParallelBus.dll

│ │ ├── SystemSI_SerialLink.dll

│ │ └── SystemSI_SystemExplorer.dll

│ ├── history

│ ├── lab_AMI_Builder

│ │ └── lab_AMI_Builder

│ │ ├── TEC_Armor_MR_C2C_Channel_THRU.s4p

│ │ ├── ami_builder

│ │ ├── chan_tek.sp

│ │ ├── history

│ │ ├── lab_AMI_Builder.ssix

│ │ ├── lab_AMI_Builder1.ssix

│ │ ├── lab_AMI_Builder_rx.ssix

│ │ ├── lab_AMI_Builder_tx.ssix

│ │ ├── result

│ │ ├── rx_bhvr.sp

│ │ └── tx_bhvr.sp

│ └── result

│ └── Terminator1.sp

└── Cadence高速电路板设计与仿真(第6版)—信号与电源完整性分析实例.rar

169 directories, 997 files

网友评论

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

支持(0) 盖楼(回复)