实例介绍

【实例截图】

【核心代码】

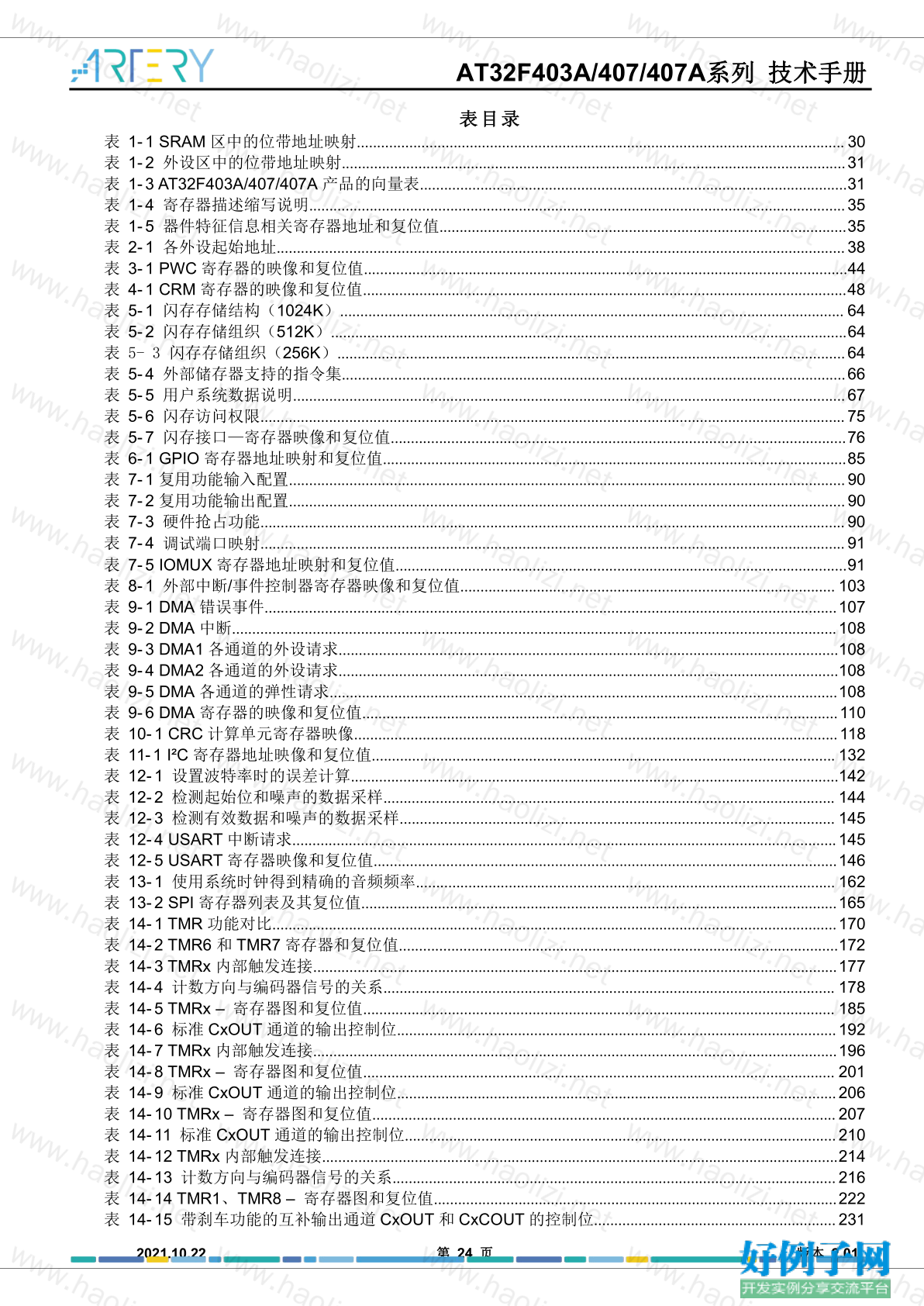

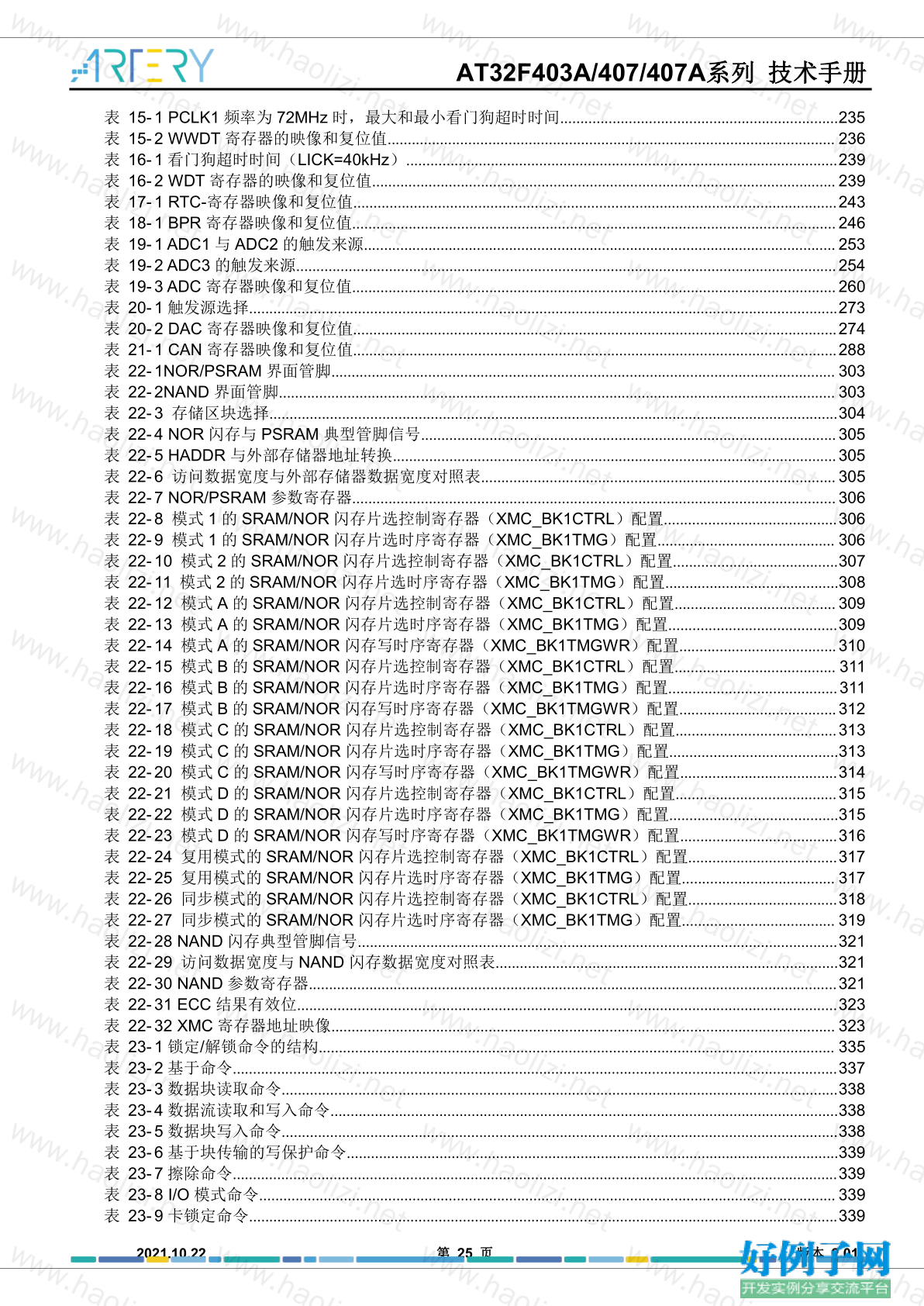

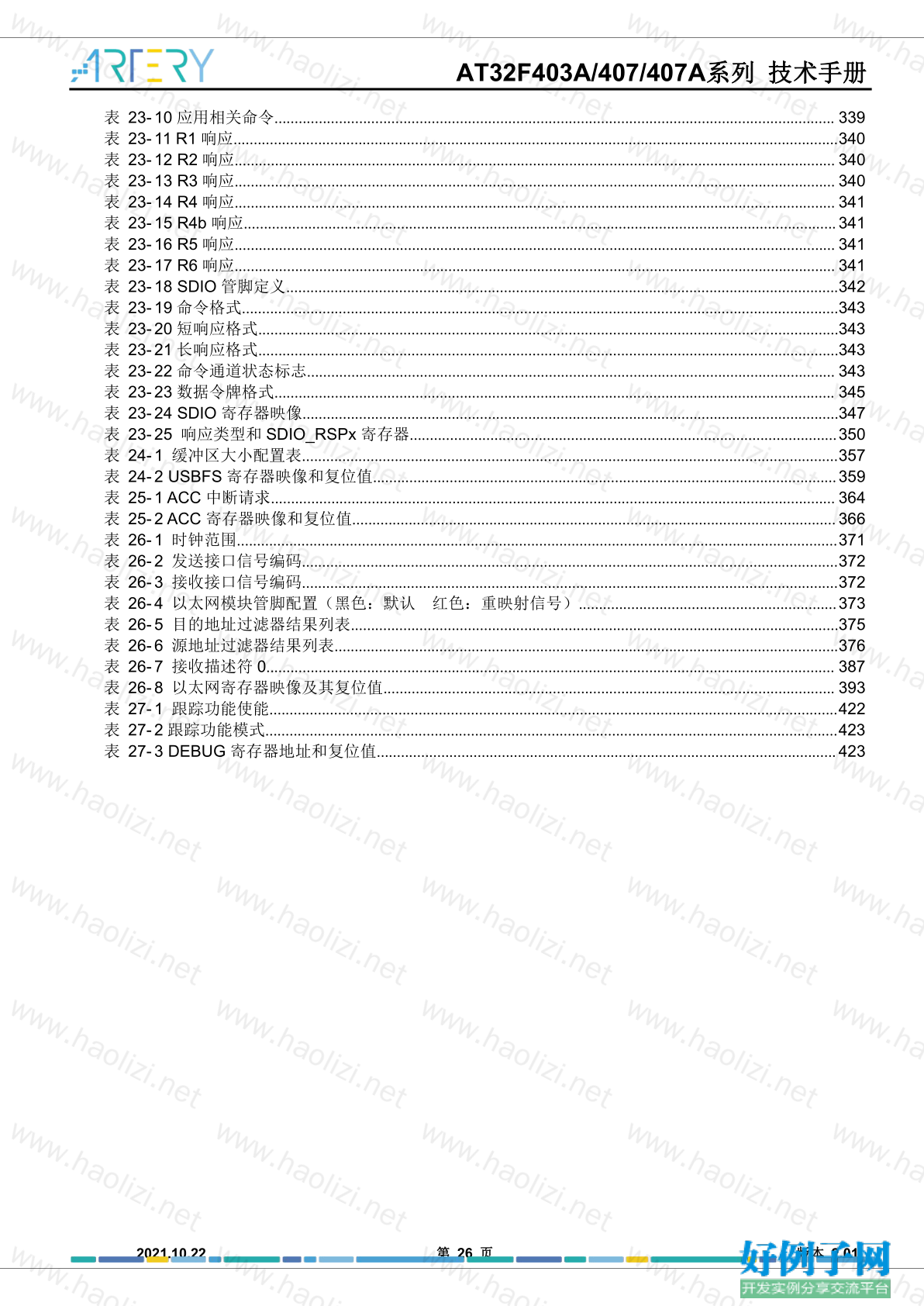

目 目 录

1 系统架构....................................................................................................................................................27

1.1 系统概述............................................................................................................................................ 29

1.1.1 ARM Cortex TM -M4F处理器..................................................................................................29

1.1.2 位带.......................................................................................................................................... 29

1.1.3 中断和异常向量....................................................................................................................31

1.1.4 系统嘀嗒定时器(SysTick).............................................................................................34

1.1.5 复位流程.................................................................................................................................34

1.2 寄存器描述缩写说明......................................................................................................................35

1.3 器件特征信息...................................................................................................................................35

1.3.1 闪存容量寄存器....................................................................................................................36

1.3.2 器件电子签名........................................................................................................................36

2 存储器资源................................................................................................................................................37

2.1 内部存储器地址映射......................................................................................................................37

2.2 Flash存储器.......................................................................................................................................37

2.3 SRAM存储器......................................................................................................................................38

2.4 外设地址映射...................................................................................................................................38

3 电源控制(PWC)...................................................................................................................................41

3.1 简介......................................................................................................................................................41

3.2 主要特点............................................................................................................................................ 41

3.3 上电低电压复位...............................................................................................................................41

3.4 电压监测器(PVM)......................................................................................................................42

3.5 电源域划分........................................................................................................................................42

3.6 省电模式............................................................................................................................................ 43

3.7 PWC寄存器........................................................................................................................................ 44

3.7.1 电源控制寄存器(PWC_CTRL)...................................................................................... 44

3.7.2 电源控制及状态寄存器(PWC_CTRLSTS)..................................................................45

4 时钟和复位管理(CRM).....................................................................................................................46

4.1 时钟......................................................................................................................................................46

4.1.1 时钟源......................................................................................................................................46

4.1.2 系统时钟.................................................................................................................................47

4.1.3 外设时钟.................................................................................................................................47

4.1.4 时钟失效检测........................................................................................................................47

4.1.5 自动滑顺频率切换...............................................................................................................47

4.1.6 内部时钟输出........................................................................................................................47

4.1.7 中断.......................................................................................................................................... 48

4.2 复位......................................................................................................................................................48

4.2.1 系统复位.................................................................................................................................48

4.2.2 电池供电域复位....................................................................................................................48

4.3 CRM寄存器........................................................................................................................................ 48

4.3.1 时钟控制寄存器(CRM_CTRL)...................................................................................... 49

4.3.2 时钟配置寄存器(CRM_CFG)........................................................................................50

4.3.3 时钟中断寄存器 (CRM_CLKINT)................................................................................52

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 3 页 页 版本 版本 2.01

4.3.4 APB2外设复位寄存器(CRM_APB2RST).....................................................................53

4.3.5 APB1外设复位寄存器(CRM_APB1RST).....................................................................54

4.3.6 AHB外设时钟使能寄存器(CRM_AHBEN)................................................................. 56

4.3.7 APB2外设时钟使能寄存器(CRM_APB2EN)..............................................................57

4.3.8 APB1外设时钟使能寄存器(CRM_APB1EN)..............................................................58

4.3.9 电池供电域控制寄存器(CRM_BPDC)........................................................................60

4.3.10 控制/状态寄存器(CRM_CTRLSTS)..............................................................................60

4.3.11 AHB外设复位寄存器(CRM_AHBRST).........................................................................61

4.3.12 额外寄存器1(CRM_MISC1).......................................................................................... 61

4.3.13 额外寄存器2(CRM_MISC2).......................................................................................... 62

4.3.14 额外寄存器3(CRM_MISC3).......................................................................................... 62

4.3.15 中断映射寄存器(CRM_INTMAP)................................................................................ 63

5 闪存控制器(FLASH)...........................................................................................................................64

5.1 FLASH介绍..........................................................................................................................................64

5.2 主存储器操作...................................................................................................................................68

5.2.1 解锁/锁定............................................................................................................................... 68

5.2.2 擦除.......................................................................................................................................... 69

5.2.3 编程.......................................................................................................................................... 70

5.2.4 读取.......................................................................................................................................... 71

5.3 外部存储器操作...............................................................................................................................71

5.4 用户系统数据区操作......................................................................................................................72

5.4.1 解锁/锁定............................................................................................................................... 72

5.4.2 擦除.......................................................................................................................................... 72

5.4.3 编程.......................................................................................................................................... 73

5.4.4 读取.......................................................................................................................................... 74

5.5 闪存保护............................................................................................................................................ 74

5.5.1 访问保护.................................................................................................................................74

5.5.2 擦写保护.................................................................................................................................75

5.6 特殊功能............................................................................................................................................ 75

5.6.1 安全库区设定........................................................................................................................75

5.7 FLASH寄存器..................................................................................................................................... 76

5.7.1 闪存性能选择寄存器(FLASH_PSR)............................................................................ 77

5.7.2 闪存解锁寄存器(FLASH_UNLOCK).............................................................................77

5.7.3 闪存用户系统数据解锁寄存器(FLASH_USD_UNLOCK)........................................77

5.7.4 闪存状态寄存器(FLASH_STS)......................................................................................77

5.7.5 闪存控制寄存器(FLASH_CTRL)................................................................................... 78

5.7.6 闪存地址寄存器(FLASH_ADDR)..................................................................................78

5.7.7 用户系统数据寄存器(FLASH_USD)............................................................................78

5.7.8 擦除编程保护状态寄存器(FLASH_EPPS).................................................................79

5.7.9 闪存解锁寄存器2(FLASH_UNLOCK2)........................................................................ 79

5.7.10 闪存状态寄存器2(FLASH_STS2)................................................................................. 79

5.7.11 闪存控制寄存器2(FLASH_CTRL2)...............................................................................79

5.7.12 闪存地址寄存器2(FLASH_ADDR2).............................................................................80

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 4 页 页 版本 版本 2.01

5.7.13 闪存解锁寄存器3(FLASH_UNLOCK3)........................................................................ 80

5.7.14 闪存选择寄存器(FLASH_SELECT)...............................................................................80

5.7.15 闪存状态寄存器3(FLASH_STS3)................................................................................. 80

5.7.16 闪存控制寄存器3(FLASH_CTRL3)...............................................................................80

5.7.17 闪存地址寄存器3(FLASH_ADDR3).............................................................................81

5.7.18 闪存解密地址寄存器(FLASH_DA)..............................................................................81

5.7.19 闪存安全库区状态寄存器0(SLIB_STS0)...................................................................81

5.7.20 闪存安全库区状态寄存器1(SLIB_STS1)...................................................................81

5.7.21 闪存安全库区密码清除寄存器(SLIB_PWD_CLR)...................................................82

5.7.22 闪存安全库区额外状态寄存器(SLIB_MISC_STS).................................................. 82

5.7.23 闪存安全库区密码设定寄存器(SLIB_SET_PWD)...................................................82

5.7.24 闪存安全库区地址设定寄存器(SLIB_SET_RANGE)...............................................82

5.7.25 闪存安全库区解锁寄存器(SLIB_UNLOCK).............................................................. 83

5.7.26 闪存CRC校验控制寄存器(FLASH_CRC_CTRL)......................................................... 83

5.7.27 闪存CRC校验结果寄存器(FLASH_CRC_CHKR)........................................................ 83

6 通用功能输入输出(GPIO)............................................................................................................... 84

6.1 简介......................................................................................................................................................84

6.2 功能描述............................................................................................................................................ 84

6.2.1 GPIO结构.................................................................................................................................84

6.2.2 GPIO复位状态........................................................................................................................84

6.2.3 通用功能输入配置...............................................................................................................85

6.2.4 模拟输入/输出配置.............................................................................................................85

6.2.5 通用功能输出配置...............................................................................................................85

6.2.6 I/O端口保护...........................................................................................................................85

6.3 GPIO寄存器........................................................................................................................................85

6.3.1 GPIO配置低寄存器(GPIOx_CFGLR)(x=A..E).......................................................86

6.3.2 GPIO配置高寄存器(GPIOx_CFGHR)(A..E)...........................................................86

6.3.3 GPIO输入数据寄存器(GPIOx_IDT)(x=A..E)........................................................86

6.3.4 GPIO输出数据寄存器(GPIOx_ODT)(x=A..E)...................................................... 87

6.3.5 GPIO设置/清除寄存器(GPIOx_SCR)(x=A..E)......................................................87

6.3.6 GPIO清除寄存器(GPIOx_CLR)(x=A..E).................................................................87

6.3.7 GPIO写保护寄存器(GPIOx_WPR)(x=A..E)..........................................................87

6.3.8 GPIO极大电流推动/吸入能力切换控制寄存器(GPIOx_HDRV)(x=A..E)....87

7 复用功能输入输出(IOMUX)............................................................................................................89

7.1 简介......................................................................................................................................................89

7.2 功能描述............................................................................................................................................ 89

7.2.1 IOMUX结构.............................................................................................................................89

7.2.2 复用功能输入配置...............................................................................................................89

7.2.3 复用功能输出或双向复用功能配置...............................................................................90

7.2.4 外设复用功能管脚配置......................................................................................................90

7.2.5 IOMUX映射优先级............................................................................................................... 90

7.2.5.1 硬件抢占功能.............................................................................................................90

7.2.5.2 调试端口优先.............................................................................................................90

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 5 页 页 版本 版本 2.01

7.2.5.3 其他外设输出优先级关系......................................................................................91

7.2.6 外部中断/唤醒线..................................................................................................................91

7.3 IOMUX寄存器....................................................................................................................................91

7.3.1 事件输出控制寄存器(IOMUX_EVTOUT)...................................................................92

7.3.2 IO复用重映射寄存器(IOMUX_REMAP).....................................................................92

7.3.3 复用外部中断配置寄存器1(IOMUX_EXINTC1).......................................................94

7.3.4 复用外部中断配置寄存器2(IOMUX_EXINTC2).......................................................95

7.3.5 复用外部中断配置寄存器3(IOMUX_EXINTC3).......................................................95

7.3.6 复用外部中断配置寄存器4(IOMUX_EXINTC4).......................................................96

7.3.7 IO复用重映射寄存器2(IOMUX_REMAP2)................................................................97

7.3.8 IO复用重映射寄存器3(IOMUX_REMAP3)................................................................97

7.3.9 IO复用重映射寄存器4(IOMUX_REMAP4)................................................................97

7.3.10 IO复用重映射寄存器5(IOMUX_REMAP5)................................................................98

7.3.11 IO复用重映射寄存器6(IOMUX_REMAP6)................................................................99

7.3.12 IO复用重映射寄存器7(IOMUX_REMAP7)..............................................................100

7.3.13 IO复用重映射寄存器8(IOMUX_REMAP8)..............................................................101

8 外部中断/事件控制器(EXINT).....................................................................................................102

8.1 EXINT介绍........................................................................................................................................102

8.2 功能描述和配置流程...................................................................................................................102

8.3 EXINT寄存器描述...........................................................................................................................103

8.3.1 中断使能寄存器(EXINT_INTEN)...............................................................................103

8.3.2 事件使能寄存器(EXINT_EVTEN)...............................................................................103

8.3.3 极性配置寄存器1(EXINT_POLCFG1)....................................................................... 103

8.3.4 极性配置寄存器2(EXINT_POLCFG2)....................................................................... 103

8.3.5 软件触发寄存器(EXINT_SWTRG).............................................................................104

8.3.6 中断状态寄存器(EXINT_INTSTS)..............................................................................104

9 DMA控制器(DMA)...........................................................................................................................105

9.1 简介...................................................................................................................................................105

9.2 特性...................................................................................................................................................105

9.3 功能描述..........................................................................................................................................105

9.3.1 通道配置...............................................................................................................................105

9.3.2 握手机制...............................................................................................................................106

9.3.3 仲裁........................................................................................................................................106

9.3.4 可编程数据传输宽度........................................................................................................106

9.3.5 错误事件...............................................................................................................................107

9.3.6 中断........................................................................................................................................107

9.3.7 DMA固定请求映射.............................................................................................................108

9.3.8 DMA弹性请求映射.............................................................................................................108

9.4 DMA寄存器......................................................................................................................................109

9.4.1 DMA中断状态寄存器(DMA_STS).............................................................................110

9.4.2 DMA中断标志清除寄存器(DMA_CLR)....................................................................112

9.4.3 DMA通道x配置寄存器(DMA_CxCTRL)(x = 1…7).............................................114

9.4.4 DMA通道x数据传输量寄存器(DMA_CxDTCNT)(x = 1…7)........................... 115

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 6 页 页 版本 版本 2.01

9.4.5 DMA通道x外设地址寄存器(DMA_CxPADDR)(x = 1…7)................................116

9.4.6 DMA通道x存储器地址寄存器(DMA_CxMADDR)(x = 1…7)..........................116

9.4.7 通道来源寄存器0(DMA_SRC_SEL0).........................................................................117

9.4.8 通道来源寄存器1(DMA_SRC_SEL1)........................................................................ 117

10 CRC计算单元(CRC)..........................................................................................................................118

10.1 CRC介绍............................................................................................................................................118

10.2 CRC寄存器....................................................................................................................................... 118

10.2.1 数据寄存器(CRC_DT)...................................................................................................118

10.2.2 通用数据寄存器(CRC_CDT).......................................................................................118

10.2.3 控制寄存器(CRC_CTRL)...............................................................................................118

10.2.4 初始化寄存器(CRC_IDT).............................................................................................119

11 I 2 C接口......................................................................................................................................................120

11.1 I 2 C简介..............................................................................................................................................120

11.2 I 2 C主要特点.....................................................................................................................................120

11.3 I 2 C总线特性.....................................................................................................................................120

11.4 I 2 C接口..............................................................................................................................................120

11.4.1 I 2 C从机通信流程................................................................................................................ 123

11.4.2 I 2 C主机通信流程................................................................................................................ 124

11.4.3 利用DMA传输......................................................................................................................129

11.4.4 SMBus.....................................................................................................................................130

11.4.5 I 2 C中断请求..........................................................................................................................132

11.4.6 I 2 C调试模式..........................................................................................................................132

11.5 I 2 C寄存器描述................................................................................................................................132

11.5.1 控制寄存器1(I2C_CTRL1).................................................................................................132

11.5.2 控制寄存器2(I2C_CTRL2).................................................................................................134

11.5.3 自身地址寄存器1(I2C_OADDR1)....................................................................................134

11.5.4 自身地址寄存器2(I2C_OADDR2)....................................................................................134

11.5.5 数据寄存器(I2C_DT)..........................................................................................................135

11.5.6 状态寄存器1(I2C_STS1)....................................................................................................135

11.5.7 状态寄存器2(I2C_STS2)....................................................................................................136

11.5.8 时钟控制寄存器(I2C_CLKCTRL)......................................................................................137

12 通用同步异步收发器(USART)......................................................................................................139

12.1 USART介绍.......................................................................................................................................139

12.2 全双工半双工选择器简述和配置流程...................................................................................140

12.3 模式选择器简述和配置流程......................................................................................................140

12.3.1 模式选择器简述.................................................................................................................140

12.3.2 模式选择器配置方法........................................................................................................140

12.4 USART帧格式简述和配置流程.................................................................................................. 141

12.5 DMA传输简述和配置流程..........................................................................................................141

12.5.1 DMA发送配置流程.............................................................................................................141

12.5.2 DMA接收配置流程.............................................................................................................141

12.6 波特率发生器简述及配置流程.................................................................................................142

12.6.1 波特率发生器简述.............................................................................................................142

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 7 页 页 版本 版本 2.01

12.6.2 波特率发生器配置方法................................................................................................... 142

12.7 发送器简述和配置流程...............................................................................................................143

12.7.1 发送器简述.......................................................................................................................... 143

12.7.2 发送器配置流程.................................................................................................................143

12.8 接收器简述和配置流程...............................................................................................................143

12.8.1 接收器简述.......................................................................................................................... 143

12.8.2 接收器配置流程.................................................................................................................143

12.8.3 起始侦测和噪声检测........................................................................................................144

12.9 中断...................................................................................................................................................145

12.10I/O管脚控制....................................................................................................................................146

12.11USART寄存器描述.........................................................................................................................146

12.11.1 状态寄存器(USART_STS)............................................................................................146

12.11.2 数据寄存器(USART_DT)..............................................................................................147

12.11.3 波特比率寄存器(USART_BAUDR)............................................................................147

12.11.4 控制寄存器1(USART_CTRL1).....................................................................................147

12.11.5 控制寄存器2(USART_CTRL2).....................................................................................148

12.11.6 控制寄存器3(USART_CTRL3).....................................................................................149

12.11.7 保护时间和预分频寄存器(GDIV)............................................................................150

13 串行外设接口(SPI)..........................................................................................................................151

13.1 串行外设接口(SPI)简介.........................................................................................................151

13.2 SPI功能描述.................................................................................................................................... 151

13.2.1 SPI简述..................................................................................................................................151

13.2.2 全双工半双工选择器简述和配置流程........................................................................152

13.2.3 CS控制器简述和配置流程...............................................................................................153

13.2.4 SPI_SCK控制器简述和配置流程.................................................................................... 154

13.2.5 CRC简述和配置流程..........................................................................................................154

13.2.6 DMA传输简述和配置流程...............................................................................................155

13.2.7 发送器简述和配置流程................................................................................................... 155

13.2.8 接收器简述和配置流程................................................................................................... 156

13.2.9 中断........................................................................................................................................157

13.2.10 IO管脚控制...........................................................................................................................157

13.2.11 注意事项...............................................................................................................................157

13.3 I 2 S功能描述.....................................................................................................................................157

13.3.1 I 2 S简述...................................................................................................................................157

13.3.2 I 2 S 全双工............................................................................................................................158

13.3.3 操作模式选择器简述和配置流程.................................................................................159

13.3.4 音频协议选择器简述和配置流程.................................................................................160

13.3.5 I2S_CLK控制器简述和配置流程.....................................................................................161

13.3.6 DMA传输简述和配置流程...............................................................................................163

13.3.7 发送器接收器简述和配置流程......................................................................................164

13.3.8 中断........................................................................................................................................165

13.3.9 I0管脚控制........................................................................................................................... 165

13.4 SPI寄存器.........................................................................................................................................165

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 8 页 页 版本 版本 2.01

13.4.1 SPI控制寄存器1(SPI_CTRL1)(I 2 S模式下不使用)............................................165

13.4.2 SPI控制寄存器2(SPI_CTRL2)......................................................................................167

13.4.3 SPI状态寄存器(SPI_STS).............................................................................................167

13.4.4 SPI数据寄存器(SPI_DT).............................................................................................. 168

13.4.5 SPICRC多项式寄存器(SPI_CPOLY)(I 2 S模式下不使用)..................................168

13.4.6 SPIRxCRC寄存器(SPI_RCRC)(I 2 S模式下不使用)............................................. 168

13.4.7 SPITxCRC寄存器(SPI_TCRC)....................................................................................... 168

13.4.8 SPI_I2S配置寄存器(SPI_I2SCTRL).............................................................................168

13.4.9 SPI_I2S预分频寄存器(SPI_I2SCLKP)........................................................................169

14 定时器(TIMER)................................................................................................................................. 170

14.1 基本定时器(TMR6和TMR7).................................................................................................. 170

14.1.1 TMR6和TMR7简介..............................................................................................................170

14.1.2 TMR6和TMR7的主要特性................................................................................................171

14.1.3 TMR6和TMR7的功能......................................................................................................... 171

14.1.3.1 计数时钟................................................................................................................... 171

14.1.3.2 计数模式................................................................................................................... 171

14.1.3.3 调试模式................................................................................................................... 172

14.1.4 TMR6和TMR7寄存器......................................................................................................... 172

14.1.4.1 TMR6 和TMR7控制寄存器1(TMRx_CTRL1)....................................... 172

14.1.4.2 TMR6和TMR7控制寄存器2(TMRx_CTRL2)..........................................173

14.1.4.3 TMR6和TMR7 DMA/中断使能寄存器(TMRx_IDEN)..........................173

14.1.4.4 TMR6和TMR7中断状态寄存器(TMRx_ISTS)....................................... 173

14.1.4.5 TMR6和TMR7软件事件寄存器(TMRx_SWEVT)..................................173

14.1.4.6 TMR6和TMR7计数值(TMRx_CVAL)........................................................173

14.1.4.7 TMR6和TMR7分频系数(TMRx_DIV)........................................................174

14.1.4.8 TMR6和TMR7周期寄存器(TMRx_PR).................................................... 174

14.2 通用定时器(TMR2到TMR5).................................................................................................. 175

14.2.1 TMRx简介..............................................................................................................................175

14.2.2 TMRx主要功能.................................................................................................................... 175

14.2.3 TMRx功能描述.................................................................................................................... 175

14.2.3.1 计数时钟................................................................................................................... 175

14.2.3.2 计数模式................................................................................................................... 177

14.2.3.3 TMR输入部分..........................................................................................................179

14.2.3.4 TMR输出部分..........................................................................................................180

14.2.3.5 定时器同步...............................................................................................................182

14.2.3.6 调试模式................................................................................................................... 184

14.2.4 TMRx寄存器描述................................................................................................................185

14.2.4.1 控制寄存器1(TMRx_CTRL1).......................................................................185

14.2.4.2 控制寄存器2(TMRx_CTRL2).......................................................................186

14.2.4.3 次定时器控制寄存器(TMRx_STCTRL)....................................................186

14.2.4.4 DMA/中断使能寄存器(TMRx_IDEN)........................................................187

14.2.4.5 中断状态寄存器(TMRx_ISTS)....................................................................188

14.2.4.6 软件事件寄存器(TMRx_SWEVT).............................................................. 189

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 9 页 页 版本 版本 2.01

14.2.4.7 通道模式寄存器1(TMRx_CM1).................................................................. 189

14.2.4.8 通道模式寄存器2(TMRx_CM2).................................................................. 191

14.2.4.9 通道控制寄存器(TMRx_CCTRL)............................................................... 192

14.2.4.10 计数值(TMRx_CVAL).....................................................................................193

14.2.4.11 分频系数(TMRx_DIV).................................................................................... 193

14.2.4.12 周期寄存器(TMRx_PR).................................................................................193

14.2.4.13 通道1数据寄存器(TMRx_C1DT)................................................................193

14.2.4.14 通道2数据寄存器(TMRx_C2DT)................................................................193

14.2.4.15 通道3数据寄存器(TMRx_C3DT)................................................................193

14.2.4.16 通道4数据寄存器(TMRx_C4DT)................................................................194

14.2.4.17 DMA控制寄存器(TMRx_DMACTRL)........................................................194

14.2.4.18 DMA数据寄存器(TMRx_DMADT)..............................................................194

14.3 通用定时器(TMR9到TMR14)................................................................................................195

14.3.1 TMRx简介..............................................................................................................................195

14.3.2 TMRx主要特性.................................................................................................................... 195

14.3.2.1 TMR9和TMR12主要特性....................................................................................195

14.3.2.2 TMR10、TMR11、TMR13和 TMR14主要特性.........................................195

14.3.3 TMRx功能描述.................................................................................................................... 196

14.3.3.1 计数时钟................................................................................................................... 196

14.3.3.2 计数模式................................................................................................................... 197

14.3.3.3 TMR输入部分..........................................................................................................197

14.3.3.4 TMR输出部分..........................................................................................................198

14.3.3.5 TMR同步...................................................................................................................200

14.3.3.6 调试模式................................................................................................................... 201

14.3.4 TMR9和TMR12寄存器描述..............................................................................................201

14.3.4.1 控制寄存器 1(TMRx_CTRL1)....................................................................202

14.3.4.2 次定时器控制寄存器(TMRx_STCTRL)....................................................202

14.3.4.3 DMA/中断使能寄存器(TMRx_IDEN)........................................................203

14.3.4.4 中断状态寄存器(TMRx_ISTS)....................................................................203

14.3.4.5 软件事件寄存器(TMRx_SWEVT).............................................................. 203

14.3.4.6 通道模式寄存器1(TMRx_CM1).................................................................. 204

14.3.4.7 通道控制寄存器(TMRx_CCTRL)............................................................... 206

14.3.4.8 计数器(TMRx_CVAL).....................................................................................206

14.3.4.9 预分频器(TMRx_DIV).................................................................................... 206

14.3.4.10 周期寄存器(TMRx_PR).................................................................................206

14.3.4.11 通道1数据寄存器(TMRx_C1DT)................................................................206

14.3.4.12 通道2数据寄存器(TMRx_C2DT)................................................................207

14.3.5 TMR10、TMR11、TMR13和TMR14寄存器描述........................................................ 207

14.3.5.1 控制寄存器1(TMRx_CTRL1).......................................................................207

14.3.5.2 DMA/中断使能寄存器(TMRx_IDEN)........................................................208

14.3.5.3 中断状态寄存器(TMRx_ISTS)....................................................................208

14.3.5.4 软件事件寄存器(TMRx_SWEVT).............................................................. 208

14.3.5.5 通道模式寄存器1(TMRx_CM1).................................................................. 208

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 10 页 页 版本 版本 2.01

14.3.5.6 通道控制寄存器(TMRx_CCTRL)............................................................... 210

14.3.5.7 计数值(TMRx_CVAL).....................................................................................210

14.3.5.8 预分频器(TMRx_DIV).................................................................................... 210

14.3.5.9 周期寄存器(TMRx_PR).................................................................................211

14.3.5.10 通道1数据寄存器(TMRx_C1DT)................................................................211

14.4 高级控制定时器(TMR1、TMR8).........................................................................................212

14.4.1 TMR1、TMR8简介..............................................................................................................212

14.4.2 TMR1、TMR8主要特性.....................................................................................................212

14.4.3 TMR1、TMR8功能描述.....................................................................................................212

14.4.3.1 计数时钟................................................................................................................... 212

14.4.3.2 计数模式................................................................................................................... 214

14.4.3.3 TMR输入部分..........................................................................................................216

14.4.3.4 TMR输出部分..........................................................................................................217

14.4.3.5 TMR刹车功能..........................................................................................................220

14.4.3.6 TMR同步...................................................................................................................221

14.4.3.7 调试模式................................................................................................................... 222

14.4.4 TMR1、TMR8寄存器描述................................................................................................222

14.4.4.1 TMR1、TMR8 控制寄存器1(TMRx_CTRL1)....................................... 223

14.4.4.2 TMR1 、TMR8控制寄存器2(TMRx_CTRL2)....................................... 223

14.4.4.3 TMR1、TMR8次定时器控制寄存器(TMRx_STCTRL).......................224

14.4.4.4 TMR1、TMR8 DMA/中断使能寄存器(TMRx_IDEN)..........................225

14.4.4.5 TMR1、TMR8中断状态寄存器(TMRx_ISTS)....................................... 226

14.4.4.6 TMR1、TMR8软件事件寄存器(TMRx_SWEVT)..................................227

14.4.4.7 TMR1、TMR8通道模式寄存器1(TMRx_CM1)......................................228

14.4.4.8 TMR1、TMR8通道模式寄存器2(TMRx_CM2)......................................230

14.4.4.9 TMR1、TMR8通道控制寄存器(TMRx_CCTRL)...................................230

14.4.4.10 TMR1、TMR8计数值(TMRx_CVAL)........................................................232

14.4.4.11 TMR1、TMR8预分频器(TMRx_DIV)........................................................232

14.4.4.12 TMR1、TMR8周期寄存器(TMRx_PR).................................................... 232

14.4.4.13 TMR1、TMR8重复周期寄存器(TMRx_RPR)........................................232

14.4.4.14 TMR1、TMR8通道1数据寄存器(TMRx_C1DT)................................... 232

14.4.4.15 TMR1、TMR8通道2数据寄存器(TMRx_C2DT)................................... 233

14.4.4.16 TMR1、TMR8通道3数据寄存器(TMRx_C3DT)................................... 233

14.4.4.17 TMR1、TMR8通道4数据寄存器(TMRx_C4DT)................................... 233

14.4.4.18 TMR1、TMR8刹车寄存器(TMRx_BRK)................................................. 233

14.4.4.19 TMR1、TMR8 DMA控制寄存器(TMRx_DMACTRL)..........................234

14.4.4.20 TMR1、TMR8 DMA数据寄存器(TMRx_DMADT)................................234

15 窗口看门狗(WWDT)........................................................................................................................235

15.1 WWDT简介.......................................................................................................................................235

15.2 WWDT主要特性............................................................................................................................. 235

15.3 WWDT功能描述............................................................................................................................. 235

15.4 调试模式..........................................................................................................................................236

15.5 WWDT寄存器..................................................................................................................................236

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 11 页 页 版本 版本 2.01

15.5.1 控制寄存器(WWDT_CTRL).........................................................................................236

15.5.2 配置寄存器(WWDT_CFG)...........................................................................................236

15.5.3 状态寄存器(WWDT_STS)............................................................................................237

16 看门狗(WDT).....................................................................................................................................238

16.1 WDT简介.......................................................................................................................................... 238

16.2 WDT主要特性.................................................................................................................................238

16.3 WDT功能描述.................................................................................................................................238

16.4 调试模式..........................................................................................................................................239

16.5 WDT寄存器......................................................................................................................................239

16.5.1 命令寄存器(WDT_CMD).............................................................................................239

16.5.2 预分频寄存器(WDT_DIV)...........................................................................................239

16.5.3 重装载寄存器(WDT_RLD)..........................................................................................240

16.5.4 状态寄存器(WDT_STS)................................................................................................240

17 实时时钟(RTC)..................................................................................................................................241

17.1 RTC简介............................................................................................................................................241

17.2 主要特性..........................................................................................................................................241

17.3 RTC架构............................................................................................................................................241

17.4 RTC功能描述...................................................................................................................................242

17.4.1 RTC寄存器配置...................................................................................................................242

17.4.2 RTC寄存器读取...................................................................................................................242

17.4.3 RTC中断.................................................................................................................................242

17.5 RTC寄存器描述.............................................................................................................................. 243

17.5.1 RTC控制寄存器高位(RTC_CTRLH)............................................................................243

17.5.2 RTC控制寄存器低位(RTC_CTRLL)............................................................................ 244

17.5.3 RTC分频系数寄存器(RTC_DIVH/RTC_DIVL)..........................................................244

17.5.4 RTC分频计数寄存器(RTC_DIVCNTH/RTC_DIVCNTL)...........................................245

17.5.5 RTC计数值寄存器(RTC_CNTH/RTC_CNTL).............................................................245

17.5.6 RTC闹钟寄存器(RTC_TAH/RTC_TAL).......................................................................245

18 电池供电寄存器(BPR)....................................................................................................................246

18.1 BPR简介............................................................................................................................................246

18.2 BPR特性............................................................................................................................................246

18.3 BPR功能描述...................................................................................................................................246

18.4 BPR寄存器描述..............................................................................................................................246

18.4.1 电池供电数据寄存器x(BPR_DTx)(x = 1 … 42)................................................247

18.4.2 RTC校准寄存器(BPR_RTCCAL).................................................................................. 247

18.4.3 备份控制寄存器(BPR_CTRL)..................................................................................... 248

18.4.4 备份控制/状态寄存器(BPR_CTRLSTS)....................................................................248

19 模拟/数字转换(ADC)......................................................................................................................250

19.1 ADC简介............................................................................................................................................250

19.2 ADC主要特征.................................................................................................................................. 250

19.3 ADC架构............................................................................................................................................250

19.4 ADC功能介绍.................................................................................................................................. 251

19.4.1 通道管理...............................................................................................................................251

19.4.1.1 内部温度传感器......................................................................................................252

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 12 页 页 版本 版本 2.01

19.4.1.2 内部参考电压..........................................................................................................252

19.4.2 ADC操作流程.......................................................................................................................252

19.4.2.1 上电与校准...............................................................................................................252

19.4.2.2 触发.............................................................................................................................253

19.4.2.3 采样与转换时序......................................................................................................254

19.4.3 转换顺序管理......................................................................................................................254

19.4.3.1 序列模式................................................................................................................... 254

19.4.3.2 抢占自动转换模式.................................................................................................255

19.4.3.3 反复模式................................................................................................................... 255

19.4.3.4 分割模式................................................................................................................... 255

19.4.4 数据管理...............................................................................................................................256

19.4.4.1 数据内容处理..........................................................................................................256

19.4.4.2 数据获取................................................................................................................... 256

19.4.5 电压监测...............................................................................................................................257

19.4.6 状态标志与中断.................................................................................................................257

19.5 主从模式..........................................................................................................................................257

19.5.1 数据管理...............................................................................................................................257

19.5.2 同时模式...............................................................................................................................258

19.5.3 抢占交错触发模式.............................................................................................................258

19.5.4 普通位移模式......................................................................................................................259

19.6 ADC寄存器.......................................................................................................................................260

19.6.1 ADC状态寄存器(ADC_STS).........................................................................................260

19.6.2 ADC控制寄存器1(ADC_CTRL1)..................................................................................261

19.6.3 ADC控制寄存器2(ADC_CTRL2)..................................................................................262

19.6.4 ADC采样时间寄存器1(ADC_SPT1)...........................................................................265

19.6.5 ADC采样时间寄存器2(ADC_SPT2)...........................................................................266

19.6.6 ADC抢占通道数据偏移寄存器x(ADC_PCDTOx)(x=1..4).............................. 268

19.6.7 ADC电压监测高边界寄存器(ADC_VMHB).............................................................268

19.6.8 ADC电压监测低边界寄存器(ADC_VMLB)..............................................................269

19.6.9 ADC普通序列寄存器1(ADC_OSQ1)..........................................................................269

19.6.10 ADC普通序列寄存器2(ADC_OSQ2)..........................................................................269

19.6.11 ADC普通序列寄存器3(ADC_OSQ3)..........................................................................270

19.6.12 ADC抢占序列寄存器(ADC_PSQ)...............................................................................270

19.6.13 ADC抢占数据寄存器x(ADC_PDTx)(x= 1..4).....................................................270

19.6.14 ADC普通数据寄存器(ADC_ODT)..............................................................................271

20 数字/模拟转换(DAC)......................................................................................................................272

20.1 简介...................................................................................................................................................272

20.2 主要特性..........................................................................................................................................272

20.3 设计提示..........................................................................................................................................272

20.4 功能描述..........................................................................................................................................273

20.4.1 触发事件...............................................................................................................................273

20.4.2 噪声/三角波生成............................................................................................................... 273

20.4.3 数据配置...............................................................................................................................274

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 13 页 页 版本 版本 2.01

20.5 DAC寄存器.......................................................................................................................................274

20.5.1 DAC控制寄存器(DAC_CTRL)......................................................................................275

20.5.2 DAC软件触发寄存器(DAC_SWTRG).........................................................................276

20.5.3 DAC1的12位右对齐数据保持寄存器(DAC_D1DTH12R).................................... 277

20.5.4 DAC1的12位左对齐数据保持寄存器(DAC_D1DTH12L).....................................277

20.5.5 DAC1的8位右对齐数据保持寄存器(DAC_D1DTH8R).........................................277

20.5.6 DAC2的12位右对齐数据保持寄存器(DAC_D2DTH12R).................................... 277

20.5.7 DAC2的12位左对齐数据保持寄存器(DAC_D2DTH12L).....................................277

20.5.8 DAC2的8位右对齐数据保持寄存器(DAC_D2DTH8R).........................................277

20.5.9 双DAC的12位右对齐数据保持寄存器(DAC_DDTH12R).................................... 277

20.5.10 双DAC的12位左对齐数据保持寄存器(DAC_DDTH12L).....................................277

20.5.11 双DAC的8位右对齐数据保持寄存器(DAC_DDTH8R).........................................278

20.5.12 DAC1数据输出寄存器(DAC_D1ODT).......................................................................278

20.5.13 DAC2数据输出寄存器(DAC_D2ODT).......................................................................278

21 CAN总线控制器......................................................................................................................................279

21.1 简介...................................................................................................................................................279

21.2 主要特性..........................................................................................................................................279

21.3 波特率设置......................................................................................................................................279

21.4 中断管理..........................................................................................................................................281

21.5 设计提示..........................................................................................................................................282

21.6 功能描述..........................................................................................................................................283

21.6.1 整体功能描述......................................................................................................................283

21.6.2 工作模式...............................................................................................................................283

21.6.3 测试方法...............................................................................................................................284

21.6.4 报文过滤...............................................................................................................................284

21.6.5 报文发送...............................................................................................................................286

21.6.6 报文接收...............................................................................................................................287

21.6.7 出错管理...............................................................................................................................288

21.7 CAN寄存器.......................................................................................................................................288

21.7.1 CAN控制和状态寄存器.....................................................................................................289

21.7.1.1 CAN主控制寄存器(CAN_MCTRL).............................................................289

21.7.1.2 CAN主状态寄存器 (CAN_MSTS).............................................................290

21.7.1.3 CAN发送状态寄存器 (CAN_TSTS)......................................................... 292

21.7.1.4 CAN接收FIFO 0寄存器 (CAN_RF0)....................................................... 294

21.7.1.5 CAN接收FIFO 1寄存器(CAN_RF1)..........................................................295

21.7.1.6 CAN中断使能寄存器 (CAN_INTEN)....................................................... 295

21.7.1.7 CAN错误状态寄存器 (CAN_ESTS).........................................................297

21.7.1.8 CAN位时序寄存器 (CAN_BTMG).............................................................298

21.7.2 CAN邮箱寄存器.................................................................................................................. 298

21.7.2.1 发送邮箱标识符寄存器 (CAN_TMIx) (x=0..2)..............................298

21.7.2.2 发送邮箱数据长度和时间戳寄存器 (CAN_TMCx) (x=0..2).....299

21.7.2.3 发送邮箱低字节数据寄存器 (CAN_TMDTLx) (x=0..2)..............299

21.7.2.4 发送邮箱高字节数据寄存器 (CAN_TMDTHx) (x=0..2).............299

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 14 页 页 版本 版本 2.01

21.7.2.5 接收FIFO邮箱标识符寄存器 (CAN_RFIx) (x=0..1)....................299

21.7.2.6 接收FIFO邮箱数据长度和时间戳寄存器 (CAN_RFCx) (x=0..1)300

21.7.2.7 接收FIFO邮箱低字节数据寄存器 (CAN_RFDTLx) (x=0..1)....300

21.7.2.8 接收FIFO邮箱高字节数据寄存器 (CAN_RFDTHx) (x=0..1)...300

21.7.3 CAN过滤器寄存器..............................................................................................................300

21.7.3.1 CAN过滤器控制寄存器 (CAN_FCTRL)..................................................300

21.7.3.2 CAN过滤器模式配置寄存器 (CAN_FMCFG)....................................... 300

21.7.3.3 CAN过滤器位宽配置寄存器 (CAN_FBWCFG)....................................301

21.7.3.4 CAN过滤器FIFO关联寄存器 (CAN_FRF).............................................301

21.7.3.5 CAN过滤器激活控制寄存器 (CAN_FACFG)........................................301

21.7.3.6 CAN过滤器组i的过滤位寄存器x (CAN_FiFBx) (其中i=0..13;x=1..2)

301

22 外部存储控制器(XMC)...................................................................................................................302

22.1 XMC简介...........................................................................................................................................302

22.2 XMC主要特征..................................................................................................................................302

22.3 XMC构造...........................................................................................................................................303

22.3.1 框图........................................................................................................................................303

22.3.2 地址映射...............................................................................................................................304

22.4 NOR/PSRAM界面............................................................................................................................305

22.4.1 操作方式...............................................................................................................................305

22.4.2 访问模式...............................................................................................................................306

22.4.2.1 读写相同时序的模式.............................................................................................306

22.4.2.2 读写不同时序的模式.............................................................................................309

22.4.2.3 复用模式................................................................................................................... 317

22.4.2.4 同步模式................................................................................................................... 318

22.5 NAND界面........................................................................................................................................321

22.5.1 操作方式...............................................................................................................................321

22.5.2 访问时序...............................................................................................................................321

22.5.3 ECC运算.................................................................................................................................323

22.6 XMC寄存器......................................................................................................................................323

22.6.1 NOR闪存和PSRAM控制器寄存器.................................................................................. 323

22.6.1.1 SRAM/NOR闪存片选控制寄存器1(XMC_BK1CTRL1)......................323

22.6.1.2 SRAM/NOR闪存片选控制寄存器4(XMC_BK1CTRL4)......................324

22.6.1.3 SRAM/NOR闪存片选时序寄存器1,4(XMC_BK1TMG1,4)................326

22.6.1.4 SRAM/NOR闪存写时序寄存器1,4(XMC_BK1TMGWR1,4)............. 326

22.6.1.5 SRAM/NOR额外时序寄存器1,4(XMC_EXT1,4)...................................327

22.6.2 NAND闪存控制器寄存器................................................................................................. 327

22.6.2.1 NAND闪存控制寄存器2(XMC_BK2CTRL).............................................327

22.6.2.2 中断使能和FIFO状态寄存器2(XMC_BK2IS).........................................328

22.6.2.3 常规空间时序寄存器2(XMC_BK2TMGRG)............................................329

22.6.2.4 特殊空间时序寄存器2(XMC_BK2TMGSP)............................................ 329

22.6.2.5 ECC结果寄存器2(XMC_BK2ECC)............................................................329

23 SDIO接口..................................................................................................................................................331

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 15 页 页 版本 版本 2.01

23.1 简介...................................................................................................................................................331

23.2 主要特点..........................................................................................................................................331

23.3 功能描述..........................................................................................................................................333

23.3.1 卡功能描述.......................................................................................................................... 333

23.3.1.1 卡识别模式...............................................................................................................333

23.3.1.2 数据传输模式..........................................................................................................333

23.3.1.3 擦除.............................................................................................................................334

23.3.1.4 保护管理................................................................................................................... 335

23.3.2 命令与响应.......................................................................................................................... 337

23.3.2.1 命令.............................................................................................................................337

23.3.2.2 响应格式................................................................................................................... 340

23.3.3 SDIO功能描述......................................................................................................................341

23.3.3.1 SDIO适配器.............................................................................................................342

23.3.3.2 数据BUF....................................................................................................................345

23.3.3.3 SDIO AHB接口.......................................................................................................345

23.3.3.4 硬件流控制...............................................................................................................346

23.3.4 SDIO I/O卡特定的操作..................................................................................................... 346

23.4 SDIO寄存器......................................................................................................................................347

23.4.1 SDIO电源控制寄存器(SDIO_ PWRCTRL).................................................................347

23.4.2 SDIO时钟控制寄存器(SDIO_CLKCTRL)....................................................................348

23.4.3 SDIO参数寄存器(SDIO_ARG).....................................................................................348

23.4.4 SDIO命令寄存器(SDIO_CMD)....................................................................................349

23.4.5 SDIO命令响应寄存器(SDIO_RSPCMD)....................................................................349

23.4.6 SDIO响应1..4寄存器(SDIO_RSPx).............................................................................349

23.4.7 SDIO数据定时器寄存器(SDIO_DTTMR)..................................................................350

23.4.8 SDIO数据长度寄存器(SDIO_DTLEN)....................................................................... 350

23.4.9 SDIO数据控制寄存器(SDIO_DTCTRL)..................................................................... 350

23.4.10 SDIO数据计数器寄存器(SDIO_DTCNTR)................................................................351

23.4.11 SDIO状态寄存器(SDIO_STS)......................................................................................351

23.4.12 SDIO清除中断寄存器(SDIO_INTCLR)......................................................................352

23.4.13 SDIO中断屏蔽寄存器(SDIO_INTEN)........................................................................353

23.4.14 SDIOBUF计数器寄存器(SDIO_BUFCNTR)...............................................................355

23.4.15 SDIO数据BUF寄存器(SDIO_BUF)..............................................................................355

24 通用串行总线全速设备接口(USBFS).........................................................................................356

24.1 简介...................................................................................................................................................356

24.2 USBFS时钟与管脚配置.................................................................................................................356

24.2.1 USB时钟配置....................................................................................................................... 356

24.2.2 USB管脚配置....................................................................................................................... 356

24.3 USBFS功能描述.............................................................................................................................. 356

24.3.1 USB初始化配置...................................................................................................................356

24.3.2 端点配置...............................................................................................................................356

24.3.3 USB缓冲区............................................................................................................................357

24.3.4 双缓冲端点配置.................................................................................................................358

AT32F403A/407/407A系列 系列 技术手册

2021.10.22 第 第 16 页 页 版本 版本 2.01

24.3.5 SOF输出.................................................................................................................................358

24.3.6 挂起/恢复.............................................................................................................................359

24.4 USB中断............................................................................................................................................359

24.5 USBFS寄存器...................................................................................................................................359

24.5.1 USBFS端点n寄存器(USBFS_EPTn), n=[0..7]...........................................................359

24.5.2 USBFS控制寄存器(USBFS_CTRL).............................................................................. 360

24.5.3 USBFS中断状态寄存器(USBFS_INTSTS)................................................................. 361

24.5.4 USBFS SOF帧编号寄存器(USBFS_SOFRNUM)....................................................... 362

24.5.5 USBFS设备地址寄存器(USBFS_DEVADDR)............................................................362

24.5.6 USBFS分组缓冲区描述表地址寄存器(USBFS_BUFTBL).....................................362

24.5.7 USBFS CFG控制寄存器(USBFS_CFG)........................................................................362

24.5.8 USBFS发送缓冲区首地址寄存器 n(USBFS_TnADDR)........................................363

24.5.9 USBFS发送数据长度寄存器 n(USBFS_TnLEN).....................................................363

24.5.10 USBFS接收缓冲区首地址寄存器 n(USBFS_RnADDR)........................................363

24.5.11 USBFS接收数据字节数寄存器 n(USBFS_RnLEN)................................................363

25 HICK自动时钟校准(ACC)............................................................................................................... 364

25.1 简介...................................................................................................................................................364

25.2 主要特性..........................................................................................................................................364

25.3 中断请求..........................................................................................................................................364

25.4 功能概述..........................................................................................................................................364

25.5 原理分析..........................................................................................................................................365

25.6 寄存器描述......................................................................................................................................366

25.6.1 状态寄存器(ACC_STS).................................................................................................367

25.6.2 控制寄存器1(ACC_CTRL1)..........................................................................................367

25.6.3 控制寄存器2(ACC_CTRL2)..........................................................................................367