实例介绍

【实例截图】

【核心代码】

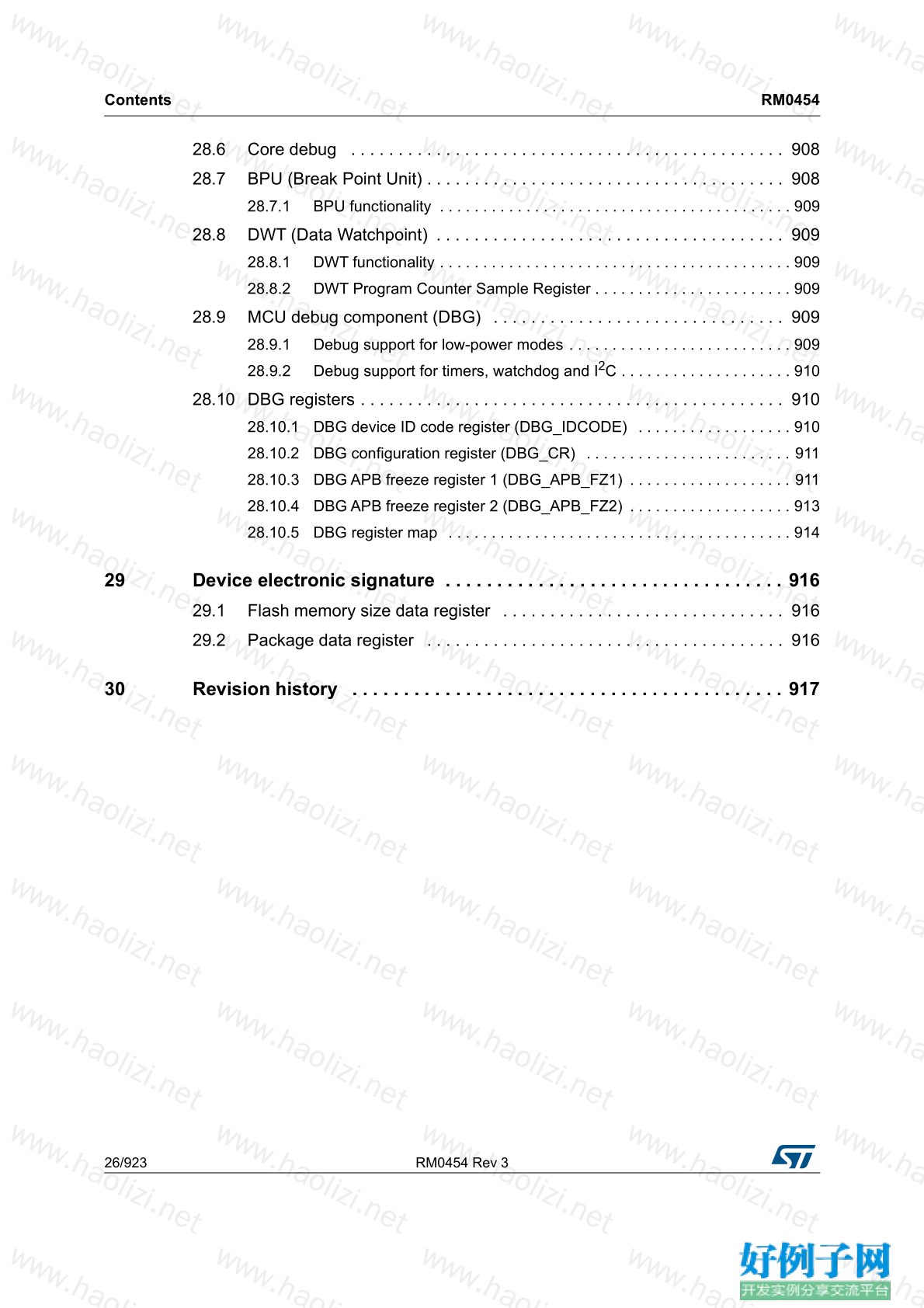

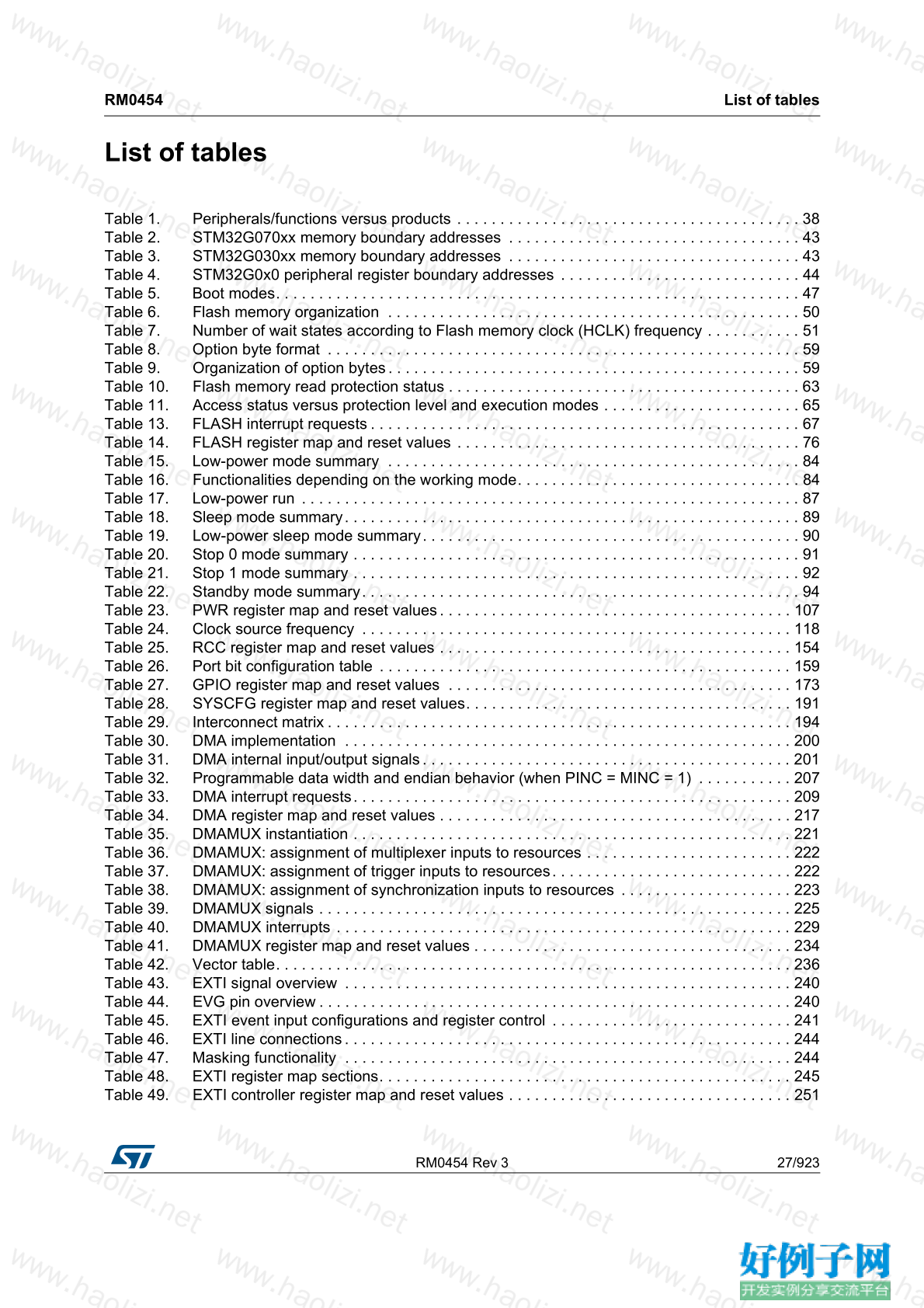

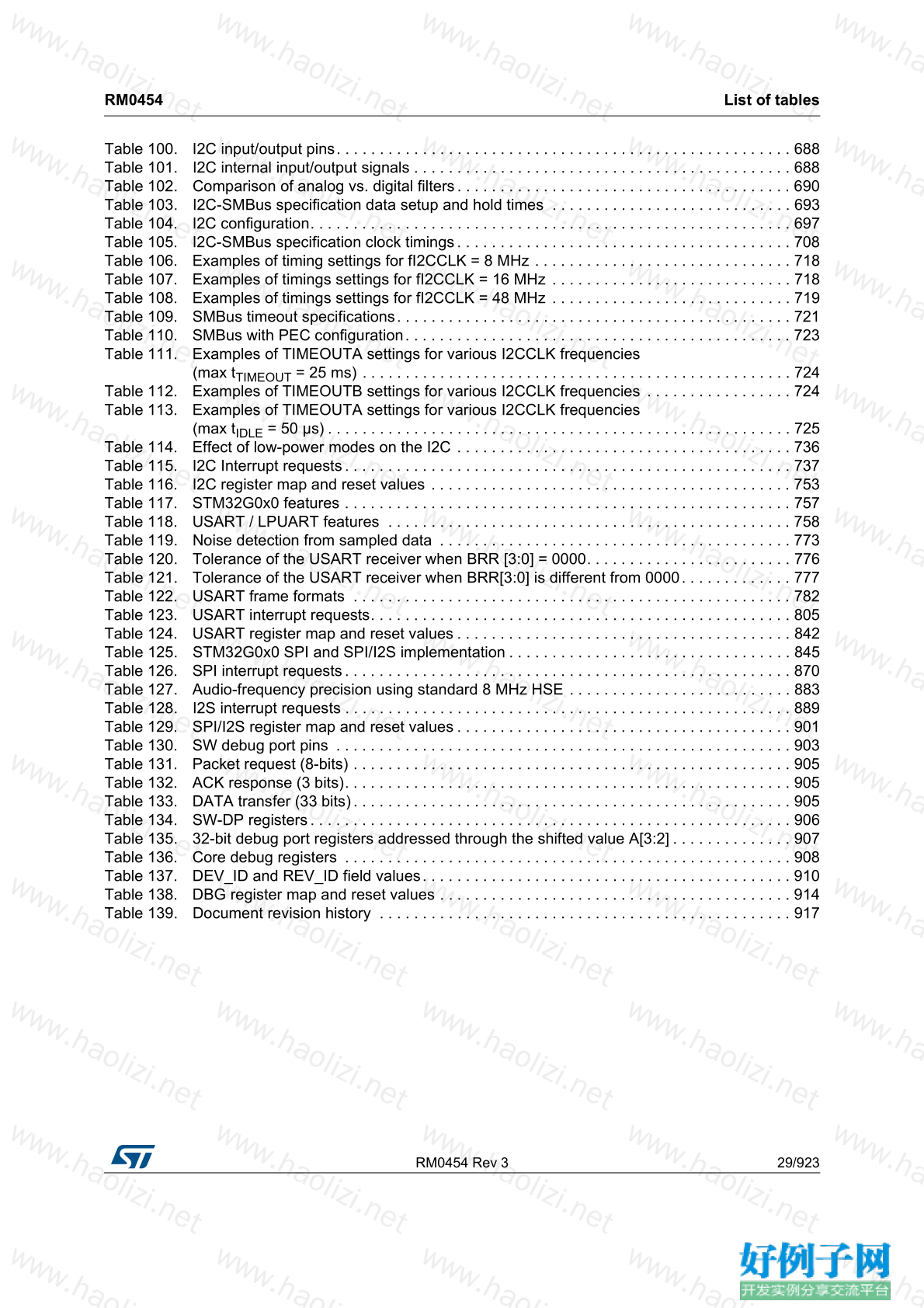

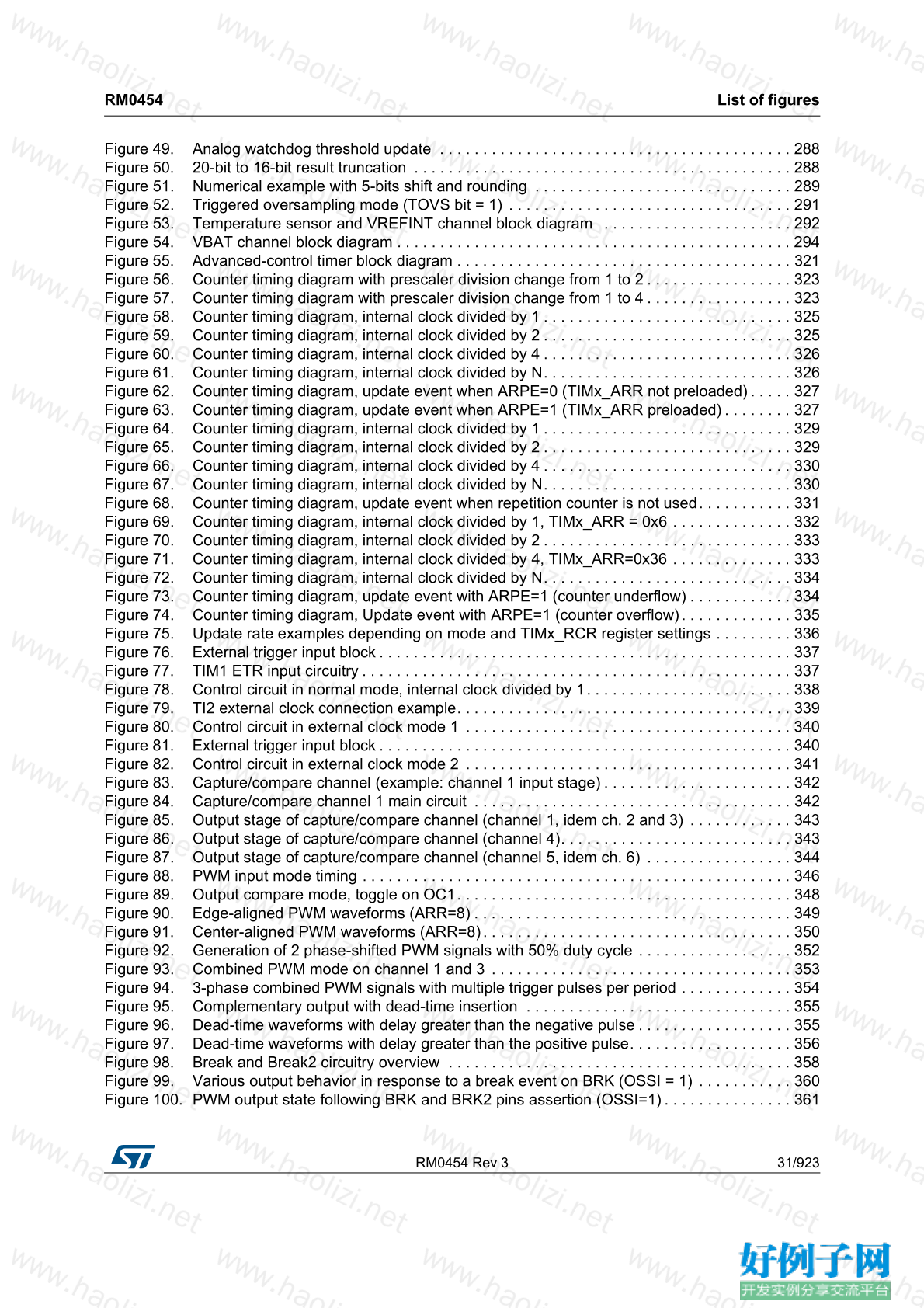

Contents

1 Documentation conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.1 General information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.2 List of abbreviations for registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

1.3 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

1.4 Availability of peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2 Memory and bus architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.1 System architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2.2 Memory organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.2.2 Memory map and register boundary addresses . . . . . . . . . . . . . . . . . . 42

2.3 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.4 Flash memory overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.5 Boot configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3 Embedded Flash memory (FLASH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.1 FLASH Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.2 FLASH main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.3 FLASH functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.3.1 FLASH memory organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

3.3.2 FLASH empty check . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.3.3 FLASH error code correction (ECC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.3.4 FLASH read access latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.3.5 FLASH memory acceleration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.3.6 FLASH program and erase operations . . . . . . . . . . . . . . . . . . . . . . . . . 53

3.3.7 FLASH Main memory erase sequences . . . . . . . . . . . . . . . . . . . . . . . . 54

3.3.8 FLASH Main memory programming sequences . . . . . . . . . . . . . . . . . . 54

3.4 FLASH option bytes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.4.1 FLASH option byte description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.4.2 FLASH option byte programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

3.5 FLASH memory protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.5.1 FLASH read protection (RDP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.5.2 FLASH write protection (WRP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

RM0454 Rev 3 3/923

RM0454 Contents

26

3.6 FLASH interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

3.7 FLASH registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.7.1 FLASH access control register (FLASH_ACR) . . . . . . . . . . . . . . . . . . . 68

3.7.2 FLASH key register (FLASH_KEYR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.7.3 FLASH option key register (FLASH_OPTKEYR) . . . . . . . . . . . . . . . . . . 69

3.7.4 FLASH status register (FLASH_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.7.5 FLASH control register (FLASH_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . 71

3.7.6 FLASH ECC register (FLASH_ECCR) . . . . . . . . . . . . . . . . . . . . . . . . . 73

3.7.7 FLASH option register (FLASH_OPTR) . . . . . . . . . . . . . . . . . . . . . . . . 73

3.7.8 FLASH WRP area A address register (FLASH_WRP1AR) . . . . . . . . . . 75

3.7.9 FLASH WRP area B address register (FLASH_WRP1BR) . . . . . . . . . . 75

3.7.10 FLASH register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

4 Power control (PWR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.1 Power supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.1.1 ADC reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.1.2 Battery backup of RTC domain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.1.3 Voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.1.4 Dynamic voltage scaling management . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.2 Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

4.2.1 Power-on reset (POR) / power-down reset (PDR) . . . . . . . . . . . . . . . . . 81

4.3 Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

4.3.1 Run mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

4.3.2 Low-power run mode (LP run) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

4.3.3 Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

4.3.4 Sleep mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

4.3.5 Low-power sleep mode (LP sleep) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

4.3.6 Stop 0 mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

4.3.7 Stop 1 mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

4.3.8 Standby mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

4.3.9 Auto-wakeup from low-power mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

4.4 PWR registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

4.4.1 Power control register 1 (PWR_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . 95

4.4.2 Power control register 3 (PWR_CR3) . . . . . . . . . . . . . . . . . . . . . . . . . . 96

4.4.3 Power control register 4 (PWR_CR4) . . . . . . . . . . . . . . . . . . . . . . . . . . 97

4.4.4 Power status register 1 (PWR_SR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Contents RM0454

4/923 RM0454 Rev 3

4.4.5 Power status register 2 (PWR_SR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

4.4.6 Power status clear register (PWR_SCR) . . . . . . . . . . . . . . . . . . . . . . . 100

4.4.7 Power Port A pull-up control register (PWR_PUCRA) . . . . . . . . . . . . . 101

4.4.8 Power Port A pull-down control register (PWR_PDCRA) . . . . . . . . . . 101

4.4.9 Power Port B pull-up control register (PWR_PUCRB) . . . . . . . . . . . . . 102

4.4.10 Power Port B pull-down control register (PWR_PDCRB) . . . . . . . . . . 102

4.4.11 Power Port C pull-up control register (PWR_PUCRC) . . . . . . . . . . . . 103

4.4.12 Power Port C pull-down control register (PWR_PDCRC) . . . . . . . . . . 103

4.4.13 Power Port D pull-up control register (PWR_PUCRD) . . . . . . . . . . . . 104

4.4.14 Power Port D pull-down control register (PWR_PDCRD) . . . . . . . . . . 104

4.4.15 Power Port F pull-up control register (PWR_PUCRF) . . . . . . . . . . . . . 105

4.4.16 Power Port F pull-down control register (PWR_PDCRF) . . . . . . . . . . 105

4.4.17 PWR register map and reset value table . . . . . . . . . . . . . . . . . . . . . . . 107

5 Reset and clock control (RCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

5.1 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

5.1.1 Power reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

5.1.2 System reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

5.1.3 RTC domain reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

5.2 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

5.2.1 HSE clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

5.2.2 HSI16 clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

5.2.3 PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

5.2.4 LSE clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

5.2.5 LSI clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

5.2.6 System clock (SYSCLK) selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

5.2.7 Clock source frequency versus voltage scaling . . . . . . . . . . . . . . . . . . 118

5.2.8 Clock security system (CSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

5.2.9 Clock security system for LSE clock (LSECSS) . . . . . . . . . . . . . . . . . 119

5.2.10 ADC clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

5.2.11 RTC clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

5.2.12 Timer clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

5.2.13 Watchdog clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

5.2.14 Clock-out capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

5.2.15 Internal/external clock measurement with TIM14/TIM16/TIM17 . . . . . 121

5.2.16 Peripheral clock enable registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

5.3 Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

RM0454 Rev 3 5/923

RM0454 Contents

26

5.4 RCC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.4.1 Clock control register (RCC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.4.2 Internal clock sources calibration register (RCC_ICSCR) . . . . . . . . . . 126

5.4.3 Clock configuration register (RCC_CFGR) . . . . . . . . . . . . . . . . . . . . . 127

5.4.4 PLL configuration register (RCC_PLLCFGR) . . . . . . . . . . . . . . . . . . . 129

5.4.5 Clock interrupt enable register (RCC_CIER) . . . . . . . . . . . . . . . . . . . . 131

5.4.6 Clock interrupt flag register (RCC_CIFR) . . . . . . . . . . . . . . . . . . . . . . 132

5.4.7 Clock interrupt clear register (RCC_CICR) . . . . . . . . . . . . . . . . . . . . . 133

5.4.8 I/O port reset register (RCC_IOPRSTR) . . . . . . . . . . . . . . . . . . . . . . . 134

5.4.9 AHB peripheral reset register (RCC_AHBRSTR) . . . . . . . . . . . . . . . . 135

5.4.10 APB peripheral reset register 1 (RCC_APBRSTR1) . . . . . . . . . . . . . . 136

5.4.11 APB peripheral reset register 2 (RCC_APBRSTR2) . . . . . . . . . . . . . . 138

5.4.12 I/O port clock enable register (RCC_IOPENR) . . . . . . . . . . . . . . . . . . 139

5.4.13 AHB peripheral clock enable register (RCC_AHBENR) . . . . . . . . . . . 140

5.4.14 APB peripheral clock enable register 1 (RCC_APBENR1) . . . . . . . . . 141

5.4.15 APB peripheral clock enable register 2(RCC_APBENR2) . . . . . . . . . . 143

5.4.16 I/O port in Sleep mode clock enable register (RCC_IOPSMENR) . . . 144

5.4.17 AHB peripheral clock enable in Sleep/Stop mode register

(RCC_AHBSMENR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

5.4.18 APB peripheral clock enable in Sleep/Stop mode register 1

(RCC_APBSMENR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

5.4.19 APB peripheral clock enable in Sleep/Stop mode register 2

(RCC_APBSMENR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

5.4.20 Peripherals independent clock configuration register (RCC_CCIPR) . 149

5.4.21 RTC domain control register (RCC_BDCR) . . . . . . . . . . . . . . . . . . . . . 151

5.4.22 Control/status register (RCC_CSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

5.4.23 RCC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

6 General-purpose I/Os (GPIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

6.2 GPIO main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

6.3 GPIO functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

6.3.1 General-purpose I/O (GPIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

6.3.2 I/O pin alternate function multiplexer and mapping . . . . . . . . . . . . . . . 160

6.3.3 I/O port control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

6.3.4 I/O port data registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

6.3.5 I/O data bitwise handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

6.3.6 GPIO locking mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Contents RM0454

6/923 RM0454 Rev 3

6.3.7 I/O alternate function input/output . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

6.3.8 External interrupt/wakeup lines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

6.3.9 Input configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

6.3.10 Output configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

6.3.11 Alternate function configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

6.3.12 Analog configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

6.3.13 Using the HSE or LSE oscillator pins as GPIOs . . . . . . . . . . . . . . . . . 166

6.3.14 Using the GPIO pins in the RTC domain . . . . . . . . . . . . . . . . . . . . . . . 166

6.4 GPIO registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

6.4.1 GPIO port mode register (GPIOx_MODER)

(x =A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

6.4.2 GPIO port output type register (GPIOx_OTYPER)

(x = A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

6.4.3 GPIO port output speed register (GPIOx_OSPEEDR)

(x = A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

6.4.4 GPIO port pull-up/pull-down register (GPIOx_PUPDR)

(x = A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

6.4.5 GPIO port input data register (GPIOx_IDR)

(x = A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

6.4.6 GPIO port output data register (GPIOx_ODR)

(x = A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

6.4.7 GPIO port bit set/reset register (GPIOx_BSRR)

(x = A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

6.4.8 GPIO port configuration lock register (GPIOx_LCKR)

(x = A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

6.4.9 GPIO alternate function low register (GPIOx_AFRL)

(x = A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

6.4.10 GPIO alternate function high register (GPIOx_AFRH)

(x = A to D, F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

6.4.11 GPIO port bit reset register (GPIOx_BRR) (x = A to D, F) . . . . . . . . . . 172

6.4.12 GPIO register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7 System configuration controller (SYSCFG) . . . . . . . . . . . . . . . . . . . . 175

7.1 SYSCFG registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

7.1.1 SYSCFG configuration register 1 (SYSCFG_CFGR1) . . . . . . . . . . . . 175

7.1.2 SYSCFG configuration register 2 (SYSCFG_CFGR2) . . . . . . . . . . . . 178

7.1.3 SYSCFG interrupt line 0 status register (SYSCFG_ITLINE0) . . . . . . . 180

7.1.4 SYSCFG interrupt line 2 status register (SYSCFG_ITLINE2) . . . . . . . 180

7.1.5 SYSCFG interrupt line 3 status register (SYSCFG_ITLINE3) . . . . . . . 181

7.1.6 SYSCFG interrupt line 4 status register (SYSCFG_ITLINE4) . . . . . . . 181

RM0454 Rev 3 7/923

RM0454 Contents

26

7.1.7 SYSCFG interrupt line 5 status register (SYSCFG_ITLINE5) . . . . . . . 182

7.1.8 SYSCFG interrupt line 6 status register (SYSCFG_ITLINE6) . . . . . . . 182

7.1.9 SYSCFG interrupt line 7 status register (SYSCFG_ITLINE7) . . . . . . . 182

7.1.10 SYSCFG interrupt line 9 status register (SYSCFG_ITLINE9) . . . . . . . 183

7.1.11 SYSCFG interrupt line 10 status register (SYSCFG_ITLINE10) . . . . . 183

7.1.12 SYSCFG interrupt line 11 status register (SYSCFG_ITLINE11) . . . . . 184

7.1.13 SYSCFG interrupt line 12 status register (SYSCFG_ITLINE12) . . . . . 185

7.1.14 SYSCFG interrupt line 13 status register (SYSCFG_ITLINE13) . . . . . 185

7.1.15 SYSCFG interrupt line 14 status register (SYSCFG_ITLINE14) . . . . . 186

7.1.16 SYSCFG interrupt line 16 status register (SYSCFG_ITLINE16) . . . . . 186

7.1.17 SYSCFG interrupt line 17 status register (SYSCFG_ITLINE17) . . . . . 187

7.1.18 SYSCFG interrupt line 18 status register (SYSCFG_ITLINE18) . . . . . 187

7.1.19 SYSCFG interrupt line 19 status register (SYSCFG_ITLINE19) . . . . . 187

7.1.20 SYSCFG interrupt line 20 status register (SYSCFG_ITLINE20) . . . . . 188

7.1.21 SYSCFG interrupt line 21 status register (SYSCFG_ITLINE21) . . . . . 188

7.1.22 SYSCFG interrupt line 22 status register (SYSCFG_ITLINE22) . . . . . 188

7.1.23 SYSCFG interrupt line 23 status register (SYSCFG_ITLINE23) . . . . . 189

7.1.24 SYSCFG interrupt line 24 status register (SYSCFG_ITLINE24) . . . . . 189

7.1.25 SYSCFG interrupt line 25 status register (SYSCFG_ITLINE25) . . . . . 189

7.1.26 SYSCFG interrupt line 26 status register (SYSCFG_ITLINE26) . . . . . 190

7.1.27 SYSCFG interrupt line 27 status register (SYSCFG_ITLINE27) . . . . . 190

7.1.28 SYSCFG interrupt line 28 status register (SYSCFG_ITLINE28) . . . . . 190

7.1.29 SYSCFG interrupt line 29 status register (SYSCFG_ITLINE29) . . . . . 191

7.1.30 SYSCFG register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

8 Interconnect matrix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

8.2 Connection summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

8.3 Interconnection details . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

8.3.1 From TIM1, TIM3, TIM15, TIM16, and TIM17,

to TIM1, TIM3, and TIM15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

8.3.2 From TIM1, TIM3, TIM6, TIM15, and EXTI, to ADC . . . . . . . . . . . . . . . 196

8.3.3 From ADC to TIM1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

8.3.4 From HSE, LSE, LSI, MCO, RTC and TAMP, to TIM14,

TIM16, and TIM17 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

8.3.5 From internal analog sources to ADC . . . . . . . . . . . . . . . . . . . . . . . . . 197

8.3.6 From system errors to TIM1, TIM3, TIM15, TIM16, and TIM17 . . . . . . 197

Contents RM0454

8/923 RM0454 Rev 3

8.3.7 From TIM16, TIM17, USART1, and USART4, to IRTIM . . . . . . . . . . . 197

8.3.8 From TIM14 to DMAMUX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

9 Direct memory access controller (DMA) . . . . . . . . . . . . . . . . . . . . . . . 199

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

9.2 DMA main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

9.3 DMA implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

9.3.1 DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

9.3.2 DMA request mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

9.4 DMA functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

9.4.1 DMA block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

9.4.2 DMA pins and internal signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

9.4.3 DMA transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

9.4.4 DMA arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

9.4.5 DMA channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

9.4.6 DMA data width, alignment and endianness . . . . . . . . . . . . . . . . . . . . 207

9.4.7 DMA error management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

9.5 DMA interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

9.6 DMA registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

9.6.1 DMA interrupt status register (DMA_ISR) . . . . . . . . . . . . . . . . . . . . . . 209

9.6.2 DMA interrupt flag clear register (DMA_IFCR) . . . . . . . . . . . . . . . . . . 212

9.6.3 DMA channel x configuration register (DMA_CCRx) . . . . . . . . . . . . . . 213

9.6.4 DMA channel x number of data to transfer register (DMA_CNDTRx) . 216

9.6.5 DMA channel x peripheral address register (DMA_CPARx) . . . . . . . . 216

9.6.6 DMA channel x memory address register (DMA_CMARx) . . . . . . . . . 217

9.6.7 DMA register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

10 DMA request multiplexer (DMAMUX) . . . . . . . . . . . . . . . . . . . . . . . . . 220

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

10.2 DMAMUX main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

10.3 DMAMUX implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

10.3.1 DMAMUX instantiation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

10.3.2 DMAMUX mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

10.4 DMAMUX functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

10.4.1 DMAMUX block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

10.4.2 DMAMUX signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

RM0454 Rev 3 9/923

RM0454 Contents

26

10.4.3 DMAMUX channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

10.4.4 DMAMUX request line multiplexer . . . . . . . . . . . . . . . . . . . . . . . . . . . . 225

10.4.5 DMAMUX request generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

10.5 DMAMUX interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

10.6 DMAMUX registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

10.6.1 DMAMUX request line multiplexer channel x configuration register

(DMAMUX_CxCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

10.6.2 DMAMUX request line multiplexer interrupt channel status register

(DMAMUX_CSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

10.6.3 DMAMUX request line multiplexer interrupt clear flag register

(DMAMUX_CFR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

10.6.4 DMAMUX request generator channel x configuration register

(DMAMUX_RGxCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

10.6.5 DMAMUX request generator interrupt status register

(DMAMUX_RGSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

10.6.6 DMAMUX request generator interrupt clear flag register

(DMAMUX_RGCFR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

10.6.7 DMAMUX register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

11 Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . 236

11.1 Main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

11.2 SysTick calibration value register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

11.3 Interrupt and exception vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

12 Extended interrupt and event controller (EXTI) . . . . . . . . . . . . . . . . . 239

12.1 EXTI main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

12.2 EXTI block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

12.2.1 EXTI connections between peripherals and CPU . . . . . . . . . . . . . . . . 241

12.3 EXTI functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

12.3.1 EXTI configurable event input wakeup . . . . . . . . . . . . . . . . . . . . . . . . 242

12.3.2 EXTI direct event input wakeup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

12.3.3 EXTI mux . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

12.4 EXTI functional behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

12.5 EXTI registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

12.5.1 EXTI rising trigger selection register (EXTI_RTSR1) . . . . . . . . . . . . . . 245

12.5.2 EXTI falling trigger selection register (EXTI_FTSR1) . . . . . . . . . . . . . 246

12.5.3 EXTI software interrupt event register (EXTI_SWIER1) . . . . . . . . . . . 246

12.5.4 EXTI rising edge pending register (EXTI_RPR1) . . . . . . . . . . . . . . . . 247

Contents RM0454

10/923 RM0454 Rev 3

12.5.5 EXTI falling edge pending register (EXTI_FPR1) . . . . . . . . . . . . . . . . 247

12.5.6 EXTI external interrupt selection register (EXTI_EXTICRx) . . . . . . . . 248

12.5.7 EXTI CPU wakeup with interrupt mask register (EXTI_IMR1) . . . . . . . 249

12.5.8 EXTI CPU wakeup with event mask register (EXTI_EMR1) . . . . . . . . 250

12.5.9 EXTI register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

13 Cyclic redundancy check calculation unit (CRC) . . . . . . . . . . . . . . . . 253

13.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

13.2 CRC main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

13.3 CRC functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

13.3.1 CRC block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

13.3.2 CRC internal signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

13.3.3 CRC operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

13.4 CRC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

13.4.1 CRC data register (CRC_DR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

13.4.2 CRC independent data register (CRC_IDR) . . . . . . . . . . . . . . . . . . . . 256

13.4.3 CRC control register (CRC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

13.4.4 CRC initial value (CRC_INIT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

13.4.5 CRC polynomial (CRC_POL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

13.4.6 CRC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

14 Analog-to-digital converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

14.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

14.2 ADC main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

14.3 ADC functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

14.3.1 ADC pins and internal signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

14.3.2 ADC voltage regulator (ADVREGEN) . . . . . . . . . . . . . . . . . . . . . . . . . 262

14.3.3 Calibration (ADCAL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

14.3.4 ADC on-off control (ADEN, ADDIS, ADRDY) . . . . . . . . . . . . . . . . . . . . 264

14.3.5 ADC clock (CKMODE, PRESC[3:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . 266

14.3.6 ADC connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

14.3.7 Configuring the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

14.3.8 Channel selection (CHSEL, SCANDIR, CHSELRMOD) . . . . . . . . . . . 269

14.3.9 Programmable sampling time (SMPx[2:0]) . . . . . . . . . . . . . . . . . . . . . 270

14.3.10 Single conversion mode (CONT=0) . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

14.3.11 Continuous conversion mode (CONT=1) . . . . . . . . . . . . . . . . . . . . . . . 271

RM0454 Rev 3 11/923

RM0454 Contents

26

14.3.12 Starting conversions (ADSTART) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

14.3.13 Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

14.3.14 Stopping an ongoing conversion (ADSTP) . . . . . . . . . . . . . . . . . . . . . 273

14.4 Conversion on external trigger and trigger polarity (EXTSEL, EXTEN) . 274

14.4.1 Discontinuous mode (DISCEN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

14.4.2 Programmable resolution (RES) - fast conversion mode . . . . . . . . . . 275

14.4.3 End of conversion, end of sampling phase (EOC, EOSMP flags) . . . . 276

14.4.4 End of conversion sequence (EOS flag) . . . . . . . . . . . . . . . . . . . . . . . 276

14.4.5 Example timing diagrams (single/continuous modes . . . . . . . . . . . . . . . . .

hardware/software triggers) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

14.4.6 Low frequency trigger mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

14.5 Data management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

14.5.1 Data register and data alignment (ADC_DR, ALIGN) . . . . . . . . . . . . . 279

14.5.2 ADC overrun (OVR, OVRMOD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

14.5.3 Managing a sequence of data converted without using the DMA . . . . 280

14.5.4 Managing converted data without using the DMA without overrun . . . 280

14.5.5 Managing converted data using the DMA . . . . . . . . . . . . . . . . . . . . . . 280

14.6 Low-power features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

14.6.1 Wait mode conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

14.6.2 Auto-off mode (AUTOFF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

14.7 Analog window watchdog (AWD1EN, AWD1SGL, AWD1CH,

ADC_AWDxCR, ADC_AWDxTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

14.7.1 Description of analog watchdog 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

14.7.2 Description of analog watchdog 2 and 3 . . . . . . . . . . . . . . . . . . . . . . . 285

14.7.3 ADC_AWDx_OUT signal output generation . . . . . . . . . . . . . . . . . . . . 286

14.7.4 Analog Watchdog threshold control . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

14.8 Oversampler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

14.8.1 ADC operating modes supported when oversampling . . . . . . . . . . . . 290

14.8.2 Analog watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

14.8.3 Triggered mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

14.9 Temperature sensor and internal reference voltage . . . . . . . . . . . . . . . . 291

14.10 Battery voltage monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

14.11 ADC interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

14.12 ADC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

14.12.1 ADC interrupt and status register (ADC_ISR) . . . . . . . . . . . . . . . . . . . 296

14.12.2 ADC interrupt enable register (ADC_IER) . . . . . . . . . . . . . . . . . . . . . . 298

Contents RM0454

12/923 RM0454 Rev 3

14.12.3 ADC control register (ADC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

14.12.4 ADC configuration register 1 (ADC_CFGR1) . . . . . . . . . . . . . . . . . . . 302

14.12.5 ADC configuration register 2 (ADC_CFGR2) . . . . . . . . . . . . . . . . . . . 306

14.12.6 ADC sampling time register (ADC_SMPR) . . . . . . . . . . . . . . . . . . . . . 307

14.12.7 ADC watchdog threshold register (ADC_AWD1TR) . . . . . . . . . . . . . . 308

14.12.8 ADC watchdog threshold register (ADC_AWD2TR) . . . . . . . . . . . . . . 309

14.12.9 ADC channel selection register [alternate] (ADC_CHSELR) . . . . . . . . 310

14.12.10 ADC channel selection register [alternate] (ADC_CHSELR) . . . . . . . . 311

14.12.11 ADC watchdog threshold register (ADC_AWD3TR) . . . . . . . . . . . . . . 313

14.12.12 ADC data register (ADC_DR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

14.12.13 ADC Analog Watchdog 2 Configuration register (ADC_AWD2CR) . . . 314

14.12.14 ADC Analog Watchdog 3 Configuration register (ADC_AWD3CR) . . . 314

14.12.15 ADC Calibration factor (ADC_CALFACT) . . . . . . . . . . . . . . . . . . . . . . 315

14.12.16 ADC common configuration register (ADC_CCR) . . . . . . . . . . . . . . . . 315

14.13 ADC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

15 Advanced-control timer (TIM1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

15.1 TIM1 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

15.2 TIM1 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 320

15.3 TIM1 functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

15.3.1 Time-base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

15.3.2 Counter modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

15.3.3 Repetition counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

15.3.4 External trigger input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 337

15.3.5 Clock selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 338

15.3.6 Capture/compare channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 342

15.3.7 Input capture mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 344

15.3.8 PWM input mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 345

15.3.9 Forced output mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346

15.3.10 Output compare mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347

15.3.11 PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 348

15.3.12 Asymmetric PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

15.3.13 Combined PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 352

15.3.14 Combined 3-phase PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 353

15.3.15 Complementary outputs and dead-time insertion . . . . . . . . . . . . . . . . 354

15.3.16 Using the break function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356

15.3.17 Bidirectional break inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

RM0454 Rev 3 13/923

RM0454 Contents

26

15.3.18 Clearing the OCxREF signal on an external event . . . . . . . . . . . . . . . 364

15.3.19 6-step PWM generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 365

15.3.20 One-pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

15.3.21 Retriggerable one pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

15.3.22 Encoder interface mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 368

15.3.23 UIF bit remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

15.3.24 Timer input XOR function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

15.3.25 Interfacing with Hall sensors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

15.3.26 Timer synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 374

15.3.27 ADC synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 378

15.3.28 DMA burst mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 378

15.3.29 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

15.4 TIM1 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

15.4.1 TIM1 control register 1 (TIM1_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . 380

15.4.2 TIM1 control register 2 (TIM1_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . 381

15.4.3 TIM1 slave mode control register (TIM1_SMCR) . . . . . . . . . . . . . . . . 384

15.4.4 TIM1 DMA/interrupt enable register (TIM1_DIER) . . . . . . . . . . . . . . . 386

15.4.5 TIM1 status register (TIM1_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 388

15.4.6 TIM1 event generation register (TIM1_EGR) . . . . . . . . . . . . . . . . . . . 390

15.4.7 TIM1 capture/compare mode register 1 [alternate]

(TIM1_CCMR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 391

15.4.8 TIM1 capture/compare mode register 1 [alternate]

(TIM1_CCMR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

15.4.9 TIM1 capture/compare mode register 2 [alternate]

(TIM1_CCMR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

15.4.10 TIM1 capture/compare mode register 2 [alternate]

(TIM1_CCMR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 396

15.4.11 TIM1 capture/compare enable register

(TIM1_CCER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 398

15.4.12 TIM1 counter (TIM1_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 401

15.4.13 TIM1 prescaler (TIM1_PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 401

15.4.14 TIM1 auto-reload register (TIM1_ARR) . . . . . . . . . . . . . . . . . . . . . . . . 401

15.4.15 TIM1 repetition counter register (TIM1_RCR) . . . . . . . . . . . . . . . . . . . 402

15.4.16 TIM1 capture/compare register 1 (TIM1_CCR1) . . . . . . . . . . . . . . . . . 402

15.4.17 TIM1 capture/compare register 2 (TIM1_CCR2) . . . . . . . . . . . . . . . . . 403

15.4.18 TIM1 capture/compare register 3 (TIM1_CCR3) . . . . . . . . . . . . . . . . . 403

15.4.19 TIM1 capture/compare register 4 (TIM1_CCR4) . . . . . . . . . . . . . . . . . 404

15.4.20 TIM1 break and dead-time register

(TIM1_BDTR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 404

Contents RM0454

14/923 RM0454 Rev 3

15.4.21 TIM1 DMA control register (TIM1_DCR) . . . . . . . . . . . . . . . . . . . . . . . 408

15.4.22 TIM1 DMA address for full transfer

(TIM1_DMAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 409

15.4.23 TIM1 capture/compare mode register 3

(TIM1_CCMR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 410

15.4.24 TIM1 capture/compare register 5 (TIM1_CCR5) . . . . . . . . . . . . . . . . . 411

15.4.25 TIM1 capture/compare register 6 (TIM1_CCR6) . . . . . . . . . . . . . . . . . 412

15.4.26 TIM1 alternate function option register 1 (TIM1_AF1) . . . . . . . . . . . . . 412

15.4.27 TIM1 Alternate function register 2 (TIM1_AF2) . . . . . . . . . . . . . . . . . . 413

15.4.28 TIM1 timer input selection register (TIM1_TISEL) . . . . . . . . . . . . . . . . 414

15.4.29 TIM1 register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

16 General-purpose timer (TIM3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 418

16.1 TIM3 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 418

16.2 TIM3 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 418

16.3 TIM3 functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 420

16.3.1 Time-base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 420

16.3.2 Counter modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

16.3.3 Clock selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 432

16.3.4 Capture/Compare channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 436

16.3.5 Input capture mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 438

16.3.6 PWM input mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439

16.3.7 Forced output mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 440

16.3.8 Output compare mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 440

16.3.9 PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 441

16.3.10 Asymmetric PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

16.3.11 Combined PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

16.3.12 Clearing the OCxREF signal on an external event . . . . . . . . . . . . . . . 446

16.3.13 One-pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 448

16.3.14 Retriggerable one pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449

16.3.15 Encoder interface mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 450

16.3.16 UIF bit remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 452

16.3.17 Timer input XOR function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 452

16.3.18 Timers and external trigger synchronization . . . . . . . . . . . . . . . . . . . . 452

16.3.19 Timer synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 456

16.3.20 DMA burst mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 461

16.3.21 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 462

RM0454 Rev 3 15/923

RM0454 Contents

26

16.4 TIM3 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 463

16.4.1 TIM3 control register 1 (TIM3_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . 463

16.4.2 TIM3 control register 2 (TIM3_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . 464

16.4.3 TIM3 slave mode control register (TIM3_SMCR) . . . . . . . . . . . . . . . . 466

16.4.4 TIM3 DMA/Interrupt enable register (TIM3_DIER) . . . . . . . . . . . . . . . 469

16.4.5 TIM3 status register (TIM3_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 470

16.4.6 TIM3 event generation register (TIM3_EGR) . . . . . . . . . . . . . . . . . . . 472

16.4.7 TIM3 capture/compare mode register 1 [alternate] (TIM3_CCMR1) . . 473

16.4.8 TIM3 capture/compare mode register 1 [alternate] (TIM3_CCMR1) . . 475

16.4.9 TIM3 capture/compare mode register 2 [alternate] (TIM3_CCMR2) . . 477

16.4.10 TIM3 capture/compare mode register 2 [alternate] (TIM3_CCMR2) . . 478

16.4.11 TIM3 capture/compare enable register

(TIM3_CCER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 479

16.4.12 TIM3 counter [alternate] (TIM3_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . 480

16.4.13 TIM3 counter [alternate] (TIM3_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . 481

16.4.14 TIM3 prescaler (TIM3_PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 481

16.4.15 TIM3 auto-reload register (TIM3_ARR) . . . . . . . . . . . . . . . . . . . . . . . . 482

16.4.16 TIM3 capture/compare register 1 (TIM3_CCR1) . . . . . . . . . . . . . . . . . 482

16.4.17 TIM3 capture/compare register 2 (TIM3_CCR2) . . . . . . . . . . . . . . . . . 483

16.4.18 TIM3 capture/compare register 3 (TIM3_CCR3) . . . . . . . . . . . . . . . . . 483

16.4.19 TIM3 capture/compare register 4 (TIM3_CCR4) . . . . . . . . . . . . . . . . . 484

16.4.20 TIM3 DMA control register (TIM3_DCR) . . . . . . . . . . . . . . . . . . . . . . . 485

16.4.21 TIM3 DMA address for full transfer (TIM3_DMAR) . . . . . . . . . . . . . . . 485

16.4.22 TIM3 alternate function option register 1 (TIM3_AF1) . . . . . . . . . . . . . 485

16.4.23 TIM3 timer input selection register (TIM3_TISEL) . . . . . . . . . . . . . . . . 486

16.4.24 TIMx register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 487

17 Basic timers (TIM6/TIM7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 489

17.1 TIM6/TIM7 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 489

17.2 TIM6/TIM7 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 489

17.3 TIM6/TIM7 functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 490

17.3.1 Time-base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 490

17.3.2 Counting mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 492

17.3.3 UIF bit remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

17.3.4 Clock source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

17.3.5 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 496

17.4 TIM6/TIM7 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 496

Contents RM0454

16/923 RM0454 Rev 3

17.4.1 TIMx control register 1 (TIMx_CR1)(x = 6 to 7) . . . . . . . . . . . . . . . . . . 496

17.4.2 TIMx control register 2 (TIMx_CR2)(x = 6 to 7) . . . . . . . . . . . . . . . . . . 498

17.4.3 TIMx DMA/Interrupt enable register (TIMx_DIER)(x = 6 to 7) . . . . . . . 498

17.4.4 TIMx status register (TIMx_SR)(x = 6 to 7) . . . . . . . . . . . . . . . . . . . . . 499

17.4.5 TIMx event generation register (TIMx_EGR)(x = 6 to 7) . . . . . . . . . . . 499

17.4.6 TIMx counter (TIMx_CNT)(x = 6 to 7) . . . . . . . . . . . . . . . . . . . . . . . . . 499

17.4.7 TIMx prescaler (TIMx_PSC)(x = 6 to 7) . . . . . . . . . . . . . . . . . . . . . . . . 500

17.4.8 TIMx auto-reload register (TIMx_ARR)(x = 6 to 7) . . . . . . . . . . . . . . . 500

17.4.9 TIMx register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 501

18 General-purpose timers (TIM14) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

18.1 TIM14 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

18.2 TIM14 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

18.2.1 TIM14 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

18.3 TIM14 functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 504

18.3.1 Time-base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 504

18.3.2 Counter modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 506

18.3.3 Clock selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 509

18.3.4 Capture/compare channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 510

18.3.5 Input capture mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 511

18.3.6 Forced output mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 512

18.3.7 Output compare mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 513

18.3.8 PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 514

18.3.9 One-pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 515

18.3.10 UIF bit remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 515

18.3.11 Using timer output as trigger for other timers (TIM14) . . . . . . . . . . . . . 516

18.3.12 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 516

18.4 TIM14 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 517

18.4.1 TIM14 control register 1 (TIM14_CR1) . . . . . . . . . . . . . . . . . . . . . . . . 517

18.4.2 TIM14 Interrupt enable register (TIM14_DIER) . . . . . . . . . . . . . . . . . . 518

18.4.3 TIM14 status register (TIM14_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 518

18.4.4 TIM14 event generation register (TIM14_EGR) . . . . . . . . . . . . . . . . . 519

18.4.5 TIM14 capture/compare mode register 1 [alternate] (TIM14_CCMR1) 520

18.4.6 TIM14 capture/compare mode register 1 [alternate] (TIM14_CCMR1) 521

18.4.7 TIM14 capture/compare enable register (TIM14_CCER) . . . . . . . . . . 523

18.4.8 TIM14 counter (TIM14_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 524

18.4.9 TIM14 prescaler (TIM14_PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 525

RM0454 Rev 3 17/923

RM0454 Contents

26

18.4.10 TIM14 auto-reload register (TIM14_ARR) . . . . . . . . . . . . . . . . . . . . . . 525

18.4.11 TIM14 capture/compare register 1 (TIM14_CCR1) . . . . . . . . . . . . . . . 525

18.4.12 TIM14 timer input selection register (TIM14_TISEL) . . . . . . . . . . . . . . 526

18.4.13 TIM14 register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 526

19 General-purpose timers (TIM15/TIM16/TIM17) . . . . . . . . . . . . . . . . . . 528

19.1 TIM15/TIM16/TIM17 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 528

19.2 TIM15 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 528

19.3 TIM16/TIM17 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 529

19.4 TIM15/TIM16/TIM17 functional description . . . . . . . . . . . . . . . . . . . . . . 532

19.4.1 Time-base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 532

19.4.2 Counter modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 534

19.4.3 Repetition counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 538

19.4.4 Clock selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 539

19.4.5 Capture/compare channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 541

19.4.6 Input capture mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 543

19.4.7 PWM input mode (only for TIM15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 544

19.4.8 Forced output mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 545

19.4.9 Output compare mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 546

19.4.10 PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 547

19.4.11 Combined PWM mode (TIM15 only) . . . . . . . . . . . . . . . . . . . . . . . . . . 548

19.4.12 Complementary outputs and dead-time insertion . . . . . . . . . . . . . . . . 549

19.4.13 Using the break function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 551

19.4.14 Bidirectional break inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 556

19.4.15 One-pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 558

19.4.16 Retriggerable one pulse mode (TIM15 only) . . . . . . . . . . . . . . . . . . . . 560

19.4.17 UIF bit remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 560

19.4.18 Timer input XOR function (TIM15 only) . . . . . . . . . . . . . . . . . . . . . . . . 562

19.4.19 External trigger synchronization (TIM15 only) . . . . . . . . . . . . . . . . . . . 563

19.4.20 Slave mode – combined reset trigger mode . . . . . . . . . . . . . . . . . . . 565

19.4.21 DMA burst mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 565

19.4.22 Timer synchronization (TIM15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 567

19.4.23 Using timer output as trigger for other timers (TIM16/TIM17) . . . . . . . 567

19.4.24 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 567

19.5 TIM15 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 568

19.5.1 TIM15 control register 1 (TIM15_CR1) . . . . . . . . . . . . . . . . . . . . . . . . 568

19.5.2 TIM15 control register 2 (TIM15_CR2) . . . . . . . . . . . . . . . . . . . . . . . . 569

Contents RM0454

18/923 RM0454 Rev 3

19.5.3 TIM15 slave mode control register (TIM15_SMCR) . . . . . . . . . . . . . . 571

19.5.4 TIM15 DMA/interrupt enable register (TIM15_DIER) . . . . . . . . . . . . . 572

19.5.5 TIM15 status register (TIM15_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 573

19.5.6 TIM15 event generation register (TIM15_EGR) . . . . . . . . . . . . . . . . . 575

19.5.7 TIM15 capture/compare mode register 1 [alternate]

(TIM15_CCMR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 576

19.5.8 TIM15 capture/compare mode register 1 [alternate]

(TIM15_CCMR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 577

19.5.9 TIM15 capture/compare enable register (TIM15_CCER) . . . . . . . . . . 580

19.5.10 TIM15 counter (TIM15_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 583

19.5.11 TIM15 prescaler (TIM15_PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 583

19.5.12 TIM15 auto-reload register (TIM15_ARR) . . . . . . . . . . . . . . . . . . . . . . 583

19.5.13 TIM15 repetition counter register (TIM15_RCR) . . . . . . . . . . . . . . . . . 584

19.5.14 TIM15 capture/compare register 1 (TIM15_CCR1) . . . . . . . . . . . . . . . 584

19.5.15 TIM15 capture/compare register 2 (TIM15_CCR2) . . . . . . . . . . . . . . . 585

19.5.16 TIM15 break and dead-time register (TIM15_BDTR) . . . . . . . . . . . . . 585

19.5.17 TIM15 DMA control register (TIM15_DCR) . . . . . . . . . . . . . . . . . . . . . 588

19.5.18 TIM15 DMA address for full transfer (TIM15_DMAR) . . . . . . . . . . . . . 588

19.5.19 TIM15 alternate register 1 (TIM15_AF1) . . . . . . . . . . . . . . . . . . . . . . . 589

19.5.20 TIM15 input selection register (TIM15_TISEL) . . . . . . . . . . . . . . . . . . 589

19.5.21 TIM15 register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 590

19.6 TIM16/TIM17 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 593

19.6.1 TIMx control register 1 (TIMx_CR1)(x = 16 to 17) . . . . . . . . . . . . . . . . 593

19.6.2 TIMx control register 2 (TIMx_CR2)(x = 16 to 17) . . . . . . . . . . . . . . . . 594

19.6.3 TIMx DMA/interrupt enable register (TIMx_DIER)(x = 16 to 17) . . . . . 595

19.6.4 TIMx status register (TIMx_SR)(x = 16 to 17) . . . . . . . . . . . . . . . . . . . 596

19.6.5 TIMx event generation register (TIMx_EGR)(x = 16 to 17) . . . . . . . . . 597

19.6.6 TIMx capture/compare mode register 1 [alternate] (TIMx_CCMR1)

(x = 16 to 17) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 598

19.6.7 TIMx capture/compare mode register 1 [alternate] (TIMx_CCMR1)

(x = 16 to 17) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 599

19.6.8 TIMx capture/compare enable register (TIMx_CCER)(x = 16 to 17) . . 601

19.6.9 TIMx counter (TIMx_CNT)(x = 16 to 17) . . . . . . . . . . . . . . . . . . . . . . . 603

19.6.10 TIMx prescaler (TIMx_PSC)(x = 16 to 17) . . . . . . . . . . . . . . . . . . . . . . 604

19.6.11 TIMx auto-reload register (TIMx_ARR)(x = 16 to 17) . . . . . . . . . . . . . 604

19.6.12 TIMx repetition counter register (TIMx_RCR)(x = 16 to 17) . . . . . . . . . 605

19.6.13 TIMx capture/compare register 1 (TIMx_CCR1)(x = 16 to 17) . . . . . . 605

19.6.14 TIMx break and dead-time register (TIMx_BDTR)(x = 16 to 17) . . . . . 606

RM0454 Rev 3 19/923

RM0454 Contents

26

19.6.15 TIMx DMA control register (TIMx_DCR)(x = 16 to 17) . . . . . . . . . . . . . 609

19.6.16 TIMx DMA address for full transfer (TIMx_DMAR)(x = 16 to 17) . . . . . 609

19.6.17 TIM16 alternate function register 1 (TIM16_AF1) . . . . . . . . . . . . . . . . 610

19.6.18 TIM16 input selection register (TIM16_TISEL) . . . . . . . . . . . . . . . . . . 610

19.6.19 TIM17 alternate function register 1 (TIM17_AF1) . . . . . . . . . . . . . . . . 611

19.6.20 TIM17 input selection register (TIM17_TISEL) . . . . . . . . . . . . . . . . . . 611

19.6.21 TIM16/TIM17 register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 612

20 Infrared interface (IRTIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 614

21 Independent watchdog (IWDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 615

21.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 615

21.2 IWDG main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 615

21.3 IWDG functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 615

21.3.1 IWDG block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 615

21.3.2 Window option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 616

21.3.3 Hardware watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 617

21.3.4 Register access protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 617

21.3.5 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 617

21.4 IWDG registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 618

21.4.1 IWDG key register (IWDG_KR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 618

21.4.2 IWDG prescaler register (IWDG_PR) . . . . . . . . . . . . . . . . . . . . . . . . . 619

21.4.3 IWDG reload register (IWDG_RLR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 620

21.4.4 IWDG status register (IWDG_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 621

21.4.5 IWDG window register (IWDG_WINR) . . . . . . . . . . . . . . . . . . . . . . . . 622

21.4.6 IWDG register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 623

22 System window watchdog (WWDG) . . . . . . . . . . . . . . . . . . . . . . . . . . 624

22.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 624

22.2 WWDG main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 624

22.3 WWDG functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 624

22.3.1 WWDG block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 625

22.3.2 Enabling the watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 625

22.3.3 Controlling the down-counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 625

22.3.4 How to program the watchdog timeout . . . . . . . . . . . . . . . . . . . . . . . . 625

22.3.5 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 627

Contents RM0454

20/923 RM0454 Rev 3

22.4 WWDG interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 627

22.5 WWDG registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 627

22.5.1 WWDG control register (WWDG_CR) . . . . . . . . . . . . . . . . . . . . . . . . . 627

22.5.2 WWDG configuration register (WWDG_CFR) . . . . . . . . . . . . . . . . . . . 628

22.5.3 WWDG status register (WWDG_SR) . . . . . . . . . . . . . . . . . . . . . . . . . 629

22.5.4 WWDG register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 629

23 Real-time clock (RTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 630

23.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 630

23.2 RTC main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 630

23.3 RTC functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 631

23.3.1 RTC block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 631

23.3.2 RTC pins and internal signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 632

23.3.3 GPIOs controlled by the RTC and TAMP . . . . . . . . . . . . . . . . . . . . . . . 633

23.3.4 Clock and prescalers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 635

23.3.5 Real-time clock and calendar . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 636

23.3.6 Programmable alarms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 637

23.3.7 Periodic auto-wakeup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 637

23.3.8 RTC initialization and configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 638

23.3.9 Reading the calendar . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 640

23.3.10 Resetting the RTC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 641

23.3.11 RTC synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 641

23.3.12 RTC reference clock detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 642

23.3.13 RTC smooth digital calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 642

23.3.14 Timestamp function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 644

23.3.15 Calibration clock output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 645

23.3.16 Tamper and alarm output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 645

23.4 RTC low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 646

23.5 RTC interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 646

23.6 RTC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 647

23.6.1 RTC time register (RTC_TR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 647

23.6.2 RTC date register (RTC_DR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 648

23.6.3 RTC sub second register (RTC_SSR) . . . . . . . . . . . . . . . . . . . . . . . . . 649

23.6.4 RTC initialization control and status register (RTC_ICSR) . . . . . . . . . 649

23.6.5 RTC prescaler register (RTC_PRER) . . . . . . . . . . . . . . . . . . . . . . . . . 651

23.6.6 RTC wakeup timer register (RTC_WUTR) . . . . . . . . . . . . . . . . . . . . . . 652

RM0454 Rev 3 21/923

RM0454 Contents

26

23.6.7 RTC control register (RTC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 652

23.6.8 RTC write protection register (RTC_WPR) . . . . . . . . . . . . . . . . . . . . . 655

23.6.9 RTC calibration register (RTC_CALR) . . . . . . . . . . . . . . . . . . . . . . . . . 656

23.6.10 RTC shift control register (RTC_SHIFTR) . . . . . . . . . . . . . . . . . . . . . . 657

23.6.11 RTC timestamp time register (RTC_TSTR) . . . . . . . . . . . . . . . . . . . . . 658

23.6.12 RTC timestamp date register (RTC_TSDR) . . . . . . . . . . . . . . . . . . . . 658

23.6.13 RTC timestamp sub second register (RTC_TSSSR) . . . . . . . . . . . . . . 659

23.6.14 RTC alarm A register (RTC_ALRMAR) . . . . . . . . . . . . . . . . . . . . . . . . 660

23.6.15 RTC alarm A sub second register (RTC_ALRMASSR) . . . . . . . . . . . . 661

23.6.16 RTC alarm B register (RTC_ALRMBR) . . . . . . . . . . . . . . . . . . . . . . . . 662

23.6.17 RTC alarm B sub second register (RTC_ALRMBSSR) . . . . . . . . . . . . 663

23.6.18 RTC status register (RTC_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 663

23.6.19 RTC masked interrupt status register (RTC_MISR) . . . . . . . . . . . . . . 664

23.6.20 RTC status clear register (RTC_SCR) . . . . . . . . . . . . . . . . . . . . . . . . . 665

23.6.21 RTC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 667

24 Tamper and backup registers (TAMP) . . . . . . . . . . . . . . . . . . . . . . . . . 669

24.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 669

24.2 TAMP main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 669

24.3 TAMP functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 670

24.3.1 TAMP block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 670

24.3.2 TAMP pins and internal signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 671

24.3.3 TAMP register write protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 671

24.3.4 Tamper detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 672

24.4 TAMP low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 674

24.5 TAMP interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 674

24.6 TAMP registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 674

24.6.1 TAMP control register 1 (TAMP_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . 675

24.6.2 TAMP control register 2 (TAMP_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . 676

24.6.3 TAMP filter control register (TAMP_FLTCR) . . . . . . . . . . . . . . . . . . . . 677

24.6.4 TAMP interrupt enable register (TAMP_IER) . . . . . . . . . . . . . . . . . . . . 678

24.6.5 TAMP status register (TAMP_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 679

24.6.6 TAMP masked interrupt status register (TAMP_MISR) . . . . . . . . . . . . 680

24.6.7 TAMP status clear register (TAMP_SCR) . . . . . . . . . . . . . . . . . . . . . . 681

24.6.8 TAMP backup x register (TAMP_BKPxR) . . . . . . . . . . . . . . . . . . . . . . 682

24.6.9 TAMP register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 683

Contents RM0454

22/923 RM0454 Rev 3

25 Inter-integrated circuit (I2C) interface . . . . . . . . . . . . . . . . . . . . . . . . . 684

25.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 684

25.2 I2C main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 684

25.3 I2C implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 685

25.4 I2C functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 685

25.4.1 I2C1 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 686

25.4.2 I2C2 block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 687

25.4.3 I2C pins and internal signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 688

25.4.4 I2C clock requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 688

25.4.5 Mode selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 688

25.4.6 I2C initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 689

25.4.7 Software reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 694

25.4.8 Data transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 695

25.4.9 I2C slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 697

25.4.10 I2C master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 706

25.4.11 I2C_TIMINGR register configuration examples . . . . . . . . . . . . . . . . . . 718

25.4.12 SMBus specific features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 719

25.4.13 SMBus initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 722

25.4.14 SMBus: I2C_TIMEOUTR register configuration examples . . . . . . . . . 724

25.4.15 SMBus slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 725

25.4.16 Wakeup from Stop mode on address match . . . . . . . . . . . . . . . . . . . . 733

25.4.17 Error conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 733

25.4.18 DMA requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 735

25.4.19 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 736

25.5 I2C low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 736

25.6 I2C interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 737

25.7 I2C registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 738

25.7.1 I2C control register 1 (I2C_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 738

25.7.2 I2C control register 2 (I2C_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 741

25.7.3 I2C own address 1 register (I2C_OAR1) . . . . . . . . . . . . . . . . . . . . . . . 744

25.7.4 I2C own address 2 register (I2C_OAR2) . . . . . . . . . . . . . . . . . . . . . . . 745

25.7.5 I2C timing register (I2C_TIMINGR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 746

25.7.6 I2C timeout register (I2C_TIMEOUTR) . . . . . . . . . . . . . . . . . . . . . . . . 747

25.7.7 I2C interrupt and status register (I2C_ISR) . . . . . . . . . . . . . . . . . . . . . 748

25.7.8 I2C interrupt clear register (I2C_ICR) . . . . . . . . . . . . . . . . . . . . . . . . . 750

25.7.9 I2C PEC register (I2C_PECR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 751

RM0454 Rev 3 23/923

RM0454 Contents

26

25.7.10 I2C receive data register (I2C_RXDR) . . . . . . . . . . . . . . . . . . . . . . . . 752

25.7.11 I2C transmit data register (I2C_TXDR) . . . . . . . . . . . . . . . . . . . . . . . . 752

25.7.12 I2C register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 753

26 Universal synchonous receiver transmitter (USART) . . . . . . . . . . . . 755

26.1 USART introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 755

26.2 USART main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 756

26.3 USART extended features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 757

26.4 USART implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 757

26.5 USART functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 759

26.5.1 USART block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 759

26.5.2 USART signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 760

26.5.3 USART character description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 761

26.5.4 USART FIFOs and thresholds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 763

26.5.5 USART transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 763