实例介绍

【实例截图】

【核心代码】

Table of Contents

1. MIPS 24K PROCESSOR 11

1.1 F EATURES 11

1.2 B LOCK D IAGRAM 12

1.3 M EMORY M AP S UMMARY 13

1.4 C LOCK P LAN 14

1.5 CPU C LOCK M UX 15

2. REGISTERS 16

2.1 N OMENCLATURE 16

2.2 S YSTEM C ONTROL 17

2.2.1 F EATURES 17

2.2.2 B LOCK D IAGRAM 17

2.2.3 L IST OF R EGISTERS 18

2.2.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0000) 19

2.3 T IMER 46

2.3.1 F EATURES 46

2.3.2 B LOCK D IAGRAM 47

2.3.3 L IST OF R EGISTERS 48

2.3.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0100) 49

2.4 I NTERRUPT C ONTROLLER 53

2.4.1 F EATURES 53

2.4.2 B LOCK D IAGRAM 53

2.4.3 L IST OF R EGISTERS 54

2.4.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0200) 55

2.5 S YSTEM T ICK C OUNTER 60

2.5.1 L IST OF R EGISTERS 60

2.5.2 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0 D 00) 61

2.6 UART 62

2.6.1 F EATURES 62

2.6.2 B LOCK D IAGRAM 62

2.6.3 L IST OF R EGISTERS 63

2.6.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0500) 64

2.7 UART L ITE 72

2.7.1 F EATURES 72

2.7.2 B LOCK D IAGRAM 72

2.7.3 L IST OF R EGISTERS 73

2.7.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0C00) 74

2.8 P ROGRAMMABLE I/O 81

2.8.1 F EATURES 81

2.8.2 B LOCK D IAGRAM 81

2.8.3 L IST OF R EGISTERS 82

2.8.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0600) 84

2.9 I 2 C C ONTROLLER 97

2.9.1 F EATURES 97

2.9.2 B LOCK D IAGRAM 97

2.9.3 L IST OF R EGISTERS 98

PGMT7620_V.1.0_040503 Page 4 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

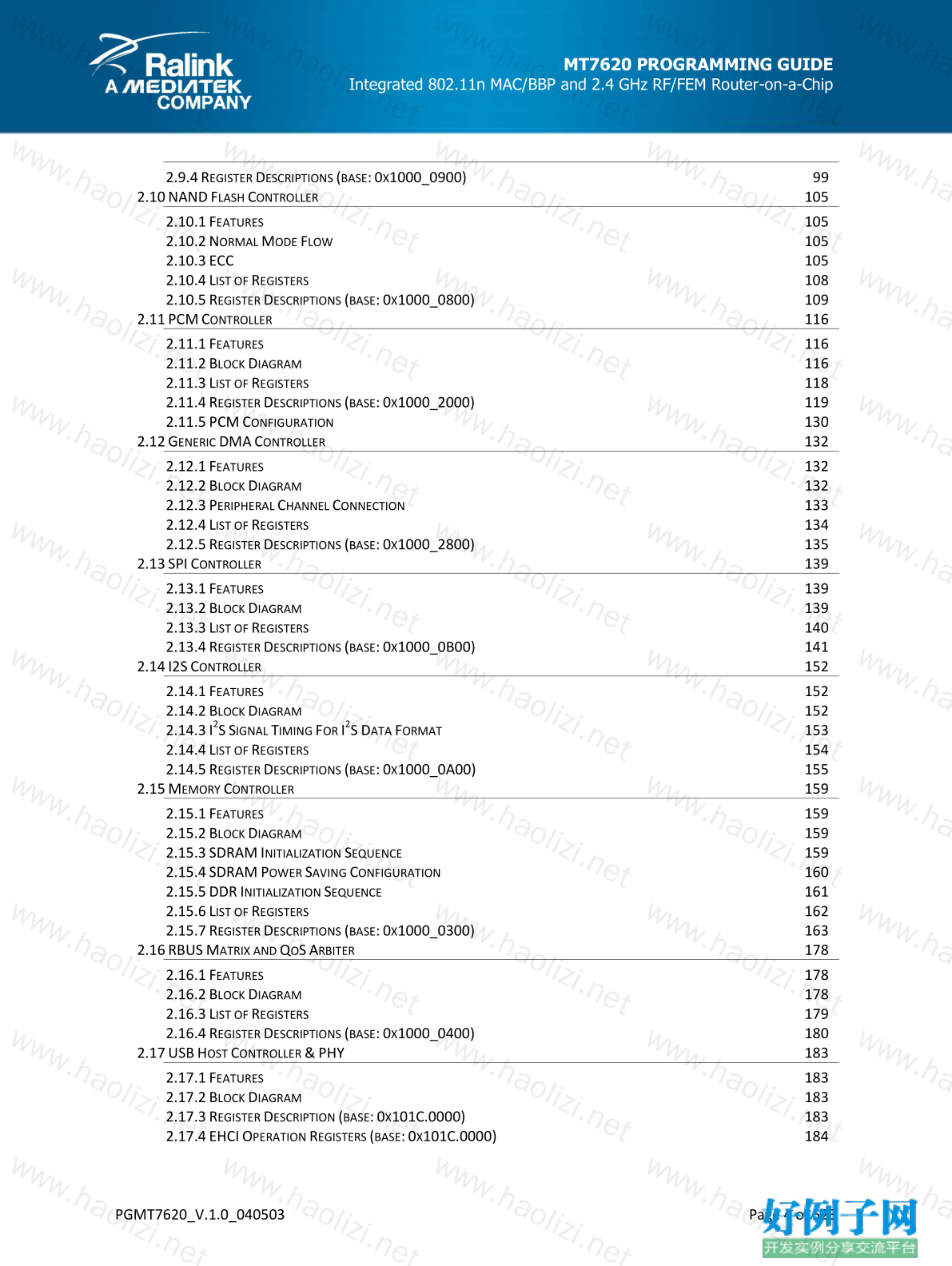

2.9.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0900) 99

2.10 NAND F LASH C ONTROLLER 105

2.10.1 F EATURES 105

2.10.2 N ORMAL M ODE F LOW 105

2.10.3 ECC 105

2.10.4 L IST OF R EGISTERS 108

2.10.5 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0800) 109

2.11 PCM C ONTROLLER 116

2.11.1 F EATURES 116

2.11.2 B LOCK D IAGRAM 116

2.11.3 L IST OF R EGISTERS 118

2.11.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_2000) 119

2.11.5 PCM C ONFIGURATION 130

2.12 G ENERIC DMA C ONTROLLER 132

2.12.1 F EATURES 132

2.12.2 B LOCK D IAGRAM 132

2.12.3 P ERIPHERAL C HANNEL C ONNECTION 133

2.12.4 L IST OF R EGISTERS 134

2.12.5 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_2800) 135

2.13 SPI C ONTROLLER 139

2.13.1 F EATURES 139

2.13.2 B LOCK D IAGRAM 139

2.13.3 L IST OF R EGISTERS 140

2.13.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0B00) 141

2.14 I2S C ONTROLLER 152

2.14.1 F EATURES 152

2.14.2 B LOCK D IAGRAM 152

2.14.3 I 2 S S IGNAL T IMING F OR I 2 S D ATA F ORMAT 153

2.14.4 L IST OF R EGISTERS 154

2.14.5 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0A00) 155

2.15 M EMORY C ONTROLLER 159

2.15.1 F EATURES 159

2.15.2 B LOCK D IAGRAM 159

2.15.3 SDRAM I NITIALIZATION S EQUENCE 159

2.15.4 SDRAM P OWER S AVING C ONFIGURATION 160

2.15.5 DDR I NITIALIZATION S EQUENCE 161

2.15.6 L IST OF R EGISTERS 162

2.15.7 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0300) 163

2.16 RBUS M ATRIX AND Q O S A RBITER 178

2.16.1 F EATURES 178

2.16.2 B LOCK D IAGRAM 178

2.16.3 L IST OF R EGISTERS 179

2.16.4 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1000_0400) 180

2.17 USB H OST C ONTROLLER & PHY 183

2.17.1 F EATURES 183

2.17.2 B LOCK D IAGRAM 183

2.17.3 R EGISTER D ESCRIPTION ( BASE : 0 X 101C.0000) 183

2.17.4 EHCI O PERATION R EGISTERS ( BASE : 0 X 101C.0000) 184

PGMT7620_V.1.0_040503 Page 5 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.17.5 OHCI O PERATION R EGISTERS ( BASE : 0 X 101C.1000) 185

2.18 USB D EVICE C ONTROLLER 186

2.18.1 F EATURES 186

2.18.2 B LOCK D IAGRAM 186

2.18.3 B ULK O UT 186

2.18.4 L EGACY M ODE 187

2.18.5 A GGREGATION M ODE 187

2.18.6 D E -A GGREGATION M ODE 188

2.18.7 B ULK - OUT A GGREGATION F ORMAT 189

2.18.8 B ULK IN 189

2.18.9 PDMA D ESCRIPTOR F ORMAT 190

2.18.10 R EGISTER D ESCRIPTIONS ( BASE : 0 X 1012_0000) 192

2.18.11 USB D EVICE C ONTROLLER R EGISTERS 192

2.18.12 UDMA R EGISTERS 193

2.18.13 PDMA R EGISTERS 194

2.19 F RAME E NGINE 202

2.19.1 PSE F EATURES 202

2.19.2 PPE F EATURES 202

2.19.3 P ACKET DMA (PDMA) F EATURES 202

2.19.4 B LOCK D IAGRAM 203

2.19.5 PDMA FIFO- LIKE R ING C ONCEPT 204

2.19.6 PDMA T X D ESCRIPTOR F ORMAT 205

2.19.7 PDMA R X D ESCRIPTOR F ORMAT 207

2.19.8 G LOBAL R EGISTERS ( BASE : 0 X 1010_0000) 209

2.19.9 CPU P ORT R EGISTERS ( BASE : 0 X 1010_0400) 216

2.19.10 PDMA R EGISTERS ( BASE : 0 X 1010_0800) 223

2.19.11 MIB C OUNTER D ESCRIPTION ( BASE : 0 X 1010_1000) 235

2.20 E THERNET S WITCH 237

2.20.1 F EATURES 237

2.20.2 B LOCK D IAGRAM 238

2.20.3 F RAME C LASSFICATION 238

2.20.4 S WITCH L2/L3 A DDRESS T ABLE 240

2.20.5 V IRTUAL LAN 244

2.20.6 A CCESS C ONTROL L OGIC 247

2.20.7 ARL R EGISTERS ( BASE : 0 X 1011_0000) 252

2.20.8 BMU R EGISTERS 291

2.20.9 PORT R EGISTERS 308

2.20.10 MAC R EGISTERS 320

2.20.11 MIB R EGISTERS 329

2.20.12 GSW C ONFIGURATION R EGISTERS 338

2.20.13 MDIO C ONTROL 347

2.21 PCI/PCI E C ONTROLLER 354

2.21.1 B LOCK D IAGRAM 355

2.21.2 PCI E C ONTROLLER A CTING AS A PCI E D EVICE 356

2.21.3 B LOCK D IAGRAM 357

2.21.4 PCI/PCI E M ASTER A CCESS I N H OST M ODE 358

2.21.5 PCI E C ONTROLLER H OST M ODE I NITIALIZATON E XAMPLE 359

2.21.6 H OST -PCI B RIDGE R EGISTERS ( BASE : 0 X 1014_0000) 359

2.21.7 PCI E 0 RC C ONTROL R EGISTERS ( BASE : 0 X 1014_2000) 363

PGMT7620_V.1.0_040503 Page 6 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.21.8 M EMORY W INDOWS R EGISTERS ( BASE : 0 X 1015_0000) 367

2.21.9 IO W INDOWS ( BASE : 0 X 1016_0000) 367

2.22 802.11 N 2T2R MAC/BBP 368

2.22.1 F EATURES 368

2.22.2 B LOCK D IAGRAM 368

2.22.3 802.11 N 2T2R MAC/BBP R EGISTER M AP 369

2.22.4 SCH/WPDMA R EGISTERS ( BASE : 0 X 1018_0000) 370

2.22.5 PBF R EGISTERS ( BASE : 0 X 1018_0000) 382

2.22.6 RF TEST R EGISTERS ( BASE : 0 X 1018_0000) 392

2.22.7 MAC R EGISTERS ( BASE : 0 X 1018_0000) 393

2.22.8 MAC T IMING C ONTROL R EGISTERS ( BASE : 0 X 1018_0000) 409

2.22.9 MAC P OWER S AVE C ONFIGURATION R EGISTERS ( BASE : 0 X 1018_0000) 416

2.22.10 MAC T X C ONFIGURATION R EGISTERS ( BASE : 0 X 1018_0000) 421

2.22.11 MAC R X C ONFIGURATION R EGISTERS ( BASE : 0 X 1018_0000) 449

2.22.12 MAC S ECURITY C ONFIGURATION R EGISTERS ( BASE : 0 X 1018_0000) 457

2.22.13 MAC HCCA/PSMP C ONTROL S TATUS R EGISTERS ( BASE : 0 X 1018_0000) 458

2.22.14 MAC S TATISTIC C OUNTERS ( BASE : 0 X 1018_0000) 462

2.22.15 MAC S EARCH T ABLE ( BASE : 0 X 1018_1800) 471

3. SECURITY ENTRY FORMATS AND KEY TABLES 473

3.1 S ECURITY E NTRY F ORMAT T ABLES ( BASE : 1018.0000, OFFSET : 0 X 4000) 473

3.1.1 S ECURITY K EY F ORMAT (8DW) 473

3.1.2 IV/EIV/WAPI_PN F ORMAT (4DW) 473

3.1.3 WCID A TTRIBUTE E NTRY F ORMAT (1DW) 474

3.1.4 S HARED K EY M ODE E NTRY F ORMAT (1DW) 475

3.2 S ECURITY T ABLES ( OFFSET : 0 X 4000) 476

3.3 S ECURITY T ABLE M AP 476

3.3.1 P AIRWISE K EY T ABLE ( OFFSET : 0 X 4000) 477

3.3.2 IV/EIV T ABLE ( OFFSET : 0 X 6000) 477

3.3.3 WCID A TTRIBUTE T ABLE ( OFFSET : 0 X 6800) 477

3.3.4 S HARED K EY T ABLE ( OFFSET : 0 X 6C00) 477

3.3.5 S HARED K EY M ODE ( OFFSET : 0 X 7000) 478

3.3.6 S PARE M EMORY S PACE M ODE ( OFFSET : 0 X 7010 TO 0 X 73EC) 478

3.3.7 S HARED K EY M ODE E XTENSION ( FOR BSS_IDX=8 TO 15) ( OFFSET : 0 X 73F0) 479

3.3.8 S HARED K EY T ABLE E XTENSION ( FOR BSS_IDX=8 TO 15) ( OFFSET : 0 X 7400) 479

3.3.9 WAPI PN T ABLE (E XTENSION OF IV/EIV T ABLE ) ( OFFSET : 0 X 7800) 480

4. TX/RX DESCRIPTORS AND WIRELESS INFORMATION 481

4.1 T X D ESCRIPTORS AND F RAME I NFORMATION 481

4.1.1 TXD F ORMAT 482

4.1.2 T X W IRELESS I NFORMATION 484

4.2 R X D ESCRIPTORS AND W IRELESS I NFORMATION 488

4.2.1 RXD F ORMAT 489

4.2.2 RXINFO F ORMAT 490

4.2.3 RXWI F ORMAT 492

4.3 B RIEF PHY R ATE F ORMAT AND D EFINITION 494

4.3.1 M ODULATION AND C ODING S CHEME 495

5. SD HOST CONTROLLER 497

5.1 F EATURES 497

PGMT7620_V.1.0_040503 Page 7 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

5.2 SD H OST B LOCK D IAGRAM 497

5.2.1 B ASIC DMA M ODE 498

5.2.2 L INKED -L IST B ASED DMA M ODE 498

5.2.3 DMA G ENERIC P ACKET D ESCRIPTOR (GPD) F ORMAT 500

5.2.4 DMA B UFFER D ESCRIPTOR (BD) F ORMAT 502

5.2.5 R EGISTER D ESCRIPTION ( BASE : 0 X 1013_0000) 503

6. LIST OF REGISTERS 504

7. ABBREVIATIONS 520

8. REVISION HISTORY 523

标签: MT

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论