实例介绍

【实例截图】

【核心代码】

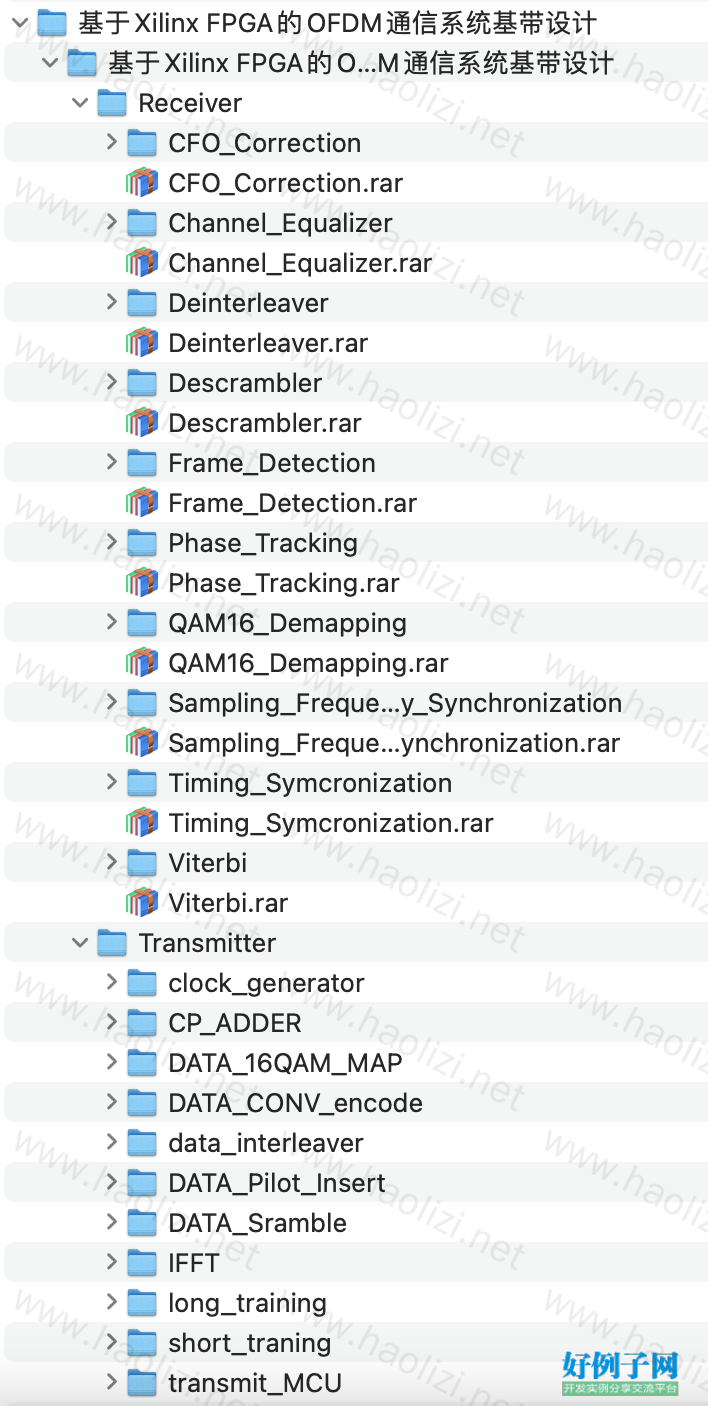

基于Xilinx FPGA的OFDM通信系统基带设计

└── 基于Xilinx FPGA的OFDM通信系统基带设计

├── Receiver

│ ├── CFO_Correction

│ │ ├── CFO_Compensation.v

│ │ ├── CFO_Compensation_summary.html

│ │ ├── CFO_Correction.ise

│ │ ├── CFO_Correction.ise_ISE_Backup

│ │ ├── CFO_Correction.restore

│ │ ├── CFO_Correction.v

│ │ ├── CFO_Correction_summary.html

│ │ ├── CFO_Estimating.v

│ │ ├── Coefficient_Estimation.v

│ │ ├── Compensation_Estimation.v

│ │ ├── Complement.v

│ │ ├── Correlation_Accumulation.v

│ │ ├── Data_Buffer_For_STS.v

│ │ ├── Data_Combination.v

│ │ ├── Data_Separating.v

│ │ ├── DelayCorrelation.v

│ │ ├── DelayForComp.v

│ │ ├── Estimation_phase.v

│ │ ├── Width9_Multiply_Width8.asy

│ │ ├── __ISE_repository_CFO_Correction.ise_.lock

│ │ ├── _xmsgs

│ │ ├── cordicdemonew.edn

│ │ ├── cordicdemonew.sym

│ │ ├── cordicdemonew.v

│ │ ├── cordicdemonew.veo

│ │ ├── cordicdemonew.vhd

│ │ ├── cordicdemonew.vho

│ │ ├── cordicdemonew.xco

│ │ ├── cordicdemosincos.edn

│ │ ├── cordicdemosincos.sym

│ │ ├── cordicdemosincos.v

│ │ ├── cordicdemosincos.veo

│ │ ├── cordicdemosincos.vhd

│ │ ├── cordicdemosincos.vho

│ │ ├── cordicdemosincos.xco

│ │ ├── shiftramlength16width16.edn

│ │ ├── shiftramlength16width16.mif

│ │ ├── shiftramlength16width16.sym

│ │ ├── shiftramlength16width16.v

│ │ ├── shiftramlength16width16.veo

│ │ ├── shiftramlength16width16.vhd

│ │ ├── shiftramlength16width16.vho

│ │ ├── shiftramlength16width16.xco

│ │ ├── shiftramlength16width8.edn

│ │ ├── shiftramlength16width8.mif

│ │ ├── shiftramlength16width8.sym

│ │ ├── shiftramlength16width8.v

│ │ ├── shiftramlength16width8.veo

│ │ ├── shiftramlength16width8.vhd

│ │ ├── shiftramlength16width8.vho

│ │ ├── shiftramlength16width8.xco

│ │ ├── shiftramlength27width16.asy

│ │ ├── shiftramlength27width16.edn

│ │ ├── shiftramlength27width16.sym

│ │ ├── shiftramlength27width16.v

│ │ ├── shiftramlength27width16.veo

│ │ ├── shiftramlength27width16.vhd

│ │ ├── shiftramlength27width16.vho

│ │ ├── shiftramlength27width16.xco

│ │ ├── templates

│ │ │ └── coregen.xml

│ │ ├── width9_multiply_width8.edn

│ │ ├── width9_multiply_width8.sym

│ │ ├── width9_multiply_width8.v

│ │ ├── width9_multiply_width8.veo

│ │ ├── width9_multiply_width8.vhd

│ │ ├── width9_multiply_width8.vho

│ │ └── width9_multiply_width8.xco

│ ├── CFO_Correction.rar

│ ├── Channel_Equalizer

│ │ ├── ChannelCompensation.v

│ │ ├── ChannelEstimating.v

│ │ ├── Channel_Equalizer.ise

│ │ ├── Channel_Equalizer.ise_ISE_Backup

│ │ ├── Channel_Equalizer.restore

│ │ ├── Channel_Equalizer.v

│ │ ├── Channel_Equalizer_summary.html

│ │ ├── EnergyComputation.v

│ │ ├── LTS_Picking.v

│ │ ├── __ISE_repository_Channel_Equalizer.ise_.lock

│ │ ├── _xmsgs

│ │ ├── longtrainingvalue.edn

│ │ ├── longtrainingvalue.mif

│ │ ├── longtrainingvalue.sym

│ │ ├── longtrainingvalue.v

│ │ ├── longtrainingvalue.veo

│ │ ├── longtrainingvalue.vhd

│ │ ├── longtrainingvalue.vho

│ │ ├── longtrainingvalue.xco

│ │ ├── ramlength64width8.edn

│ │ ├── ramlength64width8.sym

│ │ ├── ramlength64width8.v

│ │ ├── ramlength64width8.veo

│ │ ├── ramlength64width8.vhd

│ │ ├── ramlength64width8.vho

│ │ ├── ramlength64width8.xco

│ │ ├── templates

│ │ │ └── coregen.xml

│ │ ├── width8_multiply_width8.asy

│ │ ├── width8_multiply_width8.edn

│ │ ├── width8_multiply_width8.sym

│ │ ├── width8_multiply_width8.v

│ │ ├── width8_multiply_width8.veo

│ │ ├── width8_multiply_width8.vhd

│ │ ├── width8_multiply_width8.vho

│ │ ├── width8_multiply_width8.xco

│ │ ├── width9_multiply_width8.asy

│ │ ├── width9_multiply_width8.edn

│ │ ├── width9_multiply_width8.sym

│ │ ├── width9_multiply_width8.v

│ │ ├── width9_multiply_width8.veo

│ │ ├── width9_multiply_width8.vhd

│ │ ├── width9_multiply_width8.vho

│ │ └── width9_multiply_width8.xco

│ ├── Channel_Equalizer.rar

│ ├── Deinterleaver

│ │ ├── Deinterleaver.ise

│ │ ├── Deinterleaver.ise_ISE_Backup

│ │ ├── Deinterleaver.restore

│ │ ├── __ISE_repository_Deinterleaver.ise_.lock

│ │ ├── _xmsgs

│ │ ├── convert1_4.v

│ │ ├── convert4_1.v

│ │ ├── deinterleave.v

│ │ ├── deinterleave1.v

│ │ ├── deinterleave2.v

│ │ ├── deinterleave2_core.v

│ │ ├── deinterleave_summary.html

│ │ ├── dualramlength512.asy

│ │ ├── dualramlength512.edn

│ │ ├── dualramlength512.sym

│ │ ├── dualramlength512.v

│ │ ├── dualramlength512.veo

│ │ ├── dualramlength512.vhd

│ │ ├── dualramlength512.vho

│ │ ├── dualramlength512.xco

│ │ └── templates

│ │ └── coregen.xml

│ ├── Deinterleaver.rar

│ ├── Descrambler

│ │ ├── Descrambler.ise

│ │ ├── Descrambler.ise_ISE_Backup

│ │ ├── Descrambler.restore

│ │ ├── Descrambler.v

│ │ ├── Descrambler_summary.html

│ │ ├── __ISE_repository_Descrambler.ise_.lock

│ │ └── _xmsgs

│ ├── Descrambler.rar

│ ├── Frame_Detection

│ │ ├── Correlation_Accumulation.v

│ │ ├── Correlation_Window_Energy_Computing.v

│ │ ├── Data_Buffer_For_Delay.v

│ │ ├── Data_Buffer_Shiftram.v

│ │ ├── Delay_Correlation_Computing.v

│ │ ├── Delay_Correlation_Energy_Computing.v

│ │ ├── Energy_Accumulation.v

│ │ ├── Energy_Computing.v

│ │ ├── Frame_Detection.ise

│ │ ├── Frame_Detection.ise_ISE_Backup

│ │ ├── Frame_Detection.restore

│ │ ├── Frame_Detection.v

│ │ ├── Frame_Detection_summary.html

│ │ ├── Frame_Finding.v

│ │ ├── Range_Simplified_Computing.v

│ │ ├── Top_Control.v

│ │ ├── __ISE_repository_Frame_Detection.ise_.lock

│ │ ├── _xmsgs

│ │ ├── shiftramlength16width16.asy

│ │ ├── shiftramlength16width16.edn

│ │ ├── shiftramlength16width16.mif

│ │ ├── shiftramlength16width16.sym

│ │ ├── shiftramlength16width16.v

│ │ ├── shiftramlength16width16.veo

│ │ ├── shiftramlength16width16.vhd

│ │ ├── shiftramlength16width16.vho

│ │ ├── shiftramlength16width16.xco

│ │ ├── shiftramlength16width17.edn

│ │ ├── shiftramlength16width17.mif

│ │ ├── shiftramlength16width17.sym

│ │ ├── shiftramlength16width17.v

│ │ ├── shiftramlength16width17.veo

│ │ ├── shiftramlength16width17.vhd

│ │ ├── shiftramlength16width17.vho

│ │ ├── shiftramlength16width17.xco

│ │ ├── shiftramlength16width8.asy

│ │ ├── shiftramlength16width8.edn

│ │ ├── shiftramlength16width8.mif

│ │ ├── shiftramlength16width8.sym

│ │ ├── shiftramlength16width8.v

│ │ ├── shiftramlength16width8.veo

│ │ ├── shiftramlength16width8.vhd

│ │ ├── shiftramlength16width8.vho

│ │ ├── shiftramlength16width8.xco

│ │ ├── shiftramlength48width8.asy

│ │ ├── shiftramlength48width8.edn

│ │ ├── shiftramlength48width8.sym

│ │ ├── shiftramlength48width8.v

│ │ ├── shiftramlength48width8.veo

│ │ ├── shiftramlength48width8.vhd

│ │ ├── shiftramlength48width8.vho

│ │ ├── shiftramlength48width8.xco

│ │ ├── templates

│ │ │ └── coregen.xml

│ │ ├── width8_multiply_width8.asy

│ │ ├── width8_multiply_width8.edn

│ │ ├── width8_multiply_width8.sym

│ │ ├── width8_multiply_width8.v

│ │ ├── width8_multiply_width8.veo

│ │ ├── width8_multiply_width8.vhd

│ │ ├── width8_multiply_width8.vho

│ │ ├── width8_multiply_width8.xco

│ │ ├── width9_multiply_width8.asy

│ │ ├── width9_multiply_width8.edn

│ │ ├── width9_multiply_width8.sym

│ │ ├── width9_multiply_width8.v

│ │ ├── width9_multiply_width8.veo

│ │ ├── width9_multiply_width8.vhd

│ │ ├── width9_multiply_width8.vho

│ │ └── width9_multiply_width8.xco

│ ├── Frame_Detection.rar

│ ├── Phase_Tracking

│ │ ├── Compensated_Factor_Computing.v

│ │ ├── Phase_Tracking.ise

│ │ ├── Phase_Tracking.ise_ISE_Backup

│ │ ├── Phase_Tracking.restore

│ │ ├── Phase_Tracking.v

│ │ ├── Phase_Tracking_summary.html

│ │ ├── Pilots_Picking_and_Data_Buffer.v

│ │ ├── RFO_Compensation.v

│ │ ├── __ISE_repository_Phase_Tracking.ise_.lock

│ │ ├── _xmsgs

│ │ ├── ramlength64width10.asy

│ │ ├── ramlength64width10.edn

│ │ ├── ramlength64width10.sym

│ │ ├── ramlength64width10.v

│ │ ├── ramlength64width10.veo

│ │ ├── ramlength64width10.vhd

│ │ ├── ramlength64width10.vho

│ │ ├── ramlength64width10.xco

│ │ ├── scrambler.v

│ │ ├── templates

│ │ │ └── coregen.xml

│ │ ├── width11_multiply_width10.edn

│ │ ├── width11_multiply_width10.sym

│ │ ├── width11_multiply_width10.v

│ │ ├── width11_multiply_width10.veo

│ │ ├── width11_multiply_width10.vhd

│ │ ├── width11_multiply_width10.vho

│ │ └── width11_multiply_width10.xco

│ ├── Phase_Tracking.rar

│ ├── QAM16_Demapping

│ │ ├── Data_Buffer.v

│ │ ├── Factor_Buffer.asy

│ │ ├── QAM16.v

│ │ ├── QAM16_Demapping.ise

│ │ ├── QAM16_Demapping.ise_ISE_Backup

│ │ ├── QAM16_Demapping.restore

│ │ ├── QAM16_Demapping.v

│ │ ├── QAM16_Demapping_summary.html

│ │ ├── Threshold_Adjusting.v

│ │ ├── __ISE_repository_QAM16_Demapping.ise_.lock

│ │ ├── _xmsgs

│ │ ├── factor_buffer.edn

│ │ ├── factor_buffer.sym

│ │ ├── factor_buffer.v

│ │ ├── factor_buffer.veo

│ │ ├── factor_buffer.vhd

│ │ ├── factor_buffer.vho

│ │ ├── factor_buffer.xco

│ │ └── templates

│ │ └── coregen.xml

│ ├── QAM16_Demapping.rar

│ ├── Sampling_Frequency_Synchronization

│ │ ├── COM_MULTIPLIER.v

│ │ ├── Complement.v

│ │ ├── DATA_BUF.v

│ │ ├── OFFSET_COM.v

│ │ ├── Order_Rechanged.v

│ │ ├── PILOTS_COR.v

│ │ ├── Sampling_Frequency_Synchronization.ise

│ │ ├── Sampling_Frequency_Synchronization.ise_ISE_Backup

│ │ ├── Sampling_Frequency_Synchronization.restore

│ │ ├── Sampling_Frequency_Synchronization.v

│ │ ├── Sampling_Frequency_Synchronization_summary.html

│ │ ├── Scrambler.v

│ │ ├── __ISE_repository_Sampling_Frequency_Synchronization.ise_.lock

│ │ ├── _xmsgs

│ │ ├── bram.edn

│ │ ├── bram.sym

│ │ ├── bram.v

│ │ ├── bram.veo

│ │ ├── bram.vhd

│ │ ├── bram.vho

│ │ ├── bram.xco

│ │ ├── com_sig.edn

│ │ ├── com_sig.sym

│ │ ├── com_sig.v

│ │ ├── com_sig.veo

│ │ ├── com_sig.vhd

│ │ ├── com_sig.vho

│ │ ├── com_sig.xco

│ │ ├── cr_bram.asy

│ │ ├── cr_bram.edn

│ │ ├── cr_bram.sym

│ │ ├── cr_bram.v

│ │ ├── cr_bram.veo

│ │ ├── cr_bram.vhd

│ │ ├── cr_bram.vho

│ │ ├── cr_bram.xco

│ │ ├── cr_bram_flist.txt

│ │ ├── cr_bram_readme.txt

│ │ ├── cr_bram_xmdf.tcl

│ │ ├── offset_est.v

│ │ ├── phase_est.edn

│ │ ├── phase_est.sym

│ │ ├── phase_est.v

│ │ ├── phase_est.veo

│ │ ├── phase_est.vhd

│ │ ├── phase_est.vho

│ │ ├── phase_est.xco

│ │ ├── sm_acc.edn

│ │ ├── sm_acc.sym

│ │ ├── sm_acc.v

│ │ ├── sm_acc.veo

│ │ ├── sm_acc.vhd

│ │ ├── sm_acc.vho

│ │ ├── sm_acc.xco

│ │ ├── templates

│ │ │ └── coregen.xml

│ │ ├── tmp

│ │ │ └── _cg

│ │ ├── width11_multiply_width10.edn

│ │ ├── width11_multiply_width10.sym

│ │ ├── width11_multiply_width10.v

│ │ ├── width11_multiply_width10.veo

│ │ ├── width11_multiply_width10.vhd

│ │ ├── width11_multiply_width10.vho

│ │ └── width11_multiply_width10.xco

│ ├── Sampling_Frequency_Synchronization.rar

│ ├── Timing_Symcronization

│ │ ├── Correlating_and_Accumulating.v

│ │ ├── Magnitude_Simplified_Computing.v

│ │ ├── Match_Filtering.v

│ │ ├── Peak_Finding.v

│ │ ├── Quantization.v

│ │ ├── Simple_Correlation.v

│ │ ├── Symbol_Output.v

│ │ ├── Time_Syncronization.v

│ │ ├── Time_Syncronization_summary.html

│ │ ├── Timing_Symcronization.ise

│ │ ├── Timing_Symcronization.ise_ISE_Backup

│ │ ├── Timing_Symcronization.restore

│ │ ├── __ISE_repository_Timing_Symcronization.ise_.lock

│ │ └── _xmsgs

│ ├── Timing_Symcronization.rar

│ ├── Viterbi

│ │ ├── Viterbi.ise

│ │ ├── Viterbi.ise_ISE_Backup

│ │ ├── Viterbi.restore

│ │ ├── Viterbi.v

│ │ ├── Viterbi_summary.html

│ │ ├── __ISE_repository_Viterbi.ise_.lock

│ │ ├── _xmsgs

│ │ ├── acsCombine.v

│ │ ├── acsCompare.v

│ │ ├── acsadd.v

│ │ ├── acsunit.v

│ │ ├── dRam.v

│ │ ├── distance.v

│ │ ├── smaller.v

│ │ └── tb_trace.v

│ └── Viterbi.rar

└── Transmitter

├── CP_ADDER

│ ├── CP_ADDER.ise

│ ├── CP_ADDER.ise_ISE_Backup

│ ├── CP_ADDER.restore

│ ├── CP_adder.v

│ ├── CP_adder_summary.html

│ ├── _xmsgs

│ ├── bram1I.asy

│ ├── bram1i.edn

│ ├── bram1i.sym

│ ├── bram1i.v

│ ├── bram1i.veo

│ ├── bram1i.vhd

│ ├── bram1i.vho

│ ├── bram1i.xco

│ ├── bram1r.asy

│ ├── bram1r.edn

│ ├── bram1r.sym

│ ├── bram1r.v

│ ├── bram1r.veo

│ ├── bram1r.vhd

│ ├── bram1r.vho

│ ├── bram1r.xco

│ ├── bram2i.asy

│ ├── bram2i.edn

│ ├── bram2i.sym

│ ├── bram2i.v

│ ├── bram2i.veo

│ ├── bram2i.vhd

│ ├── bram2i.vho

│ ├── bram2i.xco

│ ├── bram2r.asy

│ ├── bram2r.edn

│ ├── bram2r.sym

│ ├── bram2r.v

│ ├── bram2r.veo

│ ├── bram2r.vhd

│ ├── bram2r.vho

│ ├── bram2r.xco

│ └── templates

│ └── coregen.xml

├── DATA_16QAM_MAP

│ ├── DATA_16AM_MAP.ise

│ ├── DATA_16AM_MAP.ise_ISE_Backup

│ ├── DATA_16AM_MAP.restore

│ ├── DATA_16QAM_MAP.v

│ ├── DATA_16QAM_MAP_summary.html

│ ├── DATA_16QAM_mapper_summary.html

│ └── _xmsgs

├── DATA_CONV_encode

│ ├── DATA_CONV_encode.ise

│ ├── DATA_CONV_encode.ise_ISE_Backup

│ ├── DATA_CONV_encode.restore

│ ├── DATA_Conv_encode.v

│ ├── DATA_Conv_encode_summary.html

│ ├── DATA_conv_encoder_summary.html

│ ├── _xmsgs

│ └── conv_encoder.v

├── DATA_Pilot_Insert

│ ├── DATA_Pilot_Insert.ise

│ ├── DATA_Pilot_Insert.ise_ISE_Backup

│ ├── DATA_Pilot_Insert.restore

│ ├── DATA_Pilot_Insert.v

│ ├── DATA_Pilot_Insert_summary.html

│ ├── DATA_pilot_insertion_summary.html

│ └── _xmsgs

├── DATA_Sramble

│ ├── DATA_Sramble.ise

│ ├── DATA_Sramble.ise_ISE_Backup

│ ├── DATA_Sramble.restore

│ ├── DATA_scramble.v

│ ├── DATA_scramble_summary.html

│ └── _xmsgs

├── IFFT

│ └── IFFT

│ ├── FFT_Pro_new_summary.html

│ ├── FFT_Pro_summary.html

│ ├── IFFT.ise

│ ├── IFFT.ise_ISE_Backup

│ ├── IFFT.restore

│ ├── IFFT.v

│ ├── IFFT_summary.html

│ ├── _xmsgs

│ ├── change60_new.v

│ ├── channge20_new.v

│ ├── dataromi.asy

│ ├── dataromi.edn

│ ├── dataromi.sym

│ ├── dataromi.v

│ ├── dataromi.veo

│ ├── dataromi.vhd

│ ├── dataromi.vho

│ ├── dataromi.xco

│ ├── dataromr.asy

│ ├── dataromr.edn

│ ├── dataromr.sym

│ ├── dataromr.v

│ ├── dataromr.veo

│ ├── dataromr.vhd

│ ├── dataromr.vho

│ ├── dataromr.xco

│ ├── fft_Burst.v

│ ├── fft_test.asy

│ ├── fft_test.edn

│ ├── fft_test.sym

│ ├── fft_test.v

│ ├── fft_test.veo

│ ├── fft_test.vhd

│ ├── fft_test.vho

│ ├── fft_test.xco

│ ├── fft_test_fft21_flow_control_b_1.ngc

│ ├── rami.asy

│ ├── rami.edn

│ ├── rami.sym

│ ├── rami.v

│ ├── rami.veo

│ ├── rami.vhd

│ ├── rami.vho

│ ├── rami.xco

│ ├── ramr.asy

│ ├── ramr.edn

│ ├── ramr.sym

│ ├── ramr.v

│ ├── ramr.veo

│ ├── ramr.vhd

│ ├── ramr.vho

│ ├── ramr.xco

│ └── templates

│ └── coregen.xml

├── clock_generator

│ └── clock_generator

│ ├── DCM1.xaw

│ ├── _xmsgs

│ ├── clk_generator_summary.html

│ ├── clock_generator.ise

│ ├── clock_generator.ise_ISE_Backup

│ ├── clock_generator.restore

│ ├── clock_generator.v

│ └── clock_generator_summary.html

├── data_interleaver

│ └── data_interleaver

│ ├── _xmsgs

│ ├── count24.asy

│ ├── count24.edn

│ ├── count24.sym

│ ├── count24.v

│ ├── count24.veo

│ ├── count24.vhd

│ ├── count24.vho

│ ├── count24.xco

│ ├── data_interleaver.ise

│ ├── data_interleaver.ise_ISE_Backup

│ ├── data_interleaver.restore

│ ├── data_interleaver.v

│ ├── data_interleaver_summary.html

│ ├── dint_ram.asy

│ ├── dint_ram.edn

│ ├── dint_ram.sym

│ ├── dint_ram.v

│ ├── dint_ram.veo

│ ├── dint_ram.vhd

│ ├── dint_ram.vho

│ ├── dint_ram.xco

│ ├── dint_ram2.asy

│ ├── dint_ram2.edn

│ ├── dint_ram2.mif

│ ├── dint_ram2.sym

│ ├── dint_ram2.v

│ ├── dint_ram2.veo

│ ├── dint_ram2.vhd

│ ├── dint_ram2.vho

│ ├── dint_ram2.xco

│ ├── rcount_1.asy

│ ├── rcount_1.edn

│ ├── rcount_1.sym

│ ├── rcount_1.v

│ ├── rcount_1.veo

│ ├── rcount_1.vhd

│ ├── rcount_1.vho

│ ├── rcount_1.xco

│ └── templates

│ └── coregen.xml

├── long_training

│ └── long_training

│ ├── _xmsgs

│ ├── long_generator.v

│ ├── long_generator_summary.html

│ ├── long_training.ise

│ ├── long_training.ise_ISE_Backup

│ └── long_training.restore

├── short_traning

│ └── short_training

│ ├── _xmsgs

│ ├── short_generator.v

│ ├── short_generator_summary.html

│ ├── short_training.ise

│ ├── short_training.ise_ISE_Backup

│ └── short_training.restore

└── transmit_MCU

└── transmit_MCU

├── TX_MCU_summary.html

├── _xmsgs

├── counter21.asy

├── counter21.edn

├── counter21.sym

├── counter21.v

├── counter21.veo

├── counter21.vhd

├── counter21.vho

├── counter21.xco

├── counter_30.asy

├── counter_30.edn

├── counter_30.sym

├── counter_30.v

├── counter_30.veo

├── counter_30.vhd

├── counter_30.vho

├── counter_30.xco

├── counter_80.asy

├── counter_80.edn

├── counter_80.sym

├── counter_80.v

├── counter_80.veo

├── counter_80.vhd

├── counter_80.vho

├── counter_80.xco

├── counter_data.asy

├── counter_data.edn

├── counter_data.sym

├── counter_data.v

├── counter_data.veo

├── counter_data.vhd

├── counter_data.vho

├── counter_data.xco

├── main_counter.asy

├── main_counter.edn

├── main_counter.sym

├── main_counter.v

├── main_counter.veo

├── main_counter.vhd

├── main_counter.vho

├── main_counter.xco

├── templates

│ └── coregen.xml

├── transmit_MCU.ise

├── transmit_MCU.ise_ISE_Backup

├── transmit_MCU.restore

├── transmit_MCU.v

└── transmit_MCU_summary.html

64 directories, 561 files

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论