实例介绍

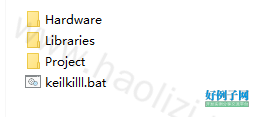

【实例截图】

【核心代码】

/**

******************************************************************************

* @file system_stm32f30x.c

* @author MCD Application Team

* @version V1.2.1

* @date 31-October-2014

* @brief CMSIS Cortex-M4 Device Peripheral Access Layer System Source File.

* This file contains the system clock configuration for STM32F30x devices,

* and is generated by the clock configuration tool

* stm32f30x_Clock_Configuration_V1.0.0.xls

*

* 1. This file provides two functions and one global variable to be called from

* user application:

* - SystemInit(): Setups the system clock (System clock source, PLL Multiplier

* and Divider factors, AHB/APBx prescalers and Flash settings),

* depending on the configuration made in the clock xls tool.

* This function is called at startup just after reset and

* before branch to main program. This call is made inside

* the "startup_stm32f30x.s" file.

*

* - SystemCoreClock variable: Contains the core clock (HCLK), it can be used

* by the user application to setup the SysTick

* timer or configure other parameters.

*

* - SystemCoreClockUpdate(): Updates the variable SystemCoreClock and must

* be called whenever the core clock is changed

* during program execution.

*

* 2. After each device reset the HSI (8 MHz) is used as system clock source.

* Then SystemInit() function is called, in "startup_stm32f30x.s" file, to

* configure the system clock before to branch to main program.

*

* 3. If the system clock source selected by user fails to startup, the SystemInit()

* function will do nothing and HSI still used as system clock source. User can

* add some code to deal with this issue inside the SetSysClock() function.

*

* 4. The default value of HSE crystal is set to 8MHz, refer to "HSE_VALUE" define

* in "stm32f30x.h" file. When HSE is used as system clock source, directly or

* through PLL, and you are using different crystal you have to adapt the HSE

* value to your own configuration.

*

* 5. This file configures the system clock as follows:

*=============================================================================

*-----------------------------------------------------------------------------

* System Clock source | PLL (HSE)

*-----------------------------------------------------------------------------

* SYSCLK(Hz) | 72000000

*-----------------------------------------------------------------------------

* HCLK(Hz) | 72000000

*-----------------------------------------------------------------------------

* AHB Prescaler | 1

*-----------------------------------------------------------------------------

* APB2 Prescaler | 1

*-----------------------------------------------------------------------------

* APB1 Prescaler | 2

*-----------------------------------------------------------------------------

* HSE Frequency(Hz) | 8000000

*----------------------------------------------------------------------------

* PLLMUL | 9

*-----------------------------------------------------------------------------

* PREDIV | 1

*-----------------------------------------------------------------------------

* USB Clock | DISABLE

*-----------------------------------------------------------------------------

* Flash Latency(WS) | 2

*-----------------------------------------------------------------------------

* Prefetch Buffer | ON

*-----------------------------------------------------------------------------

*=============================================================================

******************************************************************************

* @attention

*

* <h2><center>© COPYRIGHT 2014 STMicroelectronics</center></h2>

*

* Licensed under MCD-ST Liberty SW License Agreement V2, (the "License");

* You may not use this file except in compliance with the License.

* You may obtain a copy of the License at:

*

* http://www.st.com/software_license_agreement_liberty_v2

*

* Unless required by applicable law or agreed to in writing, software

* distributed under the License is distributed on an "AS IS" BASIS,

* WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

* See the License for the specific language governing permissions and

* limitations under the License.

*

******************************************************************************

*/

/** @addtogroup CMSIS

* @{

*/

/** @addtogroup stm32f30x_system

* @{

*/

/** @addtogroup STM32F30x_System_Private_Includes

* @{

*/

#include "stm32f30x.h"

/**

* @}

*/

/** @addtogroup STM32F30x_System_Private_TypesDefinitions

* @{

*/

/**

* @}

*/

/** @addtogroup STM32F30x_System_Private_Defines

* @{

*/

/*!< Uncomment the following line if you need to relocate your vector Table in

Internal SRAM. */

/* #define VECT_TAB_SRAM */

#define VECT_TAB_OFFSET 0x0 /*!< Vector Table base offset field.

This value must be a multiple of 0x200. */

/**

* @}

*/

/** @addtogroup STM32F30x_System_Private_Macros

* @{

*/

/**

* @}

*/

/** @addtogroup STM32F30x_System_Private_Variables

* @{

*/

uint32_t SystemCoreClock = 72000000;

__I uint8_t AHBPrescTable[16] = {0, 0, 0, 0, 0, 0, 0, 0, 1, 2, 3, 4, 6, 7, 8, 9};

/**

* @}

*/

/** @addtogroup STM32F30x_System_Private_FunctionPrototypes

* @{

*/

static void SetSysClock(void);

/**

* @}

*/

/** @addtogroup STM32F30x_System_Private_Functions

* @{

*/

/**

* @brief Setup the microcontroller system

* Initialize the Embedded Flash Interface, the PLL and update the

* SystemFrequency variable.

* @param None

* @retval None

*/

void SystemInit(void)

{

/* FPU settings ------------------------------------------------------------*/

#if (__FPU_PRESENT == 1) && (__FPU_USED == 1)

SCB->CPACR |= ((3UL << 10*2)|(3UL << 11*2)); /* set CP10 and CP11 Full Access */

#endif

/* Reset the RCC clock configuration to the default reset state ------------*/

/* Set HSION bit */

RCC->CR |= (uint32_t)0x00000001;

/* Reset CFGR register */

RCC->CFGR &= 0xF87FC00C;

/* Reset HSEON, CSSON and PLLON bits */

RCC->CR &= (uint32_t)0xFEF6FFFF;

/* Reset HSEBYP bit */

RCC->CR &= (uint32_t)0xFFFBFFFF;

/* Reset PLLSRC, PLLXTPRE, PLLMUL and USBPRE bits */

RCC->CFGR &= (uint32_t)0xFF80FFFF;

/* Reset PREDIV1[3:0] bits */

RCC->CFGR2 &= (uint32_t)0xFFFFFFF0;

/* Reset USARTSW[1:0], I2CSW and TIMs bits */

RCC->CFGR3 &= (uint32_t)0xFF00FCCC;

/* Disable all interrupts */

RCC->CIR = 0x00000000;

/* Configure the System clock source, PLL Multiplier and Divider factors,

AHB/APBx prescalers and Flash settings ----------------------------------*/

SetSysClock();

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM. */

#else

SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH. */

#endif

}

/**

* @brief Update SystemCoreClock variable according to Clock Register Values.

* The SystemCoreClock variable contains the core clock (HCLK), it can

* be used by the user application to setup the SysTick timer or configure

* other parameters.

*

* @note Each time the core clock (HCLK) changes, this function must be called

* to update SystemCoreClock variable value. Otherwise, any configuration

* based on this variable will be incorrect.

*

* @note - The system frequency computed by this function is not the real

* frequency in the chip. It is calculated based on the predefined

* constant and the selected clock source:

*

* - If SYSCLK source is HSI, SystemCoreClock will contain the HSI_VALUE(*)

*

* - If SYSCLK source is HSE, SystemCoreClock will contain the HSE_VALUE(**)

*

* - If SYSCLK source is PLL, SystemCoreClock will contain the HSE_VALUE(**)

* or HSI_VALUE(*) multiplied/divided by the PLL factors.

*

* (*) HSI_VALUE is a constant defined in stm32f30x.h file (default value

* 8 MHz) but the real value may vary depending on the variations

* in voltage and temperature.

*

* (**) HSE_VALUE is a constant defined in stm32f30x.h file (default value

* 8 MHz), user has to ensure that HSE_VALUE is same as the real

* frequency of the crystal used. Otherwise, this function may

* have wrong result.

*

* - The result of this function could be not correct when using fractional

* value for HSE crystal.

*

* @param None

* @retval None

*/

void SystemCoreClockUpdate (void)

{

uint32_t tmp = 0, pllmull = 0, pllsource = 0, prediv1factor = 0;

/* Get SYSCLK source -------------------------------------------------------*/

tmp = RCC->CFGR & RCC_CFGR_SWS;

switch (tmp)

{

case 0x00: /* HSI used as system clock */

SystemCoreClock = HSI_VALUE;

break;

case 0x04: /* HSE used as system clock */

SystemCoreClock = HSE_VALUE;

break;

case 0x08: /* PLL used as system clock */

/* Get PLL clock source and multiplication factor ----------------------*/

pllmull = RCC->CFGR & RCC_CFGR_PLLMULL;

pllsource = RCC->CFGR & RCC_CFGR_PLLSRC;

pllmull = ( pllmull >> 18) 2;

if (pllsource == 0x00)

{

/* HSI oscillator clock divided by 2 selected as PLL clock entry */

SystemCoreClock = (HSI_VALUE >> 1) * pllmull;

}

else

{

prediv1factor = (RCC->CFGR2 & RCC_CFGR2_PREDIV1) 1;

/* HSE oscillator clock selected as PREDIV1 clock entry */

SystemCoreClock = (HSE_VALUE / prediv1factor) * pllmull;

}

break;

default: /* HSI used as system clock */

SystemCoreClock = HSI_VALUE;

break;

}

/* Compute HCLK clock frequency ----------------*/

/* Get HCLK prescaler */

tmp = AHBPrescTable[((RCC->CFGR & RCC_CFGR_HPRE) >> 4)];

/* HCLK clock frequency */

SystemCoreClock >>= tmp;

}

/**

* @brief Configures the System clock source, PLL Multiplier and Divider factors,

* AHB/APBx prescalers and Flash settings

* @note This function should be called only once the RCC clock configuration

* is reset to the default reset state (done in SystemInit() function).

* @param None

* @retval None

*/

static void SetSysClock(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/* Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/* Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter ;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

/* Enable Prefetch Buffer and set Flash Latency */

FLASH->ACR = FLASH_ACR_PRFTBE | FLASH_ACR_LATENCY_1;

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

/* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_PREDIV1 | RCC_CFGR_PLLMULL9);

/* Enable PLL */

RCC->CR |= RCC_CR_PLLON;

/* Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL)

{

}

}

else

{ /* If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

}

}

/**

* @}

*/

/**

* @}

*/

/**

* @}

*/

/************************ (C) COPYRIGHT STMicroelectronics *****END OF FILE****/

标签: stm32f303

相关软件

小贴士

感谢您为本站写下的评论,您的评论对其它用户来说具有重要的参考价值,所以请认真填写。

- 类似“顶”、“沙发”之类没有营养的文字,对勤劳贡献的楼主来说是令人沮丧的反馈信息。

- 相信您也不想看到一排文字/表情墙,所以请不要反馈意义不大的重复字符,也请尽量不要纯表情的回复。

- 提问之前请再仔细看一遍楼主的说明,或许是您遗漏了。

- 请勿到处挖坑绊人、招贴广告。既占空间让人厌烦,又没人会搭理,于人于己都无利。

关于好例子网

本站旨在为广大IT学习爱好者提供一个非营利性互相学习交流分享平台。本站所有资源都可以被免费获取学习研究。本站资源来自网友分享,对搜索内容的合法性不具有预见性、识别性、控制性,仅供学习研究,请务必在下载后24小时内给予删除,不得用于其他任何用途,否则后果自负。基于互联网的特殊性,平台无法对用户传输的作品、信息、内容的权属或合法性、安全性、合规性、真实性、科学性、完整权、有效性等进行实质审查;无论平台是否已进行审查,用户均应自行承担因其传输的作品、信息、内容而可能或已经产生的侵权或权属纠纷等法律责任。本站所有资源不代表本站的观点或立场,基于网友分享,根据中国法律《信息网络传播权保护条例》第二十二与二十三条之规定,若资源存在侵权或相关问题请联系本站客服人员,点此联系我们。关于更多版权及免责申明参见 版权及免责申明

网友评论

我要评论